Motorola 88000

This article includes a list of general references, but it lacks sufficient corresponding inline citations. (September 2020) |

| Designer | Motorola |

|---|---|

| Bits | 32-bit |

| Introduced | 1988 |

| Design | RISC |

| Type | Load–store |

| Encoding | Fixed |

| Branching | Compare and branch |

| Endianness | Bi |

| Extensions | Graphics instructions (88110 only) |

| Open | No |

| Registers | |

| General-purpose | 32 32-bit |

| Floating point | 32 80-bit (88110 only) |

The 88000 (m88k for short) is a RISC instruction set architecture developed by Motorola during the 1980s. The MC88100 arrived on the market in 1988, some two years after the competing SPARC and MIPS. Due to the late start and extensive delays releasing the second-generation MC88110, the m88k achieved very limited success outside of the MVME platform and embedded controller environments. When Motorola joined the AIM alliance in 1991 to develop the PowerPC, further development of the 88000 ended.

History

[edit]Background

[edit]Motorola entered the 1980s in a position of strength; their recently-introduced Motorola 68000 easily outperformed any other microprocessor on the market, and its 32-bit architecture was naturally suited to the emerging workstation market. Intel was not moving aggressively into the 32-bit space, and the companies that did, notably National Semiconductor, botched their releases and left Motorola in control of everything that was not Intel. At the time, Intel held about 80% of the overall computer market, while Motorola controlled 90% of the rest.

Into this came the early 1980's introduction of the RISC concept. At first, there was an intense debate within the industry whether the concept would actually improve performance, or if its longer machine language programs would actually slow the execution through additional memory accesses. All such debate was ended by the mid-1980s when the first RISC-based workstations emerged; the latest Sun-3/80 running on a 20 MHz Motorola 68030 delivered about 3 MIPS, whereas the first SPARC-based Sun-4/260 with a 16 MHz SPARC delivered 10 MIPS. Hewlett-Packard, DEC and other large vendors all began moving to RISC platforms.

This shift in the market had the potential to lock Motorola out of the workstation market, one of its only strongholds and among its most lucrative. Apple remained the company's only large vendor outside the workstation space; other users of the 68000, notably Atari Corporation and Commodore International, were floundering in a market that was rapidly standardizing on IBM PC compatibles.[1]

Motorola's approach

[edit]RISC designs were a conscious effort to tailor the processor to the types of operations being called by the compilers on that platform, in the case of Unix workstations, the C programming language. The seminal IBM 801 project had noted that compilers generally did not use the vast majority of the instructions available to them, and instead used the simplest version of the instructions, often because these performed the fastest. Yet the circuitry providing the other versions of these instructions added overhead even to the simplest version. Removing these unused instructions from the CPU eliminated this overhead and freed up significant room on the chip. This gave room to increase the number of processor registers, which had a far greater impact on performance than the removed special-case instructions. For this reason, the RISC concept can be said to be driven by the real-world design of compilers.[2]

Motorola's articles on the 88000 design speak of single-cycle instructions, large processor register files and other hallmarks of the RISC concept, but don't mention the word "RISC" even once.[3] As existing RISC designs had entered the market already, the company decided that they would not attempt to compete with these and would instead produce the world's most powerful processor. To do this, they took design notes from one of the fastest computers of a previous era, the CDC 6600 supercomputer. In particular, they adopted the 6600's concept of a scoreboard. Scoreboarding allowed the CPU to examine the instruction's use of registers and immediately dispatch those that did not rely on previous calculations that were not yet complete; this allowed the instructions to be re-ordered to allow ones that had their required data to run while others had their data loaded from the cache or memory. This instruction reordering could improve usage by as much as 35%.[4]

The design also used separate data and instruction address busses. This was costly in terms of pin count; both the instruction and data caches had 32 pins for their address and 32 pins for the data, meaning the complete system used 128 pins on the "P-bus". This design was based on the observation that only about one-third of operations were memory-related; the rest were operating on data already read. This strongly favored having a dedicated instruction pathway to an external instruction cache. The caches and associated memory management units (MMU) were initially external, a cache controller could be connected to either the data or instruction busses, and up to four controllers could be used on either bus. Internally there were three 32-bit busses, connected to the internal units in different ways as required for reading and writing data to the registers.[5]

Another feature of the new design was its built-in support for specialized co-processors, or "special function units", or SFUs.[5] In addition to the internal commands supported out of the box, it set aside blocks of 256 instructions that could be used by co-processors. This was aimed at designers who wished to customize the system; new functional units could be added without affecting the existing instruction set architecture, ensuring software compatibility for the main functionality.[2] Every 88000 came with SFU1 already installed, the floating point unit (FPU).[5] The branch and jump instructions incorporate a delayed branch option (.n), which can be specified to ensure that the subsequent sequential instruction is executed before the branch target instruction, irrespective of the branch condition.[6] Placing branch instruction or other instruction which may change the instruction pointer, in the branch delay slot is deprecated to maintain future compatibility.[7]

Release

[edit]By 1987 it was widely known that Motorola was designing its own RISC processor. Referred to by the computer industry as the "78000",[a] an homage to the earlier 68000,[2] it became the 88000 when it was released in April 1988.

As a side-effect of the complexity of the design, the CPU did not fit on a single chip. The 68030, released a year earlier, had 273,000 transistors, including the arithmetic logic unit (ALU) and memory management unit (MMU) on a single chip, with the optional floating point unit (FPU) as a separate chip. In contrast, the 88000 packaged the ALU and FPU together on the 750,000 transistor MC88100, and the memory management unit (MMU) and 16 KB static RAM cache in the 750,000 transistor MC88200. In contrast to the 68030 where the FPU was truly optional, a practical 88000 system could not be built without at least one MC88200. Systems could include more than one MC88200, producing larger caches and allowing multiple paths to main memory for improved performance.[2]

Aimed at the high-end of the market, it was claimed to be the fastest 32-bit processor in the world when it was released. Running at 20 MHz, it reached 34,000 Dhrystones or 17 VUPS,[8][b] compared to about 12 MIPS for a 12.5 MHz SPARC of the same vintage in the SPARCstation, or around 3.3 MIPS of the 20 MHz 68030. It was also available as a 25 MHz part at 21 MIPS, 48,387 Dhrystones.[9]

At the time, Motorola marketed the 88000 strictly to the high-end of the market, including "telecommunications, artificial intelligence, graphics, three-dimensional animation, simulation, parallel processing and supercomputers", while they suggested the existing 68k series would continue to be used in the workstation market. Instead, most potential customers ignored the 88000,[8] and the system saw little use.

Re-release

[edit]As the original release saw next to no use outside Motorola's own products, and those traditional customers were starting to move to other RISC designs, the company re-launched the design in a single-chip form, the MC88110. In the late 1980s, several companies were actively examining the 88000 series for future use, including NeXT, Apple Computer and Apollo Computer, but all had given up on the design by the time the 88110 was finally available in 1992.

There was an attempt to popularize the system with the 88open group, similar to what Sun Microsystems was attempting with their SPARC design. It appears to have failed in any practical sense.[10]

Abandonment

[edit]In the early 1990s Motorola joined the AIM effort to create a new RISC architecture based on the IBM POWER architecture. They worked a few features of the 88000 (such as a compatible bus interface[11]) into the new PowerPC architecture to offer their customer base some sort of upgrade path. At that point the 88000 was dumped as soon as possible.[12]

Architecture

[edit]Like the 68000 before it, the 88000 was considered to be a "clean" design. It is a pure 32-bit load/store architecture with separate instruction and data caches (Harvard architecture)[13], and separate data and address buses. It has a small, powerful command set and uses a flat address space.

An unusual architectural feature is that both integer instructions and floating-point instructions use the same register file.

Implementations

[edit]

The first implementation of the 88000 ISA was the MC88100 microprocessor, which included an integrated FPU. Mated to this was the MC88200 MMU and cache controller. The idea behind this splitting of duties was to allow multiprocessor systems to be built more easily; a single MC88200 could support up to four MC88100s. However, this also meant that building the most basic system, with a single processor, required both chips and considerable wiring between them, driving up costs. This was likely to be another major reason for the 88000's limited success.

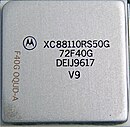

This was later addressed by the superscalar MC88110, which combined the CPU, FPU, MMU, and L1 cache into a single package. An additional modification, made at the behest of MIT's *T project, resulted in the MC88110MP, including on-chip communications for use in multi-processor systems.[14] A version capable of speeds up to 100 MHz was planned as the MC88120, but was never built.

An implementation for embedded applications, the MC88300, was under development during the early 1990s, but was eventually canceled. Ford Motor Company had planned to use the chips, which alongside adoption by telecommunications vendors had been viewed as guaranteeing the viability of the architecture indefinitely.[15] Motorola offered a PowerPC design as a replacement, which Ford accepted.[16]

Products and applications

[edit]

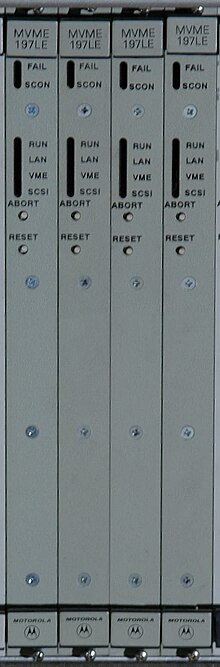

Motorola released a series of single-board computers, known as the MVME series, for building "out of the box" systems based on the 88000, as well as the Series 900 stackable computers employing these MVME boards. Unlike tower or rack mount systems, the Series 900 sat on top of each other and connected to one another with bus-like cabling. The concept never caught on.

Major 3rd party users were limited. The only widespread use would be in the Data General AViiON series. These were fairly popular, and remain in limited use today. For later models, DG moved to Intel. Encore Computer built their Encore-91 machine on the m88k, then introduced a completely ground-up redesign as the Infinity 90 series, but it is unclear how many of these machines were sold. Encore moved to the Alpha. Tektronix introduced their XD88 line of graphics workstations in April 1989.[17]

GEC Computers used the MC88100 to build the GEC 4310, one of the GEC 4000 series computers, but issues with memory management meant it didn't perform as well as their earlier gate array based and Am2900 based GEC 4000 series computers. The BBN Butterfly model TC-2000 used the MC88100 processor, and scaled to 512 CPUs. Linotype-Hell used the 88110 in their "Power" workstations running the DaVinci raster graphics editor for image manipulation.

The MC88110 made it into some versions of a never released NeXT machine, the NeXT RISC Workstation, but the project was canceled along with all NeXT hardware projects in 1993. The 4-processor OMRON LUNA-88K machines from Japan used the m88k, and were used for a short time on the Mach kernel project at Carnegie Mellon University. In the early 1990s Northern Telecom used the MC88100 and MC88110 as the central processor in its DMS SuperNode family of telephone switches.

Most other users were much smaller. Alpha Microsystems originally planned to migrate to the 88K architecture from the Motorola 68000, and internally created a machine around it running UNIX System V, but it was later scrapped in favour of later 68K derivatives.[18] NCD used the 88100 (without the 88200) in its 88K X-Terminals. Dolphin Server, a spin-off from the dying Norsk Data, built servers based on the 88k.[19] Around 100 systems were shipped during 1988-1992.

Virtuality used the MC88110 in the SU2000 virtual reality arcade machine as a graphics processor, with one MC88110 per screen of each virtual reality headset.

In the embedded computer space, the "Tri-channel VMS Computer" in the F-15 S/MTD used three 88000s in a triply redundant computer.[20]

Operating system support

[edit]Motorola released its own UNIX System V derivative, System V/88, for its 88000-based systems. There were two major releases: Release 3.2 Version 3 and Release 4.0 Version 3.[21] Data General AViiON systems ran DG/UX. OpenBSD ports exist for the MVME systems,[22] LUNA-88K workstations,[23] and Data General AViiON systems.[24] At least one unofficial experimental NetBSD port exists for the MVME systems.[25]

Notes

[edit]References

[edit]Citations

[edit]- ^ Reimer, Jeremy. "Total share: 30 years of personal computer market share figures". Ars Technica.

- ^ a b c d Lid.

- ^ Alsup 1990.

- ^ Alsup 1990, p. 51.

- ^ a b c Alsup 1990, p. 49.

- ^ "MC88100 RISC Microprocessor User's Manual" (PDF). p. 81(3-26). Retrieved 2023-12-21.

- ^ "MC88100 RISC Microprocessor User's Manual" (PDF). p. 88(3-33). Retrieved 2023-12-30.

- ^ a b April.

- ^ Volume.

- ^ Updegrove, Andrew (March 2006). "Standards Wars: Situations, Strategies and Outcomes" (PDF). ConsortiumInfo.org. p. 7. Archived from the original (PDF) on 2016-03-03. Retrieved 2009-06-16.

- ^ Cox, Steven (October 19, 2021). "CPU of the Day: Motorola XC88110 88000 RISC Processor". Retrieved 2023-08-25.

- ^ Zipper, Stuart (May 24, 1993). "Motorola PowerPC deal with Ford raises questions on 88K RISC fate". Electronic News. Retrieved 2009-06-16.[permanent dead link]

- ^ "Figure 1-2 and §1.2.7 Multiple External Buses". MC88100 RISC Microprocessor User's Manual, Second edition (PDF). 1990. Retrieved 25 August 2023.

- ^ Papadopoulos; et al. (July 28, 1993). "*T: Integrated Building Blocks for Parallel Computing" (PDF). Massachusetts Institute of Technology. Retrieved 2009-06-16.

- ^ "Ford Secures 88000 RISC Future". Unigram/X. 17 June 1991. p. 1. Retrieved 25 July 2024.

- ^ Garfinkel, Simson (June 1992). "Motorola looks to 68060 chip". NeXTWORLD.

- ^ Marshall, Martin (April 24, 1989). "Tektronix Unveils Family Of Graphics Workstations". InfoWorld.

- ^ "AMPM: The Alpha Micro Pageant of Machines". The Alpha Micro Phun Machine.

- ^ Wilson, David (July 1991). "Tested Mettle: The Dolphin Server Technology Triton 88". UNIX Review. pp. 38, 40, 43–44, 46, 48. Retrieved 24 February 2023.

- ^ Nobbs, Steven G. "PSC Implementation and Integration" (PDF). NASA. p. 63. Retrieved 2009-06-16.

- ^ Patterson, Barbara (November 2, 1991). "Motorola System V/88 R4v3.1". Motorola Computer Group. Archived from the original on May 5, 2006. Retrieved 2009-06-16.

- ^ OpenBSD/mvme88k

- ^ OpenBSD/luna88k

- ^ OpenBSD/aviion

- ^ NetBSD/m88k Archived 2013-01-12 at archive.today Unofficial port of NetBSD 3.x

Bibliography

[edit]- Alsup, Mitch (June 1990). "Motorola's 88000 Family Architecture". IEEE Micro. 10 (3): 48–66. doi:10.1109/40.56325. S2CID 30607775.

- "Lifting The Lid Off The Motorola 88000 – To Find Do-It-Yourself Co-Processors". TechMonitor. 14 September 1988.

- "Motorola's 88000 Risc In Full Volume Production". TechMonitor. 27 June 1989.[permanent dead link]

- "Motorola's Risc, Set To Go In April, Is Tailored For Unix". TechMonitor. 18 February 1988.

External links

[edit]- m88k website m68k/m88k reference website

- Dolphin m88k Dolphin Server Technology

- Badabada.org about m88k hardware and computers