Xeon

Logo since 2024 | |

| General information | |

|---|---|

| Launched | June 1998 |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturers |

|

| Performance | |

| Max. CPU clock rate | 400 MHz to 5.3 GHz |

| FSB speeds | 100 MT/s to 1.6 GT/s |

| QPI speeds | 4.8 GT/s to 24 GT/s |

| DMI speeds | 2.0 GT/s to 16 GT/s |

| Data width | Up to 64 bits |

| Address width | Up to 64 bits |

| Virtual address width | Up to 57 bits |

| Cache | |

| L1 cache | Up to 80 KB per core |

| L2 cache | Up to 2 MB per core |

| L3 cache | Up to 320 MB per socket |

| L4 cache | Up to 64 GB HBM2e[1] |

| Architecture and classification | |

| Application | |

| Technology node | 250 nm to Intel 3 and TSMC N5 |

| Microarchitecture | |

| Instruction set | x86-16, IA-32, x86-64 |

| Instructions | MMX, SSE, SSE2, SSE3, SSSE3, SSE4, SSE4.1, SSE4.2, AVX, AVX2, FMA3, AVX-512, AVX-VNNI, TSX, AES-NI, CLMUL, RDRAND |

| Extensions | |

| Physical specifications | |

| Cores |

|

| Memory (RAM) | |

| GPU | Intel Graphics Technology (some models only) |

| Co-processor | Xeon Phi (2010-2020) |

| Socket | |

| Products, models, variants | |

| Brand name | |

| Variant |

|

| History | |

| Predecessor | Pentium Pro |

| Support status | |

| Supported | |

Xeon (/ˈziːɒn/; ZEE-on) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for error correction code (ECC) memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture (MCA). They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus, which replaced the older QuickPath Interconnect (QPI) bus.

Branding[edit]

The Xeon brand has been maintained over several generations of IA-32 and x86-64 processors. The P6-based models added the Xeon moniker to the end of the name of their corresponding desktop processor, but all models since 2001 used the name Xeon on its own. The Xeon CPUs generally have more cache and cores than their desktop counterparts in addition to multiprocessing capabilities.

Xeon Scalable[edit]

The Xeon Scalable brand for high-performance server was introduced in May 2017 with the Skylake-based Xeon Platinum 8100 series. Xeon Scalable processors range from dual socket to 8 socket support. Within the Xeon Scalable brand, there exists the hierarchy of Xeon Bronze, Silver, Gold and Platinum.

(2017–2019)

(2017–2019)

(2017–2019)

(2017–2019)

(2020–2023)

(2020–2023)

(2020–2023)

(2020–2023)

In April 2024, Intel announced at its Vision event that the Xeon Scalable brand would be retired, beginning with 6th generation Xeon processors codenamed Sierra Forest and Granite Rapids that will now be referred to as "Xeon 6" processors.[4] This change brings greater emphasis on processor generation numbers.[5]

Xeon D[edit]

Xeon D is targeted towards microserver and edge computing markets with lower power consumption and integrated I/O blocks such as network interface controllers. This allows Xeon D processors to function as SoCs that do not require a separate southbridge PCH.[6] It was announced in 2014 and the first Xeon D processors were released in March 2015. Xeon D processors come in an soldered BGA package rather than in a socketable form factor. Xeon D was introduced to compete with emerging ARM hyperscale server solutions that offered greater multi-threaded performance and power effiency.[7]

Xeon W[edit]

Xeon W branding is used for Xeon workstation processors. It was first introduced in August 2017 with the release of the Skylake-based Xeon W-2100 series workstation processors. With Sapphire Rapids-WS workstation processors that launched in March 2023, Intel introduced tiers within Xeon W. Xeon w3, w5, w7 and w9 was designed to emulate the Core i3, i5, i7 and i9 branding that Intel had been using for its desktop processors.

Overview[edit]

Some shortcomings that make Xeon processors unsuitable for most consumer-grade desktop PCs include lower clock rates at the same price point (since servers run more tasks in parallel than desktops, core counts are more important than clock rates), and, usually, the lack of an integrated graphics processing unit (GPU). Processor models prior to Sapphire Rapids-WS lack support for overclocking (with the exception of Xeon W-3175X). Despite such disadvantages, Xeon processors have always had popularity among some desktop users (video editors and other power users), mainly due to higher core count potential, and higher performance to price ratio vs. the Core i7 in terms of total computing power of all cores. Since most Intel Xeon CPUs lack an integrated GPU, systems built with those processors require a discrete graphics card or a separate GPU if computer monitor output is desired.

Intel Xeon is a distinct product line from the similarly named Intel Xeon Phi. The first-generation Xeon Phi is a completely different type of device more comparable to a graphics card; it is designed for a PCI Express slot and is meant to be used as a multi-core coprocessor, like the Nvidia Tesla. In the second generation, Xeon Phi evolved into a main processor more similar to the Xeon. It conforms to the same socket as a Xeon processor and is x86-compatible; however, as compared to Xeon, the design point of the Xeon Phi emphasizes more cores with higher memory bandwidth.

| 1 or 2 Sockets UP/DP/3000/5000/E3/E5-1xxx and 2xxx/E7-2xxx/D/E/W series Bronze/Silver/Gold (non H)/Platinum (non H)/Max |

4 or 8 Sockets MP/7000/E5-4xxx/E7-4xxx and 8xxx seriesGold (H)/Platinum (H) | |||||

|---|---|---|---|---|---|---|

Node |

Code named | # of Cores |

Release date |

Code named | # of Cores |

Release date |

250 nm

|

Drake | 1 | Jun 1998 | |||

| Tanner | 1 | Mar 1999 | ||||

180 nm

|

Cascades (256 KB L2 cache) | 1 | Oct 1999 | Cascades (700 and 900 MHz models only) | 1 | May 2000 |

| Foster | 1 | May 2001 | Foster MP | 1 | Mar 2002 | |

130 nm

|

Prestonia | 1 | Feb 2002 | |||

| Gallatin DP | 1 | Jul 2003 | Gallatin | 1 | Nov 2002 | |

90 nm

|

Nocona | 1 | Jun 2004 | Cranford | 1 | Mar 2005 |

| Potomac | 1 | Mar 2005 | ||||

| Irwindale | 1 | Feb 2005 | ||||

| Paxville DP | 2 | Oct 2005 | Paxville | 2 | Nov 2005 | |

65 nm

|

Dempsey | 2 | May 2006 | Tulsa | 2 | Aug 2006 |

| Sossaman | 2 | Mar 2006 | ||||

| Woodcrest | 2 | Jun 2006 | ||||

| Conroe | 2 | Oct 2006 | ||||

| Clovertown | 4 | Nov 2006 | Tigerton/Tigerton QC | 2/4 | Sep 2007 | |

| Allendale | 2 | Jan 2007 | ||||

| Kentsfield | 4 | Jan 2007 | ||||

45 nm

|

Wolfdale DP | 2 | Nov 2007 | |||

| Harpertown | 4 | Nov 2007 | Dunnington QC/Dunnington | 4/6 | Sep 2008 | |

| Wolfdale | 2 | Feb 2008 | ||||

| Yorkfield | 4 | Mar 2008 | ||||

| Bloomfield (W35xx) | 4 | Mar 2009 | ||||

| Gainestown (55xx) | 2/4 | Mar 2009 | ||||

| Lynnfield (34xx) | 4 | Sep 2009 | ||||

| Beckton (65xx) | 4/6/8 | Mar 2010 | Beckton (75xx) | 4-8 | Mar 2010 | |

32 nm

|

Westmere-EP (56xx) | 2-6 | Mar 2010 | |||

| Gulftown (W36xx) | 6 | Mar 2010 | ||||

| Clarkdale (L34xx) | 2 | Mar 2010 | ||||

| Westmere-EX (E7-2xxx) | 6-10 | Apr 2011 | Westmere-EX (E7-4xxx/8xxx) | 6-10 | Apr 2011 | |

| Sandy Bridge-DT/EN/EP | 2-8 | Mar 2012 | Sandy Bridge-EP (E5-46xx) | 4-8 | May 2012 | |

22 nm

|

Ivy Bridge (E3/E5-1xxx/E5-2xxx v2) | 2-12 | Sep 2013 | Ivy Bridge-EP (E5-46xx v2) | 4-12 | Mar 2014 |

| Ivy Bridge-EX (E7-28xx v2) | 12/15 | Feb 2014 | Ivy Bridge-EX (E7-48xx/88xx v2) | 6-12/15 | Feb 2014 | |

| Haswell (E3/E5-1xxx/E5-2xxx v3) | 2-18 | Sep 2014 | Haswell-EP (E5-46xx v3) | 6-18 | Jun 2015 | |

| Haswell-EX (E7-48xx/88xx v3) | 4-18 | May 2015 | ||||

14 nm

|

Broadwell (E3/E5-1xxx/E5-2xxx v4) | 4-22 | Jun 2015 | |||

| Skylake-S/H (E3-1xxx v5) | 4 | Oct 2015 | ||||

| Kaby Lake-S/H (E3-1xxx v6) | 4 | Mar 2017 | ||||

| Skylake-W/SP (Bronze and Silver) | 4-28 | Jun 2017 | Skylake-SP (Gold and Platinum) | 4-28 | Jul 2017 | |

| Cascade Lake-W/SP (Bronze/Silver/R/U) | 4-28 | Apr 2019 | Cascade Lake-SP (Gold (non-R/U)/Platinum) | 4-28 | Apr 2019 | |

| Cooper Lake-SP | 8-28 | Jun 2020 | ||||

10 nm

|

Ice Lake-SP/W | 8-40 | Apr 2021 | |||

| Ice Lake-D | 2-20 | Feb 2022 | ||||

Intel 7 |

Sapphire Rapids-SP/WS/HBM | 6-56 | Jan 2023 | Sapphire Rapids-SP | 8-60 | Jan 2023 |

| Emerald Rapids-SP | 8-64 | Dec 2023 | ||||

| List of Intel Xeon processors | ||||||

P6-based Xeon[edit]

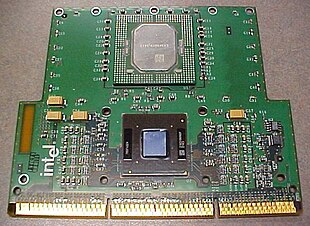

Pentium II Xeon[edit]

The first Xeon-branded processor was the Pentium II Xeon (code-named "Drake"). It was released in 1998, replacing the Pentium Pro in Intel's high-end server lineup. The Pentium II Xeon was a "Deschutes" Pentium II (and shared the same product code: 80523) with a full-speed 512 kB (1 kB = 1024 B), 1 MB (1 MB = 1024 kB = 10242 B), or 2 MB L2 cache. The L2 cache was implemented with custom 512 kB SRAMs developed by Intel. The number of SRAMs depended on the amount of cache. A 512 kB configuration required one SRAM, a 1 MB configuration: two SRAMs, and a 2 MB configuration: four SRAMs on both sides of the PCB. Each SRAM was a 12.90 mm by 17.23 mm (222.21 mm2) die fabricated in a 0.35 μm four-layer metal CMOS process and packaged in a cavity-down wire-bonded land grid array (LGA).[8] The additional cache required a larger module and thus the Pentium II Xeon used a larger slot, Slot 2. It was supported by the i440GX dual-processor workstation chipset and the i450NX quad- or octo-processor server chipset.

Pentium III Xeon[edit]

In 1999, the Pentium II Xeon was replaced by the Pentium III Xeon. Reflecting the incremental changes from the Pentium II "Deschutes" core to the Pentium III "Katmai" core, the first Pentium III Xeon, named "Tanner", was just like its predecessor except for the addition of Streaming SIMD Extensions (SSE) and a few cache controller improvements. The product codes for Tanner mirrored that of Katmai; 80525.

The second version, named "Cascades", was based on the Pentium III "Coppermine" core. The "Cascades" Xeon used a 133 MT/s front side bus and relatively small 256 kB on-die L2 cache resulting in almost the same capabilities as the Slot 1 Coppermine processors, which were capable of dual-processor operation but not quad-processor or octa-processor operation.

To improve this situation, Intel released another version, officially also named "Cascades", but often referred to as "Cascades 2 MB". That came in two variants: with 1 MB or 2 MB of L2 cache. Its bus speed was fixed at 100 MT/s, though in practice the cache was able to offset this. The product code for Cascades mirrored that of Coppermine; 80526.

NetBurst-based Xeon [edit]

Xeon (DP) and Xeon MP (32-bit)[edit]

Foster[edit]

In mid-2001, the Xeon brand was introduced ("Pentium" was dropped from the name). The initial variant that used the new NetBurst microarchitecture, "Foster", was slightly different from the desktop Pentium 4 ("Willamette"). It was a decent[clarification needed] chip for workstations, but for server applications it was almost always outperformed by the older Cascades cores with a 2 MB L2 cache and AMD's Athlon MP[example needed]. Combined with the need to use expensive Rambus Dynamic RAM, the Foster's sales were somewhat unimpressive[example needed].

At most two Foster processors could be accommodated in a symmetric multiprocessing (SMP) system built with a mainstream chipset, so a second version (Foster MP) was introduced with 512 KB or 1 MB L3 cache and the Jackson Hyper-Threading capacity. This improved performance slightly, but not enough to lift it out of third place. It was also priced much higher than the dual-processor (DP) versions. The Foster shared the 80528 product code with Willamette.

Prestonia[edit]

In 2002 Intel released a 130 nm version of Xeon branded CPU, codenamed "Prestonia". It supported Intel's new Hyper-Threading technology and had a 512 kB L2 cache. This was based on the "Northwood" Pentium 4 core. A new server chipset, E7500 (which allowed the use of dual-channel DDR SDRAM), was released to support this processor in servers, and soon the bus speed was boosted to 533 MT/s (accompanied by a new socket and two new chipsets: the E7501 for servers and the E7505 for workstations). The Prestonia performed much better than its predecessor and noticeably better than Athlon MP. The support of new features in the E75xx series also gave it a key advantage over the Pentium III Xeon and Athlon MP branded CPUs (both stuck with rather old chipsets), and it quickly became the top-selling server/workstation processor.

Gallatin[edit]

| |

| General information | |

|---|---|

| Launched | March 2003 |

| Discontinued | 2004 |

| CPUID code | 0F7x |

| Product code | 80537 |

| Performance | |

| Max. CPU clock rate | 1.50 GHz to 3.20 GHz |

| FSB speeds | 400 MT/s to 533 MT/s |

| Cache | |

| L1 cache | 8 kB + 12 kuOps trace cache |

| L2 cache | 512 kB |

| L3 cache | 1 MB, 2 MB, 4 MB |

| Architecture and classification | |

| Application | DP and MP Server |

| Technology node | 130 nm |

| Microarchitecture | NetBurst |

| Instruction set | x86-16, IA-32 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

Subsequent to the Prestonia was the "Gallatin", which had an L3 cache of 1 MB or 2 MB. Its Xeon MP version, which succeeded Foster MP, was popular in servers. Later experience with the 130 nm process allowed Intel to create the Xeon MP branded Gallatin with 4 MB cache. The Xeon branded Prestonia and Gallatin were designated 80532, like Northwood.

Xeon (DP) and Xeon MP (64-bit)[edit]

Nocona and Irwindale[edit]

Due to a lack of success with Intel's Itanium and Itanium 2 processors, AMD was able to introduce x86-64, a 64-bit extension to the x86 architecture. Intel followed suit by including Intel 64 (formerly EM64T; it is almost identical to AMD64) in the 90 nm version of the Pentium 4 ("Prescott"), and a Xeon version codenamed "Nocona" with 1 MB L2 cache was released in 2004. Released with it were the E7525 (workstation), E7520 and E7320 (both server) chipsets, which added support for PCI Express 1.0a, DDR2 and Serial ATA 1.0a. The Xeon was noticeably slower than AMD's Opteron, although it could be faster in situations where Hyper-Threading came into play.

A slightly updated core called "Irwindale" was released in early 2005, with 2 MB L2 cache and the ability to have its clock speed reduced during low processor demand. Although it was a bit more competitive than the Nocona had been, independent tests showed that AMD's Opteron still outperformed Irwindale. Both of these Prescott-derived Xeons have the product code 80546.

Cranford and Potomac[edit]

64-bit Xeon MPs were introduced in April 2005. The cheaper "Cranford" was an MP version of Nocona, while the more expensive "Potomac" was a Cranford with 8 MB of L3 cache. Like Nocona and Irwindale, they also have product code 80546.

Dual-Core Xeon[edit]

"Paxville DP"[edit]

| General information | |

|---|---|

| Launched | October 2005 |

| Discontinued | August 2008 |

| CPUID code | 0F48 |

| Product code | 80551, 80560 |

| Performance | |

| Max. CPU clock rate | 2.667 GHz to 3.0 GHz |

| FSB speeds | 667 MT/s to 800 MT/s |

| Cache | |

| L2 cache | 2×2 MB |

| Architecture and classification | |

| Application | DP Server, MP Server |

| Technology node | 90 nm |

| Microarchitecture | NetBurst |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

The first dual-core CPU branded Xeon, codenamed Paxville DP, product code 80551, was released by Intel on October 10, 2005. Paxville DP had NetBurst microarchitecture, and was a dual-core equivalent of the single-core Irwindale (related to the Pentium D branded "Smithfield") with 4 MB of L2 cache (2 MB per core). The only Paxville DP model released ran at 2.8 GHz, featured an 800 MT/s front side bus, and was produced using a 90 nm process.

7000-series "Paxville MP"[edit]

An MP-capable version of Paxville, codenamed Paxville MP, product code 80560, was released on November 1, 2005. There are two versions: one with 2 MB of L2 cache (1 MB per core), and one with 4 MB of L2 (2 MB per core). Paxville MP, called the dual-core Xeon 7000-series, was produced using a 90 nm process. Paxville MP clock ranges between 2.67 GHz and 3.0 GHz (model numbers 7020–7041), with some models having a 667 MT/s FSB, and others having an 800 MT/s FSB.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| 7020 | 2.66 GHz | 2 × 1 MB | 667 MT/s | 165 W |

| 7030 | 2.80 GHz | 800 MT/s | ||

| 7040 | 3.00 GHz | 2 × 2 MB | 667 MT/s | |

| 7041 | 800 MT/s |

7100-series "Tulsa"[edit]

| General information | |

|---|---|

| Launched | August 2006 |

| Discontinued | August 2008 |

| CPUID code | 0F68 |

| Product code | 80550 |

| Performance | |

| Max. CPU clock rate | 2.50 GHz to 3.50 GHz |

| FSB speeds | 667 MT/s to 800 MT/s |

| Cache | |

| L2 cache | 2×1 MB |

| L3 cache | 16 MB |

| Architecture and classification | |

| Application | MP Server |

| Technology node | 65 nm |

| Microarchitecture | NetBurst |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

Released on August 29, 2006,[9] the 7100 series, codenamed Tulsa (product code 80550), is an improved version of Paxville MP, built on a 65 nm process, with 2 MB of L2 cache (1 MB per core) and up to 16 MB of L3 cache. It uses Socket 604.[10] Tulsa was released in two lines: the N-line uses a 667 MT/s FSB, and the M-line uses an 800 MT/s FSB. The N-line ranges from 2.5 GHz to 3.5 GHz (model numbers 7110N-7150N), and the M-line ranges from 2.6 GHz to 3.4 GHz (model numbers 7110M-7140M). L3 cache ranges from 4 MB to 16 MB across the models.[11]

| Model | Speed | L2 cache | L3 cache | FSB | TDP |

|---|---|---|---|---|---|

| 7110N | 2.50 GHz | 2 MB | 4 MB | 667 MT/s | 95 W |

| 7110M | 2.60 GHz | 800 MT/s | |||

| 7120N | 3.00 GHz | 667 MT/s | |||

| 7120M | 800 MT/s | ||||

| 7130N | 3.16 GHz | 8 MB | 667 MT/s | 150 W | |

| 7130M | 3.20 GHz | 800 MT/s | |||

| 7140N | 3.33 GHz | 16 MB | 667 MT/s | ||

| 7140M | 3.40 GHz | 800 MT/s | |||

| 7150N | 3.50 GHz | 667 MT/s |

5000-series "Dempsey"[edit]

| General information | |

|---|---|

| Launched | May 2006 |

| Discontinued | August 2008 |

| Performance | |

| Max. CPU clock rate | 2.50 GHz to 3.73 GHz |

| FSB speeds | 667 MT/s to 1066 MT/s |

| Cache | |

| L2 cache | 4 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 65nm |

| Microarchitecture | NetBurst |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

On May 23, 2006, Intel released the dual-core CPU (Xeon branded 5000 series) codenamed Dempsey (product code 80555). Released as the Dual-Core Xeon 5000-series, Dempsey is a NetBurst microarchitecture processor produced using a 65 nm process, and is virtually identical to Intel's "Presler" Pentium Extreme Edition, except for the addition of SMP support, which lets Dempsey operate in dual-processor systems. Dempsey ranges between 2.50 GHz and 3.73 GHz (model numbers 5020–5080). Some models have a 667 MT/s FSB, and others have a 1066 MT/s FSB. Dempsey has 4 MB of L2 cache (2 MB per core). A Medium Voltage model, at 3.2 GHz and 1066 MT/s FSB (model number 5063), has also been released. Dempsey also introduces a new interface for Xeon processors: LGA 771, also known as Socket J. Dempsey was the first Xeon core in a long time to be somewhat competitive with its Opteron-based counterparts, although it could not claim a decisive lead in any performance metric – that would have to wait for its successor, the Woodcrest.

| Model | Speed (GHz) | L2 cache | FSB | TDP |

|---|---|---|---|---|

| 5020 | 2.50 GHz | 2 × 2 MB | 667 MT/s | 95 W |

| 5030 | 2.66 GHz | |||

| 5040 | 2.83 GHz | |||

| 5050 | 3.00 GHz | |||

| 5060 | 3.20 GHz | 1.07 GT/s | 130 W | |

| 5063 | 95 W | |||

| 5070 | 3.46 GHz | 130 W | ||

| 5080 | 3.73 GHz |

Pentium M (Yonah) based Xeon[edit]

LV (ULV), "Sossaman"[edit]

| |

| General information | |

|---|---|

| Launched | 2006 |

| Discontinued | 2008 |

| CPUID code | 06Ex |

| Product code | 80539 |

| Performance | |

| Max. CPU clock rate | 1.667 GHz to 2.167 GHz |

| FSB speeds | 667 MT/s |

| Cache | |

| L2 cache | 2 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 65 nm |

| Microarchitecture | Enhanced Pentium M |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

On March 14, 2006, Intel released a dual-core processor codenamed Sossaman and branded as Xeon LV (low-voltage). Subsequently, an ULV (ultra-low-voltage) version was released. The Sossaman was a low-/ultra-low-power and double-processor capable CPU (like AMD Quad FX), based on the "Yonah" processor, for ultradense non-consumer environment (i.e., targeted at the blade-server and embedded markets), and was rated at a thermal design power (TDP) of 31 W (LV: 1.66 GHz, 2 GHz and 2.16 GHz) and 15 W (ULV: 1.66 GHz).[12] As such, it supported most of the same features as earlier Xeons: Virtualization Technology, 667 MT/s front side bus, and dual-core processing, but did not support 64-bit operations, so it could not run 64-bit server software, such as Microsoft Exchange Server 2007, and therefore was limited to 16 GB of memory. A planned successor, codenamed "Merom MP" was to be a drop-in upgrade to enable Sossaman-based servers to upgrade to 64-bit capability. However, this was abandoned in favor of low-voltage versions of the Woodcrest LV processor leaving the Sossaman at a dead-end with no upgrade path.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| ULV 1.66 | 1.66 GHz | 2 MB | 667 MT/s | 15 W |

| LV 1.66 | 31 W | |||

| LV 2.00 | 2.00 GHz | |||

| LV 2.16 | 2.16 GHz |

Core-based Xeon[edit]

Dual-Core[edit]

3000-series "Conroe"[edit]

The 3000 series, codenamed Conroe (product code 80557) dual-core Xeon (branded) CPU,[13] released at the end of September 2006, was the first Xeon for single-CPU operation and is designd for entry-level uniprocessor servers. The same processor is branded as Core 2 Duo or as Pentium Dual-Core and Celeron, with varying features disabled. They use LGA 775 (Socket T), operate on a 1066 MT/s front-side bus, support Enhanced Intel SpeedStep Technology and Intel Virtualization Technology but do not support hyper-threading. Conroe processors with a number ending in "5" have a 1333 MT/s FSB.[14]

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| 3040 | 1.86 GHz | 2 MB | 1066 MT/s | 65 W |

| 3050 | 2.13 GHz | |||

| 3055* | 4 MB | |||

| 3060 | 2.4 GHz | |||

| 3065 | 2.33 GHz | 1333 MT/s | ||

| 3070 | 2.66 GHz | 1066 MT/s | ||

| 3075 | 1333 MT/s | |||

| 3080* | 2.93 GHz | 1066 MT/s | ||

| 3085 | 3.00 GHz | 1333 MT/s |

- Models marked with an asterisk (*) are not present in Intel's Ark database.[15]

3100-series "Wolfdale"[edit]

The 3100 series, codenamed Wolfdale (product code 80570) dual-core Xeon (branded) CPU, was just a rebranded version of the Intel's mainstream Core 2 Duo E7000/E8000 and Pentium Dual-Core E5000 processors, featuring the same 45 nm process and 6 MB of L2 cache. Unlike most Xeon processors, they only support single-CPU operation. They use LGA 775 (Socket T), operate on a 1333 MT/s front-side bus, support Enhanced Intel SpeedStep Technology and Intel Virtualization Technology but do not support Hyper-Threading.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E3110 | 3.00 GHz | 6 MB | 1333 MT/s | 65 W |

| L3110 | 45 W | |||

| E3120 | 3.16 GHz | 65 W |

5100-series "Woodcrest"[edit]

| |

| General information | |

|---|---|

| Launched | 2006 |

| Discontinued | 2009 |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer | |

| CPUID code | 06Fx |

| Product code | 80556 |

| Performance | |

| Max. CPU clock rate | 1.60 GHz to 3.0 GHz |

| FSB speeds | 1066 MT/s to 1333 MT/s |

| Cache | |

| L1 cache | 128 KB (64 KB (32 KB instruction + 32 KB data) x 2) |

| L2 cache | 4 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 65nm |

| Microarchitecture | Core/Merom |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Socket | |

| Products, models, variants | |

| Brand name |

|

| Variants |

|

| History | |

| Predecessor | Dempsey |

| Successor | Wolfdale-DP |

On June 26, 2006, Intel released the dual-core CPU (Xeon branded 5100 series) codenamed Woodcrest (product code 80556); it was the first Intel Core/Merom microarchitecture processor to be launched on the market. It is a dual-processor server and workstation version of the Core 2 processor. Intel claimed that it provides an 80% boost in performance, while reducing power consumption by 20% relative to the 5000 series Dempsey.

Most models have a 1333 MT/s FSB, except for the 5110 and 5120, which have a 1066 MT/s FSB. The fastest processor (5160) operates at 3.0 GHz. All Woodcrest processors use the LGA 771 (Socket J) socket and all except two models have a TDP of 65 W. The 5160 has a TDP of 80 W and the 5148LV (2.33 GHz) has a TDP of 40 W. The previous generation Xeons had a TDP of 130 W. All models support Intel 64 (Intel's x86-64 implementation), the XD bit, and Virtualization Technology, with the Demand-based switching power management option only on Dual-Core Xeon 5140 or above. Woodcrest has 4 MB of shared L2 cache.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| 5110 | 1.60 GHz | 4 MB | 1066 MT/s | 65 W |

| 5120 | 1.83 GHz | |||

| 5128 | 40 W | |||

| 5130 | 2.0 GHz | 1333 MT/s | 65 W | |

| 5138 | 2.13 GHz | 1066 MT/s | 35 W | |

| 5140 | 2.33 GHz | 1333 MT/s | 65 W | |

| 5148 | 40 W | |||

| 5150 | 2.66 GHz | 65 W | ||

| 5160 | 3.00 GHz | 80 W |

5200-series "Wolfdale-DP"[edit]

| General information | |

|---|---|

| Launched | 2007 |

| Discontinued | present |

| CPUID code | 1067x |

| Product code | 80573 |

| Performance | |

| Max. CPU clock rate | 1.866 GHz to 3.50 GHz |

| FSB speeds | 1066 MT/s to 1600 MT/s |

| Cache | |

| L2 cache | 6 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 45 nm |

| Microarchitecture | Penryn |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

On November 11, 2007, Intel released the dual-core CPU (Xeon branded 5200 series) codenamed Wolfdale-DP (product code 80573).[16] It is built on a 45 nm process like the desktop Core 2 Duo and Xeon Wolfdale, featuring Intel 64 (Intel's x86-64 implementation), the XD bit, and Virtualization Technology. It is unclear whether the Demand-based switching power management is available on the L5238.[17] Wolfdale has 6 MB of shared L2 cache.

| Model | Speed (GHz) | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E5205 | 1.86 GHz | 6 MB | 1066 MT/s | 65 W |

| L5238 | 2.66 GHz | 1333 MT/s | 35 W | |

| L5240 | 3.00 GHz | 40 W | ||

| X5260 | 3.33 GHz | 80 W | ||

| X5270 | 3.50 GHz | |||

| X5272 | 3.40 GHz | 1600 MT/s |

7200-series "Tigerton"[edit]

The 7200 series, codenamed Tigerton (product code 80564) is an MP-capable processor, similar to the 7300 series, but, in contrast, there is a single dual-core die.[18][19][20][21]

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E7210 | 2.40 GHz | 4 MB | 1066 MT/s | 80 W |

| E7220 | 2.93 GHz |

Quad-Core and Six-Core Xeon[edit]

3200-series "Kentsfield "[edit]

Intel released rebranded versions of its quad-core (2×2) Core 2 Quad processor as the Xeon 3200-series (product code 80562) on January 7, 2007.[22] The 2 × 2 "quad-core" (dual-die dual-core[23]) comprised two separate dual-core die next to each other in one CPU package. The models are the X3210, X3220 and X3230, running at 2.13 GHz, 2.4 GHz and 2.66 GHz, respectively.[24] Like the 3000-series, these models only support single-CPU operation and operate on a 1066 MT/s front-side bus. It is targeted at the "blade" market. The X3220 is also branded and sold as Core2 Quad Q6600, the X3230 as Q6700.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| X3210 | 2.13 GHz | 4 MB × 2 | 1066 MT/s | 100/105 W |

| X3220 | 2.40 GHz | |||

| X3230 | 2.66 GHz | 100 W |

3300-series "Yorkfield"[edit]

Intel released relabeled versions of its quad-core Core 2 Quad Yorkfield Q9300, Q9400, Q9x50 and QX9770 processors as the Xeon 3300-series (product code 80569). This processor comprises two separate dual-core dies next to each other in one CPU package and manufactured in a 45 nm process. The models are the X3320, X3330, X3350, X3360, X3370 and X3380, being rebadged Q9300, Q9400, Q9450, Q9550, Q9650, QX9770, running at 2.50 GHz, 2.66 GHz, 2.66 GHz, 2.83 GHz, 3.0 GHz, and 3.16 GHz, respectively. The L2 cache is a unified 6 MB per die (except for the X3320 and X3330 with a smaller 3 MB L2 cache per die), and a front-side bus of 1333 MHz. All models feature Intel 64 (Intel's x86-64 implementation), the XD bit, and Virtualization Technology, as well as Demand-based switching.

The Yorkfield-CL (product code 80584) variant of these processors are X3323, X3353 and X3363. They have a reduced TDP of 80W and are made for single-CPU LGA 771 systems instead of LGA 775, which is used in all other Yorkfield processors. In all other respects, they are identical to their Yorkfield counterparts.

5300-series "Clovertown"[edit]

| |

| General information | |

|---|---|

| Launched | 2006 |

| Discontinued | present |

| CPUID code | 06Fx |

| Product code | 80563 |

| Performance | |

| Max. CPU clock rate | 1.60 GHz to 3.0 GHz |

| FSB speeds | 1066 MT/s to 1333 |

| Cache | |

| L2 cache | 2×4 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 65 nm |

| Microarchitecture | Core |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

A quad-core (2×2) successor of the Woodcrest for DP segment, consisting of two dual-core Woodcrest chips in one package similarly to the dual-core Pentium D branded CPUs (two single-core chips) or the quad-core Kentsfield. All Clovertowns use the LGA 771 package. The Clovertown has been usually implemented with two Woodcrest dies on a multi-chip module, with 8 MB of L2 cache (4 MB per die). Like Woodcrest, lower models use a 1066 MT/s FSB, and higher models use a 1333 MT/s FSB. Intel released Clovertown, product code 80563, on November 14, 2006[25] with models E5310, E5320, E5335, E5345, and X5355, ranging from 1.6 GHz to 2.66 GHz. All models support: MMX, SSE, SSE2, SSE3, SSSE3, Intel 64, XD bit (an NX bit implementation), Intel VT. The E and X designations are borrowed from Intel's Core 2 model numbering scheme; an ending of -0 implies a 1066 MT/s FSB, and an ending of -5 implies a 1333 MT/s FSB.[24] All models have a TDP of 80 W with the exception of the X5355, which has a TDP of 120 W, and the X5365, which has a TDP of 150 W. A low-voltage version of Clovertown with a TDP of 50 W has a model numbers L5310, L5320 and L5335 (1.6 GHz, 1.86 GHz and 2.0 GHz respectively). The 3.0 GHz X5365 arrived in July 2007, and became available in the Apple Mac Pro[26] on April 4, 2007.[27][28] The X5365 performs up to around 38 GFLOPS in the LINPACK benchmark.[29]

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E5310 | 1.60 GHz | 4 MB × 2 | 1066 MT/s | 80 W |

| L5310 | 50 W | |||

| E5320 | 1.86 GHz | 80 W | ||

| L5320 | 50 W | |||

| E5335 | 2.00 GHz | 1333 MT/s | 80 W | |

| L5335 | 50 W | |||

| E5345 | 2.33 GHz | 80 W | ||

| X5355 | 2.66 GHz | 120 W | ||

| X5365 | 3.00 GHz | 150 W |

5400-series "Harpertown"[edit]

| General information | |

|---|---|

| Launched | 2007 |

| Discontinued | present |

| CPUID code | 1067x |

| Product code | 80574 |

| Performance | |

| Max. CPU clock rate | 2.0 GHz to 3.40 GHz |

| FSB speeds | 1066 MT/s to 1600 |

| Cache | |

| L2 cache | 2 × 6 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 45 nm |

| Microarchitecture | Penryn |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand names |

|

On November 11, 2007 Intel presented Yorkfield-based Xeons – called Harpertown (product code 80574) – to the public.[30] This family consists of dual die quad-core CPUs manufactured on a 45 nm process and featuring 1066 MHz, 1333 MHz, 1600 MHz front-side buses, with TDP rated from 40 W to 150 W depending on the model. These processors fit in the LGA 771 package. All models feature Intel 64 (Intel's x86-64 implementation), the XD bit, and Virtualization Technology. All except the E5405 and L5408 also feature Demand-based switching. The supplementary character in front of the model-number represents the thermal rating: an L depicts a TDP of 40 W or 50 W, an E depicts 80 W whereas an X is 120 W TDP or above. The speed of 3.00 GHz comes as four models, two models with 80 W TDP two other models with 120 W TDP with 1333 MHz or 1600 MHz front-side bus respectively. The fastest Harpertown is the X5492 whose TDP of 150 W is higher than those of the Prescott-based Xeon DP but having twice as many cores. (The X5482 is also sold under the name "Core 2 Extreme QX9775" for use in the Intel Skulltrail system.)

Intel 1.6 GT/s front-side bus Xeon processors will drop into the Intel 5400 (Seaburg) chipset whereas several mainboards featuring the Intel 5000/5200-chipset are enabled to run the processors with a 1333 MHz front-side bus speed. Seaburg features support for dual PCIe 2.0 x16 slots and up to 128 GB of memory.[31][32]

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E5405 | 2.00 GHz | 2 × 6 MB | 1333 MT/s | 80 W |

| L5408 | 2.13 GHz | 1066 MT/s | 40 W | |

| E5410 | 2.33 GHz | 1333 MT/s | 80 W | |

| L5410 | 50 W | |||

| E5420 | 2.50 GHz | 80 W | ||

| L5420 | 50 W | |||

| E5430 | 2.66 GHz | 80 W | ||

| L5430 | 50 W | |||

| E5440 | 2.83 GHz | 80 W | ||

| X5450 | 3.00 GHz | 120 W | ||

| E5450 | 80 W | |||

| X5460 | 3.16 GHz | 120 W | ||

| X5470 | 3.33 GHz | |||

| E5462 | 2.80 GHz | 1600 MT/s | 80 W | |

| E5472 | 3.00 GHz | |||

| X5472 | 120 W | |||

| X5482 | 3.20 GHz | 150 W | ||

| X5492 | 3.40 GHz |

7300-series "Tigerton QC"[edit]

| General information | |

|---|---|

| Launched | 2007 |

| Discontinued | present |

| CPUID code | 06Fx |

| Product code | 80564 80565 |

| Performance | |

| Max. CPU clock rate | 1.60 GHz to 2.933 GHz |

| FSB speeds | 1066 MT/s |

| Cache | |

| L2 cache | 2×2 or 2×4 MB |

| Architecture and classification | |

| Application | MP Server |

| Technology node | 65 nm |

| Microarchitecture | Core |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand names |

|

The 7300 series, codenamed Tigerton QC (product code 80565) is a four-socket (packaged in Socket 604) and more capable quad-core processor, consisting of two dual core Core 2 architecture silicon chips on a single ceramic module, similar to Intel's Xeon 5300 series Clovertown processor modules.[33]

The 7300 series uses Intel's Caneland (Clarksboro) platform.

Intel claims the 7300 series Xeons offer more than twice the performance per watt as Intel's previous generation 7100 series. The 7300 series' Caneland chipset provides a point to point interface allowing the full front side bus bandwidth per processor.

The 7xxx series is aimed at the large server market, supporting configurations of up to 32 CPUs per host.

| Model | Speed | L2 cache | FSB | TDP |

|---|---|---|---|---|

| E7310 | 1.60 GHz | 2×2 MB | 1066 MT/s | 80 W |

| E7320 | 2.13 GHz | |||

| E7330 | 2.40 GHz | 2×3 MB | ||

| E7340 | 2×4 MB | |||

| L7345 | 1.86 GHz | 50 W | ||

| X7350 | 2.93 GHz | 130 W |

7400-series "Dunnington"[edit]

| General information | |

|---|---|

| Launched | 2008 |

| Discontinued | present |

| CPUID code | 106D1 |

| Product code | 80582 |

| Performance | |

| Max. CPU clock rate | 2.133 GHz to 2.66 GHz |

| FSB speeds | 1066 MT/s |

| Cache | |

| L1 cache | 6 × 96 KB |

| L2 cache | 3 × 3 MB |

| L3 cache | 16 MB |

| Architecture and classification | |

| Application | MP Server |

| Technology node | 45 nm |

| Microarchitecture | Penryn |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

Dunnington[34] – the last CPU of the Penryn generation and Intel's first multi-core (above two) die – features a single-die six- (or hexa-) core design with three unified 3 MB L2 caches (resembling three merged 45 nm dual-core Wolfdale-3M dies), and 96 kB L1 cache (Data) and 16 MB of L3 cache. It features a 1.07 GT/s FSB, fits into the Tigerton's mPGA604 socket, and is compatible with both the Intel Caneland and IBM X4 chipsets. These processors support DDR2-1066 (533 MHz), and have a maximum TDP below 130 W. They are intended for blades and other stacked computer systems. Availability was scheduled for the second half of 2008. It was followed shortly by the Nehalem microarchitecture. Total transistor count is 1.9 billion.[35]

Announced on September 15, 2008.[36]

| Model | Speed | L3 cache | FSB | TDP | Cores |

|---|---|---|---|---|---|

| E7420 | 2.13 GHz | 8 MB | 1066 MT/s | 90 W | 4 |

| E7430 | 12 MB | ||||

| E7440 | 2.40 GHz | 16 MB | |||

| L7445 | 2.13 GHz | 12 MB | 50 W | ||

| E7450 | 2.40 GHz | 90 W | 6 | ||

| L7455 | 2.13 GHz | 65 W | |||

| X7460 | 2.66 GHz | 16 MB | 130 W |

Nehalem-based Xeon[edit]

3400-series "Lynnfield"[edit]

Xeon 3400-series processors based on Lynnfield are designed for entry-level servers compared to Bloomfield, which is designed for uniprocessor workstations. Like Bloomfield, they are quad-core single-package processors based on the Nehalem microarchitecture, but were introduced almost a year later, in September 2009. The same processors are marketed for mid-range to high-end desktops systems as Core i5 and Core i7. They have two integrated memory channels as well as PCI Express and Direct Media Interface (DMI) links, but no QuickPath Interconnect (QPI) interface.

3400-series "Clarkdale"[edit]

At low end of the 3400-series is not a Lynnfield but a Clarkdale processor, which is also used in the Core i3-500 and Core i5-600 processors as well as the Celeron G1000 and G6000 Pentium series. A single model was released in March 2010, the Xeon L3406. Compared to all other Clarkdale-based products, this one does not support integrated graphics, but has a much lower thermal design power of just 30 W. Compared to the Lynnfield-based Xeon 3400 models, it only offers two cores.

W3500-series "Bloomfield"[edit]

Bloomfield (or Nehalem-E) is the codename for the successor to the Xeon 3300 series, is based on the Nehalem microarchitecture and uses the same 45 nm manufacturing methods as Intel's Penryn. The first processor released with the Nehalem architecture is the high-end desktop Core i7, which was released in November 2008. This is the server version for single CPU systems. This is a single-socket Intel Xeon processor designed for uniprocessor workstations.

The performance improvements over the previous Xeon 3300 series are based mainly on:

- Integrated memory controller supporting three memory channels of DDR3 UDIMM (Unbuffered) or RDIMM (Registered)

- A new point-to-point processor interconnect QuickPath, replacing the legacy front side bus

- Simultaneous multithreading by multiple cores and hyper-threading (2× per core).

- Turbo Boost, an overclocking technology that allows the CPU to run at a clock speed higher than the base speed as needed

| Model | Speed | L3 cache | QPI speed | DDR3 speed | TDP | Cores | Threads | Turbo-Boost |

|---|---|---|---|---|---|---|---|---|

| W3503 | 2.40 GHz | 4 MB | 4.8 GT/s | 1066 MT/s | 130 W | 2 | No | |

| W3505 | 2.53 GHz | |||||||

| W3520 | 2.66 GHz | 8 MB | 4 | 8 | Yes | |||

| W3530 | 2.80 GHz | |||||||

| W3540 | 2.93 GHz | |||||||

| W3550 | 3.06 GHz | |||||||

| W3565 | 3.20 GHz | |||||||

| W3570 | 3.2 GHz | 6.4 GT/s | 1333 MT/s | |||||

| W3580 | 3.33 GHz | |||||||

5500-series "Gainestown"[edit]

| General information | |

|---|---|

| Launched | 2008 |

| Discontinued | present |

| CPUID code | 106Ax |

| Product code | 80602 |

| Performance | |

| Max. CPU clock rate | 1.866 GHz to 3.333 GHz |

| Cache | |

| L2 cache | 4×256 kB |

| L3 cache | 8 MB |

| Architecture and classification | |

| Application | DP Server |

| Technology node | 45 nm |

| Microarchitecture | Nehalem |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand name |

|

Gainestown or Nehalem-EP (Efficient Performance), the successor to Wolfdale-DP, and Harpertown, is based on the Nehalem microarchitecture and uses the same 45 nm manufacturing methods. The first processor released with the Nehalem microarchitecture is the high-end desktop Core i7, which was released in November 2008. Server processors of the Xeon 55xx range were first supplied to testers in December 2008.[37]

The performance improvements over Wolfdale-DP and Harpertown processors are based mainly on:

- Monolithic design for quad-core models

- Integrated memory controller supporting three memory channels of DDR3 memory with ECC support.

- A new point-to-point processor interconnect QuickPath, replacing the legacy front side bus. Gainestown has two QuickPath interfaces.

- Hyper-threading (2× per core, starting from 5518), that was already present in NetBurst-based processors

- Turbo Boost, an overclocking technology that allows the CPU to run at a clock speed higher than the base speed as needed

| Model | Speed | L3 cache | QPI speed | DDR3 speed | TDP | Cores | Threads | Turbo-Boost |

|---|---|---|---|---|---|---|---|---|

| E5502 | 1.87 GHz | 4 MB | 4.8 GT/s | 800 MT/s | 80 W | 2 | No | |

| E5503 | 2.00 GHz | |||||||

| E5504 | 4 | 4 | ||||||

| E5506 | 2.13 GHz | |||||||

| L5506 | 60 W | |||||||

| E5507 | 2.26 GHz | 80 W | ||||||

| L5518 | 2.13 GHz | 8 MB | 5.86 GT/s | 1066 MT/s | 60 W | 8 | Yes | |

| E5520 | 2.26 GHz | 80 W | ||||||

| L5520 | 60 W | |||||||

| E5530 | 2.40 GHz | 80 W | ||||||

| L5530 | 60 W | |||||||

| E5540 | 2.53 GHz | 80 W | ||||||

| X5550 | 2.66 GHz | 6.4 GT/s | 1333 MT/s | 95 W | ||||

| X5560 | 2.80 GHz | |||||||

| X5570 | 2.93 GHz | |||||||

| W5580 | 3.20 GHz | 130 W | ||||||

| W5590 | 3.33 GHz | |||||||

C3500/C5500-series "Jasper Forest"[edit]

| General information | |

|---|---|

| Launched | 2010 |

| Discontinued | present |

| CPUID code | 106Ex |

| Product code | 80612 |

| Performance | |

| Max. CPU clock rate | 1.733 GHz to 2.40 GHz |

| Cache | |

| L2 cache | 4×256 kB |

| L3 cache | 8 MB |

| Architecture and classification | |

| Application | UP/DP Server |

| Technology node | 45 nm |

| Microarchitecture | Nehalem |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand names |

|

Jasper Forest is a Nehalem-based embedded processor with PCI Express connections on-die, core counts from 1 to 4 cores and power envelopes from 23 to 85 watts.[38]

The uni-processor version without QPI comes as LC35xx and EC35xx, while the dual-processor version is sold as LC55xx and EC55xx and uses QPI for communication between the processors. Both versions use a DMI link to communicate with the 3420 that is also used in the 3400-series Lynfield Xeon processors, but use an LGA 1366 package that is otherwise used for processors with QPI but no DMI or PCI Express links. The CPUID code of both Lynnfield and Jasper forest is 106Ex, i.e., family 6, model 30.

The Celeron P1053 belongs into the same family as the LC35xx series, but lacks some RAS features that are present in the Xeon version.

W3600/5600-series "Gulftown" & "Westmere-EP"[edit]

Gulftown and Westmere-EP, six-core 32 nm architecture Westmere-based processors, are the basis for the Xeon 36xx and 56xx series and the Core i7-980X. It launched in the first quarter of 2010. The 36xx-series follows the 35xx-series Bloomfield uni-processor model while the 56xx-series follows the 55xx-series Gainestown dual-processor model and both are socket compatible to their predecessors.

| Model | Speed | L3 cache | QPI speed | DDR3 speed | TDP | Cores | Threads | Turbo-Boost |

|---|---|---|---|---|---|---|---|---|

| W3670 | 3.20 GHz | 12 MB | 4.8 GT/s | 1066 MT/s | 130 W | 6 | 12 | Yes |

| W3680 | 3.33 GHz | 6.4 GT/s | 1333 MT/s | |||||

| W3690 | 3.46 GHz | |||||||

| E5603 | 1.60 GHz | 4 MB | 4.8 GT/s | 800 MT/s | 80 W | 4 | 4 | No |

| E5606 | 2.13 GHz | 8 MB | 1066 MT/s | |||||

| E5607 | 2.26 GHz | |||||||

| L5609 | 1.86 GHz | 12 MB | 40 W | |||||

| L5618 | 5.86 GT/s | 8 | Yes | |||||

| E5620 | 2.40 GHz | 80 W | ||||||

| L5630 | 2.13 GHz | 40 W | ||||||

| E5630 | 2.53 GHz | 80 W | ||||||

| L5638 | 2.00 GHz | 1333 MT/s | 60 W | 6 | 12 | |||

| L5639 | 2.13 GHz | |||||||

| L5640 | 2.26 GHz | |||||||

| E5640 | 2.66 GHz | 1066 MT/s | 80 W | 4 | 8 | |||

| L5645 | 2.40 GHz | 1333 MT/s | 60 W | 6 | 12 | |||

| E5645 | 80 W | |||||||

| E5649 | 2.53 GHz | |||||||

| X5650 | 2.66 GHz | 6.4 GT/s | 95 W | |||||

| X5660 | 2.80 GHz | |||||||

| X5667 | 3.06 GHz | 4 | 8 | |||||

| X5670 | 2.93 GHz | 6 | 12 | |||||

| X5672 | 3.20 GHz | 4 | 8 | |||||

| X5675 | 3.06 GHz | 6 | 12 | |||||

| X5677 | 3.46 GHz | 130 W | 4 | 8 | ||||

| X5679 | 3.20 GHz | 1066 MT/s | 115 W | 6 | 12 | |||

| X5680 | 3.33 GHz | 1333 MT/s | 130 W | |||||

| X5687 | 3.60 GHz | 4 | 8 | |||||

| X5690 | 3.46 GHz | 6 | 12 | |||||

| X5698 | 4.40 GHz | 1066 MT/s | 2 | 4 | No |

6500/7500-series "Beckton"[edit]

Xeon E7530 (with and without the heat spreader) | |

| General information | |

|---|---|

| Launched | March 30, 2010 |

| Discontinued | Q4 2012 |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer | |

| CPUID code | 206Ex |

| Product code | 80604 |

| Performance | |

| Max. CPU clock rate | 1.733 GHz to 2.667 GHz |

| QPI speeds | 6.4 GT/s |

| Cache | |

| L2 cache | 256 KB per core |

| L3 cache | Up to 24 MB |

| Architecture and classification | |

| Application | DP/MP Server |

| Technology node | 45 nm |

| Microarchitecture | Nehalem |

| Instruction set | x86-16, IA-32, x86-64 |

| Physical specifications | |

| Cores |

|

| Package | |

| Products, models, variants | |

| Brand names |

|

Beckton or Nehalem-EX (Expandable server market) is a Nehalem-based processor with up to eight cores and uses buffering inside the chipset to support up to 16 standard DDR3 DIMMs per CPU socket without requiring the use of FB-DIMMs.[39] Unlike all previous Xeon MP processors, Nehalem-EX uses the new LGA 1567 (Socket LS) package, replacing the Socket 604 used in the previous models, up to Xeon 7400 "Dunnington". The 75xx models have four QuickPath interfaces, so it can be used in up-to eight-socket configurations, while the 65xx models are only for up to two sockets. Designed by the Digital Enterprise Group (DEG) Santa Clara and Hudson Design Teams, Beckton is manufactured on the P1266 (45 nm) technology. Its launch in March 2010 coincided with that of its direct competitor, AMD's Opteron 6xxx "Magny-Cours".[40]

Most models limit the number of cores and QPI links as well as the L3 cache size in order to get a broader range of products out of the single chip design.

E7-x8xx-series "Westmere-EX"[edit]

Westmere-EX is the follow-on to Beckton/Nehalem-EX and the first Intel processor to have ten CPU cores. The microarchitecture is the same as in the six-core Gulftown/Westmere-EP processor, but it uses the LGA 1567 package like Beckton to support up to eight sockets.

Starting with Westmere-EX, the naming scheme has changed once again, with "E7-xxxx" now signifying the high-end line of Xeon processors using a package that supports larger than two-CPU configurations, formerly the 7xxx series. Similarly, the 3xxx uniprocessor and 5xxx dual-processor series turned into E3-xxxx and E5-xxxx, respectively, for later processors.

Sandy Bridge- and Ivy Bridge-based Xeon[edit]

E3-12xx-series "Sandy Bridge"[edit]

The Xeon E3-12xx line of processors, introduced in April 2011, uses the Sandy Bridge chips that are also the base for the Core i3/i5/i7-2xxx and Celeron/Pentium Gxxx products using the same LGA 1155 socket, but with a different set of features disabled. Notably, the Xeon variants include support for ECC memory, VT-d and trusted execution that are not present on the consumer models, while only some Xeon E3 enable the integrated GPU that is present on Sandy Bridge. Like its Xeon 3400-series predecessors, the Xeon E3 only supports operation with a single CPU socket and is targeted at entry-level workstations and servers. The CPUID of this processor is 0206A7h, the product code is 80623.

E3-12xx v2-series "Ivy Bridge"[edit]

Xeon E3-12xx v2 is a minor update of the Sandy Bridge-based E3-12xx, using the 22 nm shrink, and providing slightly better performance while remaining backwards compatible. They were released in May 2012 and mirror the desktop Core i3/i5/i7-3xxx parts.

E5-14xx/24xx series "Sandy Bridge-EN" and E5-16xx/26xx/46xx-series "Sandy Bridge-EP"[edit]

The Xeon E5-16xx processors follow the previous Xeon 3500/3600-series products as the high-end single-socket platform, using the LGA 2011 package introduced with this processor. They share the Sandy Bridge-E platform with the single-socket Core i7-38xx and i7-39xx processors. The CPU chips have no integrated GPU but eight CPU cores, some of which are disabled in the entry-level products. The Xeon E5-26xx line has the same features but also enables multi-socket operation like the earlier Xeon 5000-series and Xeon 7000-series processors.

E5-14xx v2/24xx v2 series "Ivy Bridge-EN" and E5-16xx v2/26xx v2/46xx v2 series "Ivy Bridge-EP"[edit]

The Xeon E5 v2 line was an update, released in September 2013 to replace the original Xeon E5 processors with a variant based on the Ivy Bridge shrink. The maximum number of CPU cores was raised to 12 per processor module and the total L3 cache was upped to 30 MB.[41][42] The consumer version of the Xeon E5-16xx v2 processor is the Core i7-48xx and 49xx.

E7-28xx v2/48xx v2/88xx v2 series "Ivy Bridge-EX"[edit]

The Xeon E7 v2 line was an update, released in February 2014 to replace the original Xeon E7 processors with a variant based on the Ivy Bridge shrink. There was no Sandy Bridge version of these processors but rather a Westmere version.

Haswell-based Xeon[edit]

E3-12xx v3 series "Haswell-WS"[edit]

Introduced in May 2013, Xeon E3-12xx v3 is the first Xeon series based on the Haswell microarchitecture. It uses the new LGA 1150 socket, which was introduced with the desktop Core i5/i7 Haswell processors, incompatible with the LGA 1155 that was used in Xeon E3 and E3 v2. As before, the main difference between the desktop and server versions is added support for ECC memory in the Xeon-branded parts. The main benefit of the new microarchitecture is better power efficiency.

E5-16xx/26xx v3 series "Haswell-EP"[edit]

Introduced in September 2014, Xeon E5-16xx v3 and Xeon E5-26xx v3 series use the new LGA 2011-v3 socket, which is incompatible with the LGA 2011 socket used by earlier Xeon E5 and E5 v2 generations based on Sandy Bridge and Ivy Bridge microarchitectures. Some of the main benefits of this generation, compared to the previous one, are improved power efficiency, higher core counts, and bigger last level caches (LLCs). Following the already used nomenclature, Xeon E5-26xx v3 series allows dual-socket operation.

One of the new features of this generation is that Xeon E5 v3 models with more than 10 cores support cluster on die (COD) operation mode, allowing CPU's multiple columns of cores and LLC slices to be logically divided into what is presented as two non-uniform memory access (NUMA) CPUs to the operating system. By keeping data and instructions local to the "partition" of CPU which is processing them, thus decreasing the LLC access latency, COD brings performance improvements to NUMA-aware operating systems and applications.[43]

E7-48xx/88xx v3 series "Haswell-EX"[edit]

Introduced in May 2015, Xeon E7-48xx v3 and Xeon E7-88xx v3 series provide higher core counts, higher per-core performance and improved reliability features, compared to the previous Xeon E7 v2 generation. Following the usual SKU nomenclature, Xeon E7-48xx v3 and E7-88xx v3 series allow multi-socket operation, supporting up to quad- and eight-socket configurations, respectively.[44][45] These processors use the LGA 2011 (R1) socket.[46]

Xeon E7-48xx v3 and E7-88xx v3 series contain a quad-channel integrated memory controller (IMC), supporting both DDR3 and DDR4 LRDIMM or RDIMM memory modules through the use of Jordan Creek (DDR3) or Jordan Creek 2 (DDR4) memory buffer chips. Both versions of the memory buffer chip connect to the processor using version 2.0 of the Intel Scalable Memory Interconnect (SMI) interface, while supporting lockstep memory layouts for improved reliability. Up to four memory buffer chips can be connected to a processor, with up to six DIMM slots supported per each memory buffer chip.[44][45]

Xeon E7-48xx v3 and E7-88xx v3 series also contain functional bug-free support for Transactional Synchronization Extensions (TSX), which was disabled via a microcode update in August 2014 for Haswell-E, Haswell-WS (E3-12xx v3) and Haswell-EP (E5-16xx/26xx v3) models, due to a bug that was discovered in the TSX implementation.[44][45][47][48][49][50]

Broadwell-based Xeon[edit]

E3-12xx v4 series "Broadwell-H"[edit]

Introduced in June 2015, Xeon E3-12xx v4 is the first Xeon series based on the Broadwell microarchitecture. It uses LGA 1150 socket, which was introduced with the desktop Core i5/i7 Haswell processors. As before, the main difference between the desktop and server versions is added support for ECC memory in the Xeon-branded parts. The main benefit of the new microarchitecture is the new lithography process, which results in better power efficiency.

Skylake-based Xeon[edit]

E3-12xx v5 series "Skylake-S"[edit]

Introduced in October 2015, Xeon E3-12xx v5 is the first Xeon series based on the Skylake microarchitecture. It uses new LGA 1151 socket, which was introduced with the desktop Core i5/i7 Skylake processors. Although it uses the same socket as consumer processors, it is limited to the C200 server chipset series and will not work with consumer chipsets like Z170. As before, the main difference between the desktop and server versions is added support for ECC memory in the Xeon-branded parts.

1st generation Xeon Scalable "Skylake-SP"[edit]

Kaby Lake-based Xeon[edit]

E3-12xx v6 series[edit]

Introduced in January 2017, Xeon E3-12xx v6 is the first Xeon series based on the Kaby Lake microarchitecture. It uses the same LGA 1151 socket, which was introduced with the desktop Core i5/i7 Kaby Lake processors. As before, the main difference between the desktop and server versions is added support for ECC memory and improved energy efficiency in the Xeon-branded parts.

Coffee Lake-based Xeon[edit]

Coffee Lake-E (Server/Workstation)[edit]

| Processor branding |

Model | Cores

(Threads) |

Base CPU clock rate |

Max. Turbo

clock rate |

GPU | max GPU clock rate |

L3 cache [note 1] |

TDP | Memory support |

Price (USD) |

|---|---|---|---|---|---|---|---|---|---|---|

| Xeon E | 2186G | 6 (12) | 3.8 GHz | 4.7 GHz | UHD P630 | 1.20 GHz | 12 MB | 95 W | Up to 64 GB[note 2] DDR4 2666 ECC memory supported |

$506 |

| 2176G | 3.7 GHz | 80 W | $406 | |||||||

| 2174G | 4 (8) | 3.8 GHz | 8 MB | 71 W | $370 | |||||

| 2146G | 6 (12) | 3.5 GHz | 4.5 GHz | 12 MB | 80 W | $350 | ||||

| 2144G | 4 (8) | 3.6 GHz | 8 MB | 71 W | $306 | |||||

| 2136 | 6 (12) | 3.3 GHz | N/A | 12 MB | 80 W | $319 | ||||

| 2134 | 4 (8) | 3.5 GHz | 8 MB | 71 W | $281 | |||||

| 2126G | 6 (6) | 3.3 GHz | UHD P630 | 1.20 GHz | 12 MB | 80 W | $286 | |||

| 2124G | 4 (4) | 3.4 GHz | 8 MB | 71 W | $245 | |||||

| 2124 | 3.3 GHz | 4.3 GHz | N/A | $217 | ||||||

| 2104G | 3.2 GHz | N/A | UHD P630 | 1.20 GHz | 65 W | $193 | ||||

Coffee Lake-E Refresh (Server/Workstation)[edit]

| Processor branding |

Model | Cores

(Threads) |

Base CPU clock rate |

Max. Turbo

clock rate |

GPU | max GPU clock rate |

L3 cache [note 3] |

TDP | Memory support |

Price (USD) |

|---|---|---|---|---|---|---|---|---|---|---|

| Xeon E | 2288G | 8 (16) | 3.7 GHz | 5.0 GHz | UHD P630 | 1.20 GHz | 16 MiB | 95 W | Up to 128 GB[note 4] DDR4 2666 ECC memory supported |

$539 |

| 2286G | 6 (12) | 4.0 GHz | 4.9 GHz | 12 MiB | $450 | |||||

| 2278G | 8 (16) | 3.4 GHz | 5.0 GHz | 16 MiB | 80 W | $494 | ||||

| 2276G | 6 (12) | 3.8 GHz | 4.9 GHz | 12 MiB | $362 | |||||

| 2274G | 4 (8) | 4.0 GHz | 8 MiB | 83 W | $328 | |||||

| 2246G | 6 (12) | 3.6 GHz | 4.8 GHz | 12 MiB | 80 W | $311 | ||||

| 2244G | 4 (8) | 3.8 GHz | 8 MiB | 71 W | $272 | |||||

| 2236 | 6 (12) | 3.4 GHz | N/A | 12 MiB | 80 W | $284 | ||||

| 2234 | 4 (8) | 3.6 GHz | 8 MiB | 71 W | $250 | |||||

| 2226G | 6 (6) | 3.4 GHz | 4.7 GHz | UHD P630 | 1.20 GHz | 12 MiB | 80 W | $255 | ||

| 2224G | 4 (4) | 3.5 GHz | 8 MiB | 71 W | $213 | |||||

| 2224 | 3.4 GHz | 4.6 GHz | N/A | $193 | ||||||

Comet Lake-based Xeon[edit]

Cascade Lake-based Xeon[edit]

Variants[edit]

- Server: Cascade Lake-SP (Scalable Performance; meaning multi physical processors configuration), Cascade Lake-AP (Advanced Performance)

- Workstation: Cascade Lake-W

- Enthusiast: Cascade Lake-X

Cooper Lake-based Xeon[edit]

The 3rd generation Xeon SP processors for 4S and 8S.

Ice Lake-based Xeon[edit]

The 3rd generation Xeon SP processors for WS, 1S and 2S.

Rocket Lake-based Xeon[edit]

Sapphire Rapids-based Xeon[edit]

Introduced in 2023, the 4th generation Xeon Scalable processors (Sapphire Rapids-SP and Sapphire Rapids-HBM) and Xeon W-2400 and W-3400 series (Sapphire Rapids-WS) provide large performance enhancements over the prior generation.

Features[edit]

CPU[edit]

- Up to 60 Golden Cove CPU cores per package

- AVX512-FP16

- TSX Suspend Load Address Tracking (

TSXLDTRK) - Advanced Matrix Extensions (AMX)

- Trust Domain Extensions (TDX), a collection of technologies to help deploy hardware-isolated virtual machines (VMs) called trust domains (TDs)

- In-Field Scan (IFS), a technology that allows for testing the processor for potential hardware faults without taking it completely offline

- Data Streaming Accelerator (DSA), allows for speeding up data copy and transformation between different kinds of storage

- QuickAssist Technology (QAT), allows for improved performance of compression and encryption tasks

- Dynamic Load Balancer (DLB), allows for offloading tasks of load balancing, packet prioritization and queue management

- In-Memory Analytics Accelerator (IAA), allows accelerating in-memory databases and big data analytics

Not all accelerators are available in all processor models. Some accelerators are available under the Intel On Demand program, also known as Software Defined Silicon (SDSi), where a license is required to activate a given accelerator that is physically present in the processor. The license can be obtained as a one-time purchase or as a paid subscription. Activating the license requires support in the operating system. A driver with the necessary support was added in Linux kernel version 6.2.

I/O[edit]

- PCI Express 5.0

- Direct Media Interface 4.0

- 8-channel DDR5 memory support up to DDR5-4800, up to 2 DIMMs per channel

- On-package High Bandwidth Memory 2e memory as L4 cache on Xeon Max models

- Compute Express Link 1.1

Emerald Rapids-based Xeon[edit]

Supercomputers[edit]

By 2013 Xeon processors were ubiquitous in supercomputers—more than 80% of the TOP500 machines in 2013 used them. For the fastest machines, much of the performance comes from compute accelerators; Intel's entry into that market was the Xeon Phi, the first machines using it appeared in June 2012 and by June 2013 it was used in the fastest computer in the world.

- The first Xeon-based machines in the top-10 appeared in November 2002, two clusters at Lawrence Livermore National Laboratory and at NOAA.

- The first Xeon-based machine to be in the first place of the TOP500 was the Chinese Tianhe-IA in November 2010, which used a mixed Xeon-Nvidia GPU configuration; it was overtaken by the Japanese K computer in 2012, but the Tianhe-2 system using 12-core Xeon E5-2692 processors and Xeon Phi cards occupied the first place in both TOP500 lists of 2013.

- The SuperMUC system, using eight-core Xeon E5-2680 processors but no accelerator cards, managed fourth place in June 2012 and had dropped to tenth by November 2013

- Xeon processor-based systems are among the top 20 fastest systems by memory bandwidth as measured by the STREAM benchmark.[51]

- An Intel Xeon virtual SMP system using ScaleMP's Versatile SMP (vSMP) architecture with 128 cores and 1 TiB RAM.[52] This system aggregates 16 Stoakley platform (Seaburg chipset) systems with total of 32 Harpertown processors.

See also[edit]

- AMD Epyc

- AMD Opteron

- Intel Itanium

- Intel Xeon Phi, brand name for family of products using the Intel MIC architecture

- List of Intel processors

- List of Macintosh models grouped by CPU type

Notes[edit]

References[edit]

- ^ Cutress, Ian (November 15, 2021). "Intel: Sapphire Rapids With 64 GB of HBM2e, Ponte Vecchio with 408 MB L2 Cache". AnandTech. Retrieved December 11, 2022.

- ^ Jump up to: a b c d "Intel Launches New Xeon Workstation Processors – the Ultimate Solution for Professionals". Intel. Retrieved February 18, 2023.

- ^ "Intel Max Series Brings Breakthrough Memory Bandwidth and Performance to HPC and AI". Intel Newsroom. November 9, 2022. Retrieved December 22, 2022.

- ^ Chiapetta, Marco (April 9, 2024). "Intel Unveils Powerful, Efficient Gaudi 3 AI Accelerator And New Xeon 6 Processors At Vision 2024". Forbes. Retrieved April 22, 2024.

- ^ Bonshor, Gavin (April 9, 2024). "Intel Unveils New Branding For 6th Generation Xeon Processors: Intel Xeon 6". AnandTech. Retrieved April 22, 2024.

- ^ "Intel's Xeon brand makes its first foray into SoC space with Xeon D". Ars Technica. March 10, 2015. Retrieved April 22, 2024.

- ^ Prickett Morgan, Timothy (March 9, 2015). "Intel Crafts Broadwell Xeon D For Hyperscale". The Next Platform. Retrieved April 22, 2024.

- ^ Bateman, B.; et al. (February 1998). A 450MHz 512 kB Second-Level Cache with a 3.6GB/s Data Bandwidth. International Solid-State Circuits Conference. pp. 358–359. doi:10.1109/ISSCC.1998.672528. ISBN 0-7803-4344-1. S2CID 21384417.

- ^ "New High-End Intel Server Processors Expand Performance Leadership" (Press release). Intel. August 29, 2006.

- ^ "Intel Xeon Processor 7100 Series Specification Update" (PDF). Intel. March 2010.

- ^ "Intel prices up Woodcrest, Tulsa server chips". The Inquirer. May 26, 2006. Archived from the original on January 3, 2007.

{{cite web}}: CS1 maint: unfit URL (link) - ^ "Intel drops 32-bit dual-core LV processors". TG Daily. Retrieved July 31, 2007.

- ^ Huynh, Anh Tuan (July 19, 2006). "Intel Adds Low End Xeons to Roadmap". DailyTech. Archived from the original on April 2, 2016.

- ^ "Intel Readies New Xeons and Price Cuts". WinBeta.org. Archived from the original on September 27, 2007.

- ^ "ARK - Your Source for Intel® Product Information". Intel® ARK (Product Specs).

- ^ "Dual-Core Intel Xeon Processor 5200 Series" (PDF). Intel. August 2008.

- ^ "Intel Ships New Processors for Embedded, Communications and Storage Markets Based on New Transistors, Manufacturing". Intel (Press release). Santa Clara, CA. February 27, 2008. Retrieved December 10, 2022.

- ^ "Intel bares Tigerton". The Register.

- ^ Donald Melanson (October 23, 2006). "Intel previews quad-core Xeon "Tigerton" server processor". Engadget. AOL.

- ^ "Rap meets tech at IDF yo". theinquirer.net. Archived from the original on April 19, 2007.

{{cite web}}: CS1 maint: unfit URL (link) - ^ "Dual-Core Intel® Xeon® Processor 7200 Series and Quad-Core Intel® Xeon® Processor 7300 Series Datasheet" (PDF). Intel. September 2007. Archived from the original (PDF) on October 25, 2007. Retrieved September 19, 2007.

- ^ Huynh, Anh Tuan (January 7, 2007). "Intel Hard-Launches Three New Quad-core Processors". DailyTech. Archived from the original on April 5, 2016.

- ^ "Intel Clovertowns step up, reduce power". TG Daily. Archived from the original on 11 September 2007. Retrieved 5 September 2007.

- ^ Jump up to: a b Huynh, Anh Tuan (September 21, 2006). "Quad-core Xeon Details Unveiled". DailyTech. Archived from the original on December 16, 2017.

- ^ "Intel Ignites Quad-Core Era" (Press release). Intel.

- ^ "Apple - Mac Pro - The fastest, most powerful Mac ever". Archived from the original on June 2, 2013.

- ^ Gruener, Wolfgang; Cheung, Humphrey (September 26, 2006). "Intel CEO announces Core 2 Quad". TG Daily. Archived from the original on October 26, 2006.

- ^ "Intel Readies New Xeons and Price Cuts". DailyTech. Archived from the original on June 12, 2016.

- ^ "Intel® Xeon® Processor E5-2600 v4 Family World Record".

- ^ "Quad-Core Intel Xeon Processor 5400 Series" (PDF). Intel. August 2008.

- ^ "Intel Readies 1600 MHz Front-Side Bus Xeons". DailyTech. Archived from the original on April 1, 2016.

- ^ "Intel Xeons Coming With 1600MHz FSB". TrustedReviews.

- ^ "Intel Launches First Industry-Standard Quad-Core Products for High-End, Multi-Processor Servers". Intel (Press release). Santa Clara, CA. September 5, 2007. Retrieved November 13, 2022.

- ^ Valich, Theo (February 25, 2008). "Intel six-core coming in 2008". TG Daily. Tigervision Media. Archived from the original on February 27, 2008. Retrieved February 26, 2008.

- ^ Prickett Morgan, Timothy (September 15, 200). "Chipzilla unveils six-core 'Dunnington' Xeons". The Register. Retrieved December 10, 2022.

- ^ "Intel® Xeon® Processor E7 Family". Intel. Archived from the original on December 30, 2008.

- ^ De Gelas, Johan (December 16, 2008). "Intel Xeon 5570: Smashing SAP records". AnandTech. Retrieved December 10, 2022.

- ^ "Intel demos Moorestown, embeds Nehalem". The Register.

- ^ Shimpi, Anand Lal (May 27, 2009). "Nehalem-EX: 2.3 billion transistors, eight cores, one die". AnandTech. Retrieved December 10, 2022.

- ^ Novakovic, Nebojsa (February 12, 2009). "Intel's next bunch of fun CPUs moves to 2010". The Inquirer. Archived from the original on March 4, 2009.

{{cite web}}: CS1 maint: unfit URL (link) - ^ Prickett Morgan, Timothy (September 10, 2013). "Intel carves up Xeon E5-2600 v2 chips for two-socket boxes". The Register. Retrieved November 13, 2022.

- ^ "Intel Introduces Highly Versatile Datacenter Processor Family Architected for New Era of Services". Intel Newsroom. September 10, 2013. Retrieved September 13, 2013.

- ^ De Gelas, Johan (September 8, 2014). "Intel Xeon E5 Version 3, Up to 18 Haswell EP Cores: The Magic Inside the Uncore". AnandTech. Retrieved September 9, 2014.

- ^ Jump up to: a b c Shvets, Anthony (May 7, 2015). "Intel launches Xeon E7 v3 server processors". CPU-World. Retrieved May 16, 2015.

- ^ Jump up to: a b c De Gelas, Johan (May 8, 2015). "The Intel Xeon E7-8800 v3 Review: The POWER8 Killer?". AnandTech. Retrieved May 16, 2015.

- ^ Mujtaba, Hassan (May 6, 2015). "Intel Unleashes Haswell-EX Xeon E7 V3 Processors – Up to 18 Cores, 45 MB L3 Cache, 12 TB DDR4 Memory Support and 5.7 Billion Transistors". Wccftech. Retrieved January 29, 2016.

- ^ Cutress, Ian (August 12, 2014). "Intel Disables TSX Instructions: Erratum Found in Haswell, Haswell-E/EP, Broadwell-Y". AnandTech. Retrieved August 30, 2014.

- ^ "Transactional Synchronization in Haswell". Intel. February 7, 2012. Archived from the original on February 8, 2012. Retrieved February 7, 2012.

- ^ Wasson, Scott (August 12, 2014). "Errata prompts Intel to disable TSX in Haswell, early Broadwell CPUs". Tech Report. Retrieved August 12, 2014.

- ^ "Desktop 4th Generation Intel Core Processor Family, Desktop Intel Pentium Processor Family, and Desktop Intel Celeron Processor Family: Specification Update (Revision 039US)" (PDF). Intel. April 2020. p. 46. Retrieved November 13, 2022.

Under a complex set of internal timing conditions and system events, software using the Intel TSX (Transactional Synchronization Extensions) instructions may observe unpredictable system behavior.

- ^ McCalpin, John D. "STREAM benchmark". University of Virginia. Retrieved December 10, 2022.

- ^ "STREAM "Top20" results". University of Virginia. Retrieved December 10, 2022.