MIPS architecture processors

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

|

Since 1985, many processors implementing some version of the MIPS architecture have been designed and used widely.

MIPS microprocessors

[edit]

The first MIPS microprocessor, the R2000, was announced in 1985. It added multiple-cycle multiply and divide instructions in a somewhat independent on-chip unit. New instructions were added to retrieve the results from this unit back to the processor register file; these result-retrieving instructions were interlocked.

The R2000 could be booted either big-endian or little-endian. It had thirty-one 32-bit general purpose registers, but no status register (condition code register (CCR), the designers considered it a potential bottleneck), a feature it shares with the AMD 29000, the DEC Alpha, and RISC-V. Unlike other registers, the program counter is not directly accessible.

The R2000 also had support for up to four co-processors, one of which was built into the main central processing unit (CPU) and handled exceptions, traps and memory management, while the other three were left for other uses. One of these could be filled by the optional R2010 floating-point unit (FPU), which had thirty-two 32-bit registers that could be used as sixteen 64-bit registers for double-precision.

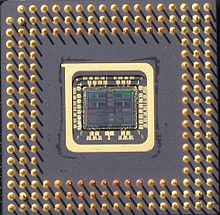

The R3000 succeeded the R2000 in 1988, adding 32 KB (soon raised to 64 KB) caches for instructions and data, and support for shared-memory multiprocessing in the form of a cache coherence protocol. While there were flaws in the R3000s multiprocessing support, it was successfully used in several successful multiprocessor computers. The R3000 also included a built-in memory management unit (MMU), a common feature on CPUs of the era. The R3000, like the R2000, could be paired with a R3010 FPU. The R3000 was the first successful MIPS design in the market, and eventually over one million were made. A faster version of the R3000 running up to 40 MHz, the R3000A delivered a performance of 32 million instructions per second (MIPS), or VAX Unit of Performance (VUPs). The MIPS R3000A-compatible R3051 running at 33.8688 MHz was the processor used in the Sony PlayStation though it didn't have FPU or MMU. Third-party designs include Performance Semiconductor's R3400 and IDT's R3500, both of them were R3000As with an integrated R3010 FPU. Toshiba's R3900 was a virtually first system on a chip (SoC) for the early handheld PCs that ran Windows CE. A radiation-hardened variant for outer space use, the Mongoose-V, is a R3000 with an integrated R3010 FPU.

The R4000 series, released in 1991, extended MIPS to a full 64-bit word design, moved the FPU onto the main die to form a single-chip microprocessor, and had a then high clock rate of 100 MHz at introduction. However, to achieve the clock frequency, the caches were reduced to 8 KB each and they took three cycles to access. The high clock rates were achieved through the method of deep pipelining (called super-pipelining then). The improved R4400 followed in 1993. It had larger 16 KB primary caches, largely bug-free 64-bit operation, and support for a larger L2 cache.

MIPS, now a division of Silicon Graphics (SGI) named MTI, designed the low-cost R4200, the basis for the even cheaper R4300i. A derivative of this microprocessor, the NEC VR4300, was used in the Nintendo 64 game console.[1]

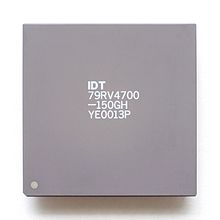

Quantum Effect Devices (QED), a separate company started by former MIPS employees, designed the R4600 Orion, the R4700 Orion, the R4650 and the R5000. Where the R4000 had pushed clock frequency and sacrificed cache capacity, the QED designs emphasized large caches which could be accessed in just two cycles and efficient use of silicon area. The R4600 and R4700 were used in low-cost versions of the SGI Indy workstation as well as the first MIPS-based Cisco routers, such as the 36x0 and 7x00-series routers. The R4650 was used in the original WebTV set-top boxes (now Microsoft TV). The R5000 FPU had more flexible single precision floating-point scheduling than the R4000, and as a result, R5000-based SGI Indys had much better graphics performance than similarly clocked R4400 Indys with the same graphics hardware. SGI gave the old graphics board a new name when it was combined with R5000, to emphasize the improvement. QED later designed the RM7000 and RM9000 family of devices for embedded system markets like computer networking and laser printers. QED was acquired by the semiconductor manufacturer PMC-Sierra in August 2000, the latter company continuing to invest in the MIPS architecture. The RM7000 included an integrated 256 KB L2 cache and a controller for optional L3 cache. The RM9xx0 were a family of SOC devices which included northbridge peripherals such as memory controller, PCI controller, Gigabit Ethernet controller and fast I/O such as a HyperTransport port.

The R8000 (1994) was the first superscalar MIPS design, able to execute two integer or floating point and two memory instructions per cycle. The design was spread over six chips: an integer unit (with 16 KB instruction and 16 KB data caches), a floating-point unit, three fully-custom secondary cache tag RAMs (two for secondary cache accesses, one for bus snooping), and a cache controller ASIC. The design had two fully pipelined double precision multiply-add units, which could stream data from the 4 MB off-chip secondary cache. The R8000 powered SGI's POWER Challenge servers in the mid-1990s and later became available in the POWER Indigo2 workstation. Although its FPU performance fit scientific users quite well, its limited integer performance and high cost dampened appeal for most users. The R8000 was sold for only a year and remains fairly rare.

In 1995, the R10000 was released. This processor was a single-chip design, ran at a higher clock frequency than the R8000, and had larger 32 KB primary instruction and data caches. It was also superscalar, but its major innovation was out-of-order execution. Even with one memory pipeline and simpler FPU, the vastly improved integer performance, lower price, and higher density made the R10000 preferable for most customers.

Some later designs have been based upon R10000 core. The R12000 used a 0.25 micrometre process to shrink the chip and achieve higher clock rates. The revised R14000 allowed higher clock rates with added support for double data rate synchronous dynamic random-access memory (DDR SDRAM) static random access memory (SRAM) in the off-chip cache. Later iterations are named R16000 and R16000A, and feature higher clock rates and smaller die manufacturing compared with before.

Other members of the MIPS family include the R6000, an emitter-coupled logic (ECL) implementation produced by Bipolar Integrated Technology. The R6000 introduced the MIPS II architecture. Its translation lookaside buffer (TLB) and cache architecture are different from all other members of the MIPS family. The R6000 did not deliver the promised performance benefits, and although it saw some use in Control Data machines, it quickly disappeared from the mainstream market.

History

[edit]First hardware

[edit]In 1981, John L. Hennessy began the Microprocessor without Interlocked Pipeline Stages (MIPS) project at Stanford University to investigate reduced instruction set computer (RISC) technology. The results of his research convinced him of the future commercial potential of the technology, and in 1984, he took a sabbatical to found MIPS Computer Systems. The company designed a new architecture that was also named MIPS, and introduced the first MIPS implementation, the R2000, in 1985. The R2000 was improved, and the design was introduced as the R3000 in 1988. These 32-bit CPUs formed the basis of their company through the 1980s, used primarily in Silicon Graphics' (SGI) series of workstations and later Digital Equipment Corporation DECstation workstations and servers. The SGI commercial designs deviated from Stanford MIPS by implementing most of the interlocks in hardware, supplying full multiply and divide instructions (among others). The designs were guided, in part, by software architect Earl Killian who designed the MIPS III 64-bit instruction-set extension, and led the work on the R4000 microarchitecture.[2][3]

In 1991 MIPS released the first 64-bit microprocessor, the R4000. However, MIPS had financial difficulties while bringing it to market. The design was so important to SGI, at the time one of MIPS' few major customers, that SGI bought the company in 1992 to guarantee the design would not be lost. The new SGI subsidiary was named MIPS Technologies.

Licensable architecture

[edit]In the early 1990s, MIPS began to license their designs to third-party vendors. This proved fairly successful due to the simplicity of the core, which allowed it to have many uses that would have formerly used much less able complex instruction set computer (CISC) designs of similar gate count and price; the two are strongly related: the price of a CPU is generally related to the number of gates and the number of external pins. Sun Microsystems attempted to enjoy similar success by licensing their SPARC core but was not nearly as successful. By the late 1990s, MIPS was a powerhouse in the embedded processor field. According to MIPS Technologies Inc., there was an exponential growth, with 48-million MIPS-based CPU shipments and 49% of total RISC CPU market share in 1997.[4] MIPS was so successful that SGI spun off MIPS Technologies in 1998. In 2000s fully half of MIPS's income came from licensing their designs, while much of the rest came from contract design work on cores for third parties.

In 1999, MIPS Technologies replaced the previous versions of the MIPS architecture with two architectures, the 32-bit MIPS32 (based on MIPS II with some added features from MIPS III, MIPS IV, and MIPS V) and the 64-bit MIPS64 (based on MIPS V) for licensing. Nippon Electric Corporation (NEC), Toshiba, and SiByte (later acquired by Broadcom) each obtained licenses for the MIPS64 as soon as it was announced. Philips, LSI Logic and Integrated Device Technology (IDT) have since joined them. Today, the MIPS cores are one of the most-used "heavyweight"[clarification needed] cores in the market for computer-like devices: handheld PCs, set-top boxes, etc.

Since the MIPS architecture is licensable, it has attracted several processor start-up companies over the years. One of the first start-ups to design MIPS processors was Quantum Effect Devices (see next section). The MIPS design team that designed the R4300i started the company SandCraft, which designed the R5432 for NEC and later produced the SR71000, one of the first out-of-order execution processors for the embedded market. The original DEC StrongARM team eventually split into two MIPS-based start-ups: SiByte which produced the SB-1250, one of the first high-performance MIPS-based systems-on-a-chip (SOC); while Alchemy Semiconductor (later acquired by AMD) produced the Au-1000 SoC for low-power uses. Lexra used a MIPS-like architecture and added DSP extensions for the audio chip market and multithreading support for the networking market. Due to Lexra not licensing the architecture, two lawsuits were started between the two companies. The first was quickly resolved when Lexra promised not to advertise their processors as MIPS-compatible. The second (about MIPS patent 4814976 for handling unaligned memory access) was protracted, hurt both companies' business, and culminated in MIPS Technologies giving Lexra a free license and a large cash payment.

Two companies have emerged that specialize in building multi-core processor devices using the MIPS architecture. Raza Microelectronics, Inc. bought the product line from failing SandCraft and later produced devices that contained eight cores for the telecommunication and networking markets. Cavium, originally a security processor vendor also produced devices with eight CPU cores, and later up to 32 cores, for the same markets. Both of these firms designed their cores in-house, only licensing the architecture instead of buying cores from MIPS.

The desktop

[edit]Among the manufacturers which have made computer workstation systems using MIPS processors are SGI, MIPS Computer Systems, Inc., Whitechapel Workstations, Olivetti, Siemens-Nixdorf, Acer, Digital Equipment Corporation, NEC, and DeskStation.

Operating systems ported to the architecture include SGI's IRIX, Microsoft's Windows NT (through v4.0), Windows CE, Linux, FreeBSD, NetBSD, OpenBSD, UNIX System V, SINIX, QNX, and MIPS Computer Systems' own RISC/os.

In the early 1990s, speculation occurred that MIPS and other powerful RISC processors would overtake the Intel IA-32 architecture. This was encouraged by the support of the first two versions of Microsoft's Windows NT for Alpha, MIPS and PowerPC, and to a lesser extent the Clipper architecture and SPARC. However, as Intel quickly released faster versions of their Pentium class CPUs, Microsoft Windows NT v4.0 dropped support for anything but IA-32 and Alpha. With SGI's decision to transition to the Itanium and IA-32 architectures in 2007 (following a 2006 Chapter 11 bankruptcy[5]) and 2009 acquisition by Rackable Systems, Inc., support ended for the MIPS/IRIX consumer market in December, 2013 as originally scheduled. However, a support team still exists for special circumstances and refurbished systems that are still available on a limited basis.[6]

Embedded markets

[edit]

Through the 1990s, the MIPS architecture was widely adopted by the embedded market, including for use in computer networking, telecommunications, video arcade games, video game consoles, computer printers, digital set-top boxes, digital televisions, DSL and cable modems, and personal digital assistants.

The low power-consumption and heat characteristics of embedded MIPS implementations, the wide availability of embedded development tools, and knowledge about the architecture means use of MIPS microprocessors in embedded roles is likely to remain common.

Synthesizeable cores for embedded markets

[edit]In recent years[when?] most of the technology used in the various MIPS generations has been offered as semiconductor intellectual property cores (IP cores), as building blocks for embedded processor designs. Both 32-bit and 64-bit basic cores are offered, known as the 4K and 5K. These cores can be mixed with add-in units such as floating-point units (FPU), single instruction, multiple data (SIMD) systems, various input/output (I/O) devices, etc.

MIPS cores have been commercially successful, now having many consumer and industrial uses. MIPS cores can be found in newer Cisco, Linksys and Mikrotik's routerboard routers, cable modems and asymmetric digital subscriber line (ADSL) modems, smartcards, laser printer engines, set-top boxes, robots, and hand-held computers. In cellphones and PDAs, MIPS has been largely unable to displace the incumbent, competing ARM architecture.

MIPS architecture processors include: IDT RC32438; ATI/AMD Xilleon; Alchemy Au1000, 1100, 1200; Broadcom Sentry5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx and CN5xxx; Infineon Technologies EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2; Microchip Technology PIC32; NEC EMMA and EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR4300, VR5432, VR5500; Oak Technologies Generation; PMC-Sierra RM11200; QuickLogic QuickMIPS ESP; Toshiba Donau, Toshiba TMPR492x, TX4925, TX9956, TX7901; KOMDIV-32, KOMDIV-64, ELVEES Multicore from Russia.

MIPS-based supercomputers

[edit]One interesting, less common use of the MIPS architecture is in massive processor count supercomputers. Silicon Graphics (SGI) refocused its business from desktop graphics workstations to the high-performance computing market in the early 1990s. The success of the company's first foray into server systems, the Challenge series based on the R4400 and R8000, and later R10000, motivated SGI to form a vastly more powerful system. The introduction of the integrated R10000 allowed SGI to produce a system, the Origin 2000, eventually scalable to 1024 CPUs using its NUMAlink cc-NUMA interconnect. The Origin 2000 begat the Origin 3000 series which topped out with the same 1,024 maximum CPU count but using the R14000 and R16000 chips up to 700 MHz. Its MIPS-based supercomputers were withdrawn in 2005 when SGI made the strategic decision to move to Intel's Itanium IA-64 architecture.

A high-performance computing startup named SiCortex introduced a massively parallel MIPS-based supercomputer in 2007. The machines are based on the MIPS64 architecture and a high performance interconnect using a Kautz graph topology. The system is very power efficient and computationally powerful.[citation needed] The most innovative aspect of the system was its multicore processing node which integrates six MIPS64 cores, a crossbar switch memory controller, interconnect direct memory access (DMA) engine, Gigabit Ethernet and PCI Express controllers all on a single chip which consumes only 10 watts of power, yet has a peak floating point performance of 6 gigaFLOPS. The most powerful configuration, the SC5832, is a single cabinet supercomputer consisting of 972 such node chips for a total of 5832 MIPS64 processor cores and 8.2 teraFLOPS of peak performance.

Loongson

[edit]Loongson is a family of MIPS-compatible microprocessors designed by the Chinese Academy of Sciences' Institute of Computing Technology (ICT). Independently designed by the Chinese, early models lacked support for four instructions that had been patented by MIPS Technologies.[7] In June 2009, ICT licensed the MIPS32 and MIPS64 architectures from MIPS Technologies.[8] Starting in 2006, many companies released Loongson-based computers, including nettops and netbooks designed for low-power use.[9][10]

In recent years, the Loongson space dedicated chip (1E04/1E0300/1E1000,1F04/1F0300,1J) has been used on 3–5 Beidou navigation satellites.

Dawning 6000

[edit]The Dawning 6000 supercomputer, which has a projected performance of over 1 PFLOPS, will use the Loongson processor. The Dawning 6000 is currently being jointly developed by the ICT and Dawning Information Industry Company. Li Guojie, chairman of Dawning Information Industry Company and director and academician of the ICT, said research and development of the Dawning 6000 is expected to be completed in two years. By then, Chinese-made high-performance computers will be expected to achieve two major goals: first, the adoption of domestically made processors; second, the existing cluster-based system structure of high-performance computers will be changed once performance reaches 1 PFLOPS.

MIPS Aptiv

[edit]Announced in 2012,[11] the MIPS Aptiv family includes three 32-bit CPU products based on the MIPS32 Release 3 architecture.

microAptiv

[edit]microAptiv[12] is a compact, real-time embedded processor core with a five-stage pipeline and the microMIPS code compression instruction set. microAptiv can be either configured as a microprocessor (microAptiv UP) with instruction and data caches and a memory management unit or as a microcontroller (microAptiv UC) with a memory protection unit (MPU). The CPU integrates DSP and SIMD functionality to address signal processing requirements for entry-level embedded segments including industrial control, smart meters, automotive and wired/wireless communications.

interAptiv

[edit]interAptiv[13] is a multiprocessor core leveraging a nine-stage pipeline with multi-threading. The core can be used for highly-parallel tasks requiring cost and power optimization, such as smart gateways, baseband processing in LTE user equipment and small cells, solid-state drive (SSD) controllers, and automotive equipment.

proAptiv

[edit]proAptiv[14] is a superscalar, out-of-order processor core that is available in single and multi-core product versions. proAptiv is designed for application processing in connected consumer electronics, and control plane processing in networking.

MIPS Warrior

[edit]Announced in June 2013,[15] the MIPS Warrior family includes multiple 32-bit and 64-bit CPU products based on the MIPS Release 5 and 6 architectures.

Warrior M-class

[edit]32-bit MIPS cores for embedded and microcontroller uses:

- MIPS M5100 and MIPS M5150 cores (MIPS32 Release 5):[16] five-stage pipeline architecture, microMIPS ISA, the MIPS DSP Module r2, fast interrupt handling, advanced debug/profiling capabilities and power management.

- MIPS M6200 and M6250 cores (MIPS32 Release 6):[17] six-stage pipeline architecture, microMIPS ISA, dedicated DSP and SIMD module

Warrior I-class

[edit]64-bit MIPS CPUs for high-performance, low-power embedded uses:

- MIPS I6400 multiprocessor core (MIPS64 Release 6):[18] simultaneous multi-threading (SMT), hardware virtualization, 128-bit SIMD, advanced power management, multi-context security, extensible to coherent multi-cluster operation.

Warrior P-class

[edit]32-bit and 64-bit MIPS application processors:

- MIPS P5600 multiprocessor core (MIPS32 Release 5):[19] hardware virtualization with hardware table walk, 128-bit SIMD, 40-bit eXtended Physical Addressing (XPA)

- MIPS P6600 multiprocessor core (MIPS64 Release 6): hardware virtualization with hardware table walk, 128-bit SIMD

Trivia

[edit]The MIPS rabbit character from Super Mario 64 was named after the MIPS microprocessor.

See also

[edit]References

[edit]- ^ Bridgman, Aston (20 January 1998). "NEC Offers Two High Cost Performance 64-bit RISC Microprocessors". NEC Corporation (Press release). Retrieved 12 January 2021.

- ^ "Advisory Board". Paravirtual. 2006. Archived from the original on 13 February 2012. Retrieved 26 November 2010.

- ^ "S-1 Supercomputer Alumni: Earl Killian". Clemson University. 28 June 2005. Retrieved 26 November 2010.

Earl Killian's early work w... As MIPS's Director of Architecture, he designed the MIPS III 64-bit instruction-set extension, and led the work on the R4000 microarchitecture. He was a cofounder of QED, which created the R4600 and R5000 MIPS processors. Most recently he was chief architect at Tensilica working on configurable/extensible processors.

- ^ "MIPS Brochure" (PDF). MIPS Technologies Inc. Retrieved March 2, 2013.

- ^ Patrick Fitzgerald (6 May 2006). "Silicon Graphics Seeks Chapter 11 As Sales Decline". Wall Street Journal.

- ^ "End of General Availability for MIPS® IRIX® Products". 2013.

- ^ "China's Microprocessor Dilemma". The Linley Group.

- ^ "China's Institute of Computing Technology Licenses Industry-Standard MIPS Architectures". Archived from the original on 2011-05-08. Retrieved 2017-04-21.

- ^ "LinuxDevices article about the Municator". Archived from the original on 2012-12-16.

- ^ "Yeelong Specs". LinuxDevices. 22 October 2008. Archived from the original on 10 December 2012.

- ^ S., Ganesh T. (10 May 2012). "MIPS Technologies Updates Processor IP Lineup with Aptiv Series". Anandtech. Retrieved 2016-06-22.

- ^ "microAptiv Processor Core". Imagination Technologies. Retrieved 2016-06-22.

- ^ "interAptiv Processor Core". Imagination Technologies. Retrieved 2016-06-22.

- ^ "proAptiv Processor Core". Imagination Technologies. Retrieved 2016-06-22.

- ^ "Introducing the MIPS Series5 'Warrior' CPU cores: the next revolution in processor IP from Imagination". Imagination Technologies. 2013-06-26. Retrieved 2016-06-22.

- ^ "M-Class M51xx Core Family". Imagination Technologies. Retrieved 2016-06-22.

- ^ "M-Class M6200 and M6250 Processor Cores". Imagination Technologies. Retrieved 2016-06-22.

- ^ "I-Class I6400 Multiprocessor Core". Imagination Technologies. Retrieved 2016-06-22.

- ^ "P-Class P5600 Multiprocessor Core". Imagination Technologies. Retrieved 2016-06-22.