Трассировка кэша

В компьютерной архитектуре кэш трассировки или кэш трассировки выполнения представляет собой специализированный кэш инструкций , в котором хранится динамический поток инструкций , известный как трассировка . Это помогает увеличить пропускную способность выборки инструкций и снизить энергопотребление (в случае Intel Pentium 4 ) за счет хранения следов инструкций, которые уже были получены и декодированы. [1] Процессор трассировки [2] — это архитектура, разработанная на основе кэша трассировки и обрабатывающая инструкции с детализацией уровня трассировки. Формальная математическая теория следов описывается моноидами следов .

Фон

[ редактировать ]Самая ранняя научная публикация о кэше трассировки была «Кэш трассировки: подход с малой задержкой к выборке инструкций с высокой пропускной способностью». [1] Этот широко признанный документ был представлен Эриком Ротенбергом, Стивом Беннеттом и Джимом Смитом на конференции Международного симпозиума по микроархитектуре (MICRO) 1996 года. Более ранней публикацией является патент США 5381533, [3] Алекс Пелег и Ури Вайзер из Intel, «Кэш-память инструкций динамического потока, организованная вокруг сегментов трассировки, независимых от виртуальной адресной строки», продолжение приложения, поданного в 1992 году, от которого позже отказались.

Необходимость

[ редактировать ]Более широкие суперскалярные процессоры требуют выборки нескольких инструкций за один цикл для повышения производительности. Инструкции, которые необходимо извлечь, не всегда находятся в смежных ячейках памяти ( базовых блоках ) из-за инструкций ветвления и перехода . Таким образом, процессорам требуется дополнительная логическая и аппаратная поддержка для извлечения и выравнивания таких инструкций из несмежных базовых блоков. Если несколько ветвей прогнозируются как невыполненные , то процессоры могут извлекать инструкции из нескольких смежных базовых блоков за один цикл. Однако если какая-либо из ветвей прогнозируется как занятая , то процессор должен получить инструкции по выбранному пути в том же цикле. Это ограничивает возможности процессора по выборке.

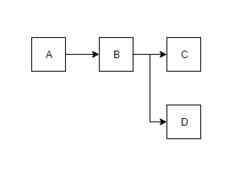

Рассмотрим эти четыре основных блока ( A, B, C, D), как показано на рисунке, которые соответствуют простому циклу if-else . Эти блоки будут храниться рядом как ABCD в памяти. Если ветка D прогнозируется, что он не принят, модуль выборки может извлечь базовые блоки A, B, C которые расположены рядом. Однако, если D прогнозируется извлечь , что устройство выборки должно A, B, D которые расположены несмежно. Следовательно, извлечение этих блоков, которые не расположены рядом друг с другом, за один цикл будет очень затруднительно. Итак, в подобных ситуациях кэш трассировки приходит на помощь процессору.

После извлечения кэш трассировки сохраняет инструкции в их динамической последовательности. Когда эти инструкции встречаются снова, кэш трассировки позволяет блоку выборки команд процессора извлечь из него несколько базовых блоков, не беспокоясь о ветвлениях в потоке выполнения. Инструкции будут храниться в кэше трассировки либо после их декодирования, либо по мере их удаления. Однако последовательность команд является спекулятивной, если они сохраняются сразу после этапа декодирования.

Структура трассировки

[ редактировать ]Трассировка, также называемая динамической последовательностью команд, представляет собой запись в кэше трассировки. Его можно охарактеризовать максимальным количеством инструкций и максимальным количеством базовых блоков . Трассировки могут начинаться с любой динамической инструкции. Несколько трасс могут иметь одну и ту же стартовую инструкцию, т. е. один и тот же стартовый программный счетчик (ПК) и инструкции из разных базовых блоков в соответствии с результатами ветвления. На рисунке выше ABC и ABD являются допустимыми трассами. Оба они начинаются с одного и того же компьютера (адрес A) и имеют разные базовые блоки, согласно предсказанию D.

Трассировки обычно прекращаются, когда происходит одно из следующих событий:

- Трассировка заполнена максимально допустимым количеством инструкций.

- В трассировке имеется максимально допустимое количество базовых блоков.

- Инструкции по возврату

- Косвенные ответвления

- Системные вызовы

Информация о отслеживании контроля

[ редактировать ]Одна трассировка будет содержать следующую информацию:

- Стартовый ПК — ПК первой инструкции в трассировке

- Флаг ветвления - ( максимальное количество базовых блоков -1 ) предсказания ветвления

- Маска ветвей — количество ветвей в трассировке и заканчивается ли трасса веткой или нет.

- Провал трассировки — следующий компьютер, если последняя инструкция не выполнена или не является ветвью.

- Цель трассировки - адрес взятой цели последней ветки.

Проектирование кэша трассировки

[ редактировать ]Ниже приведены факторы, которые необходимо учитывать при проектировании кэша трассировки.

- Политики выбора трассировки — максимальное количество инструкций и максимальное количество базовых блоков в трассировке.

- Ассоциативность - количество способов, которыми может обладать кеш.

- Метод индексации кэша — конкатенация или XOR с битами ПК

- Ассоциативность путей - трассы с одного и того же стартового ПК, но с разными базовыми блоками могут быть сопоставлены с разными наборами.

- Варианты заполнения кэша трассировки —

- После этапа декодирования (предположительно)

- После выхода на пенсию

Кэш трассировки не находится на критическом пути выборки инструкций. [4]

Логика попадания/промаха

[ редактировать ]Строки трассировки сохраняются в кэше трассировки на основе ПК первой инструкции в трассировке и набора предсказаний ветвей. Это позволяет хранить разные пути трассировки, начинающиеся с одного и того же адреса, каждый из которых представляет разные результаты ветвления. Этот метод тегирования помогает обеспечить ассоциативность путей к кэшу трассировки. Другой метод может включать в себя использование только стартового компьютера в качестве тега в кэше трассировки. На этапе выборки команд конвейера текущий компьютер вместе с набором предсказаний ветвей проверяется в кэше трассировки на предмет совпадения . Если есть совпадение, предоставляется строка трассировки для выборки модуля, которому не нужно обращаться к обычному кэшу или памяти для этих инструкций. Кэш трассировки продолжает подавать модуль выборки до тех пор, пока строка трассировки не закончится или пока не произойдет неверный прогноз в конвейере . Если есть промах, начинает строиться новая трасса.

Кэш трассировки выполнения Pentium 4 хранит микрооперации , возникающие в результате декодирования инструкций x86 , обеспечивая также функциональность кэша микроопераций. Благодаря этому в следующий раз, когда понадобится инструкция, ее не придется снова декодировать в микрооперации. [5]

Недостатки

[ редактировать ]Недостатками кэша трассировки являются:

- Резервное хранилище инструкций между кешем трассировки и кешем инструкций, а также внутри самого кеша трассировки. [6]

- Энергоэффективность и сложность оборудования [4]

Кэш трассировки выполнения

[ редактировать ]В кэш L1 процессоров NetBurst Intel включила свой кэш трассировки выполнения. [7] [8] Он хранит декодированные микрооперации , так что при выполнении новой инструкции вместо повторной выборки и декодирования инструкции ЦП напрямую обращается к декодированным микрооперациям из кэша трассировки, тем самым экономя значительное время. Более того, микрооперации кэшируются по прогнозируемому пути их выполнения, а это означает, что когда инструкции извлекаются ЦП из кэша, они уже присутствуют в правильном порядке выполнения. Позже Intel представила аналогичную, но более простую концепцию с Sandy Bridge, названную кешем микроопераций (кэш UOP).

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ Перейти обратно: а б Ротенберг, Эрик; Беннетт, Стив; Смит, Джеймс Э.; Ротенберг, Эрик (1 января 1996 г.). «Кэш трассировки: подход с малой задержкой к выборке инструкций с высокой пропускной способностью» . В материалах 29-го Международного симпозиума по микроархитектуре : 24–34.

- ^ Эрик Ротенберг, Куинн Джейкобсон, Яннакис Сазеидес и Джеймс Э. Смит. Трассировочные процессоры . Материалы 30-го Международного симпозиума IEEE/ACM по микроархитектуре (MICRO-30) , стр. 138-148, декабрь 1997 г.

- ^ Пелег, Александр; Вайзер, Ури (10 января 1995 г.), Кэш-память инструкций динамического потока, организованная вокруг сегментов трассировки, независимых от строки виртуального адреса , получено 18 октября 2016 г.

- ^ Перейти обратно: а б Леон Гу; Дипти Мотиани (октябрь 2003 г.). «Кэш следов» (PDF) . Проверено 6 октября 2013 г.

- ^ Агнер Фог (19 февраля 2014 г.). «Микроархитектура процессоров Intel, AMD и VIA: руководство по оптимизации для программистов-сборщиков и производителей компиляторов» (PDF) . agner.org . Проверено 21 марта 2014 г.

- ^ Ко, Мишель. «Кэш следов» . www.cs.virginia.edu . Проверено 21 октября 2016 г. [ мертвая ссылка ]

- ^ Кармин, Дуг (весна 2002 г.). «Процессор Intel® Pentium® 4» (PDF) . Архивировано из оригинала (PDF) 19 апреля 2018 года. [ ненадежный источник? ]

- ^ «X-bit labs - Версия для печати» . www.xbitlabs.com . Архивировано из оригинала 6 марта 2016 года . Проверено 12 января 2022 г.