Кэш на палке

COASt , аббревиатура от « кэш на карте памяти », представляет собой стандарт упаковки для модулей, содержащих SRAM, используемых в качестве кэша L2 на компьютере. Модули COASt выглядят как модули SIMM несколько увеличенного размера . Эти модули были довольно популярны на платформах Apple и ПК в период с начала до середины 1990-х годов, но в новых компьютерах кэш встроен либо в процессор , либо в материнскую плату . Модули COASt отделили материнскую плату от ее кэша, позволяя создавать различные конфигурации. Недорогая система может работать без кэша, а более дорогая система может иметь кэш объемом 512 КБ или более. Позже модули COASt были оснащены SRAM с конвейерной пакетной передачей данных .

определила стандарт Первоначально компания Motorola шириной от 4,33 до 4,36 дюйма (110 и 111 мм) и высотой от 1,12 до 1,16 дюйма (28 и 29 мм). Его можно было найти во многих Apple Macintosh в начале-середине 90-х, но он исчез, когда Mac перешел на платформу PowerPC .

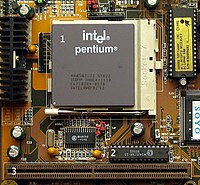

Intel также использовала стандарт COASt для своих систем Pentium , где его можно было найти еще в 1998 году в системах Pentium MMX, использующих наборы микросхем Intel, такие как 430VX и 430TX. Позже Intel объединила эту архитектуру с ЦП и создала картридж ЦП Slot 1 , который содержал как ЦП, так и отдельные микросхемы кэша.

Слот, к которому был подключен модуль COASt, получил название «CELP», или «низкий профиль края карты», что относится к небольшой монтажной плате и проводникам на ее краю. Он имел 80 контактов на каждой стороне печатной платы (всего 160), расположенных на расстоянии 0,050 дюйма друг от друга, плюс идентификационную выемку между контактами 42 и 43.

Операция

[ редактировать ]Модули COASt предоставляли 256 КБ или 512 КБ кэша с прямым отображением , организованного в виде 8192 или 16384 строк по 32 байта. 64-битная шина данных позволяла передавать строку кэша пакетом за 4 такта.

Модули содержали 256 КБ или 512 КБ быстрой конвейерной SRAM , а также 8 или 11 бит еще более быстрой статической оперативной памяти на строку для хранения тегов кэша. (Модуль имеет контакты для 11 линий, но многие материнские платы и модули имеют только 8.) В некоторых вариантах (показано справа) ОЗУ тегов размещалось на материнской плате, а на модуле было только ОЗУ основного кэша.

Сначала рассмотрим модуль 256K. 8-битный тег позволяет кэшировать память, в 256 раз превышающую размер кэша, или 64 МБ. 11-битный тег поддерживает до 512 МБ. Каждая строка кэша также имеет действительный и «грязный» бит, хранящиеся в контроллере кэша. (16 Кбит или 2 Кбайт, общий размер.)

Модуль 512 КБ содержит в два раза больше строк кэша, поэтому для поддержки того же размера кэшируемой памяти требуется на один бит тега меньше. Оставшийся бит тега вместо этого используется для хранения грязного бита строки кэша, а все 16 Кбит в контроллере кэша используются для действительных битов.

Ссылки

[ редактировать ]- Модули COASt , PCGuide, 17 апреля 2001 г.

- Процедура физической установки модуля кэша , PCGuide, 17 апреля 2001 г.

- Ренн, Брайан. Руководство по кэшированию: что такое COASt? , 12 декабря 1998 г.

- Accutek Microcircuit Corporation, Модуль вторичного кэша объемом 512 КБ для процессора Pentium и 82430 PCISETS , получено 1 января 2012 г. Поддерживает 11-битный тег.

- Motorola (09 декабря 1996 г.), Модуль вторичного кэша BurstRAM™ с конвейерной обработкой 256 КБ/512 КБ для Pentium™ (PDF) , получено 1 января 2012 г. . Поддерживает только 8-битные теги.