Графики перехода сигналов

Графики перехода сигналов ( STG ) обычно используются в электронной технике и вычислительной технике для описания динамического поведения асинхронных схем в целях их анализа или синтеза.

Основные определения и приложения

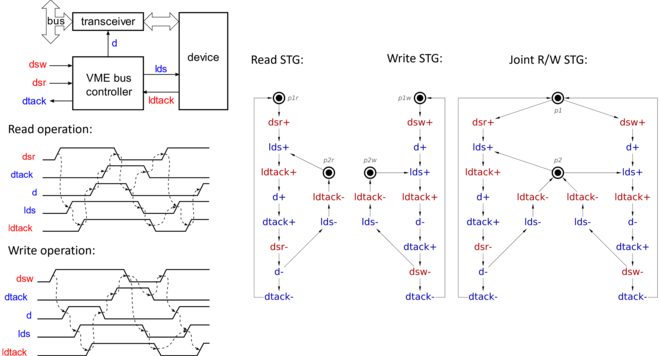

[ редактировать ]Неформально СТГ — это графическое описание поведения асинхронной схемы в виде, где информация о причинно-следственных связях между сигнальными событиями представлена непосредственно, в отличие от описаний, основанных на состояниях. Таким образом, STG помогают формализовать описание схемы, обычно представляемой временными диаграммами , иногда также называемыми формами сигналов . Последние широко используются инженерами-электронщиками.

Более формально, СТГ — это тип интерпретируемой (или помеченной) сети Петри , переходы которой помечены названиями изменений значений сигналов (ср. сигнальные переходы ). Например, типичным случаем маркировки является случай, когда сигналы являются двоичными, поэтому переход интерпретируется как нарастающий и спадающий фронты сигналов в схеме.

STG обычно дают более компактное описание поведения асинхронных схем, чем графы состояний. Сложность спецификации STG схемы обычно линейна в зависимости от количества сигналов в схеме, тогда как сложность графа состояний может расти экспоненциально из-за того, что асинхронные схемы имеют высокую степень параллелизма. В STG параллельные события представлены через отношения «причина-последовательность» (см. «Истинный параллелизм»), тогда как в графах состояний параллелизм представлен через чередование.

СТГ были впервые предложены в 1981 году под названием «Сигнальные графы» Леонидом Розенблюмом (на русском языке). [2] Более формально они были изучены и применены к проектированию асинхронных интерфейсов Алексом Яковлевым в 1982 году в его докторской диссертации. [3] (на русском языке). Позже они были представлены на английском языке в 1985 году в двух независимых источниках, один — Розенблюмом и Яковлевым в [4] а другой - Там-Ань Чу в [5] (более ранняя версия была представлена на ICCD'85). С тех пор СТГ широко изучались в теории и на практике. [6] [7] [8] [9] [10] [11] [12] что привело к разработке популярных программных средств для анализа и синтеза асинхронных схем управления , таких как Petrify [13] (главный разработчик: Jordi Cortadella ) и Workcraft (набор инструментов от Университета Ньюкасла ). [14]

Среди различных примеров использования STG при проектировании асинхронных схем наиболее известны примеры из области асинхронных интерфейсов, контроллеров, арбитров и схем со смешанными аналоговыми сигналами, ср. [15] [9] [16] [17] [18] [19] совсем недавно STG были расширены для моделирования причинного поведения, включающего причинность, опосредованную емкостной связью, например, используемую в преобразователях с переключаемыми конденсаторами (SCC). [20] [21]

Расширения и связанные модели

[ редактировать ]Помимо СТГ, основанных на двоичных сигналах, существуют еще символические СТГ. [22] где сигналы могут быть многозначными.

STG с аннотацией информации о времени (задержках) были впервые представлены в [4] и позже, [23] где идеи анализа поведения схем с временными ограничениями, [24] позже названный «Относительное время», [25] также были впервые представлены.

Специальные расширения базовых моделей сетей Петри для фиксации асинхронности и прерываний в компактной форме были представлены в сетях диаграммы мест. [26] Важная связь между моделями асинхронных схем, основанными на состояниях, и моделями, основанными на сетях Петри (включая STG), была установлена в [27] используя теорию регионов (см. [28] ). Теория регионов была использована для вывода модели STG и ее схемной реализации в [29] для противоточного конвейерного процессора Роберта Спроулла , Ивана Сазерленда и Чарльза Молнара . [30]

Одной из моделей, тесно связанных с СТГ, являются «Диаграммы изменений», предложенные Михаилом Кишиневским, Алексом Кондратьевым, Александром Таубиным и Виктором Варшавским . [31] Преимущество диаграмм изменений состоит в том, что они позволяют компактно моделировать причинно-следственные связи И и ИЛИ. Но им не хватает описательной силы с точки зрения выбора. Сравнение сетей Петри и диаграмм изменений с точки зрения их описательной силы и их объединения в форме причинно-логических сетей было представлено в . [32]

Ссылки на языки описания оборудования

[ редактировать ]STG были связаны с различными HDL, см., например, ссылки с VHDL. [33] (1996) и Верилог [34] (2000) с целью поддержки асинхронного проектирования. Помещенные в поток синтеза из VHDL, STG и сети Петри оказались полезными, [35] и то же самое с Verilog, [36] где был разработан инструмент VERISYN. [37]

Совсем недавно STG были связаны с обозначениями, которые считаются более простыми для практических разработчиков аппаратного обеспечения, что привело к появлению модели графов перехода формы волны (WTG). [38] Аналогичным образом, понимая, что модель конечного автомата (FSM) может быть проще для проектировщиков, чем, например, сети Петри или STG, связь с автоматами пакетного режима [39] как интерфейс был разработан. [40]

Методы анализа

[ редактировать ]На данный момент, пожалуй, наиболее эффективные методы анализа и синтеза асинхронных схем основаны на развертках сетей Петри — их исследовал Виктор Хоменко в своей кандидатской диссертации. [41] Они реализованы в рамках Workcraft. [14]

Анализ производительности некоторых подклассов сетей Петри моделей асинхронных цепей исследовался Айгуо Се и Питером Бирелем. [42]

Синтез асинхронных цепей

[ редактировать ]Исследованы различные проблемы синтеза асинхронных схем по спецификации СТГ. Один из способов их классификации основан на подходах к анализу, используемых для представления пространства состояний спецификации STG, таких как явные пространства состояний, развертывание базовой сети Петри, структурный анализ сетей Петри и прямое отображение (синтаксически-прямая трансляция). ) СТГ. Эти подходы обычно связаны со сложностью алгоритмов синтеза и, следовательно, временем работы инструментов. С другой стороны, некоторые из этих методов накладывают определенные ограничения на класс сетей Петри. Например, явные методы, основанные на пространстве состояний, обычно работают для произвольного типа сети Петри, тогда как некоторые структурные методы требуют, чтобы базовая сеть Петри представляла собой размеченный граф или сеть со свободным выбором.

Полная проблема государственного кодирования

[ редактировать ]Одной из ключевых хорошо известных проблем синтеза схемных реализаций является проблема полного кодирования состояний (CSC). Для решения этой проблемы были разработаны различные методы. [6] [43] [44] [11] Особенно оригинальный способ анализа удовлетворенности CSC основан на понятии отношения связанности или, что то же самое, отношения блокировки, независимо разработанного Алексом Яковлевым. [3] [1] и Питер Ванбекберген. [45] [46] Другой метод использовал теорию регионов , которая соединяет элементы сетей Петри с областями состояний в графах состояний. [47]

Методы синтеза для обнаружения и разрешения CSC на основе частичных порядков и разверток сетей Петри были разработаны Алексом Семеновым. [48] [49] и Виктор Хоменко. [41] [50] Эти методы помогли формализовать и реализовать метод эффективной визуализации проблем CSC на основе ядер CSC. [51] реализовано в Workcraft. [14]

Методы структурного кодирования для синтеза на основе STG были разработаны Хосепом Кармоной. [52]

Синтез в ограниченных логических базисах

[ редактировать ]Важной проблемой синтеза схем, независимых от скорости (или, что эквивалентно , квази-нечувствительных к задержке - QDI) схем является синтез в пределах ограниченной логической базы, например, с использованием ТОЛЬКО логических элементов с ограниченной базой, таких как И и ИЛИ - см., например, работа Алексея Яковлева, [53] где условие E(возбуждения)-постоянства было введено для обеспечения безопасности в реализации, состоящей из двухуровневой логики суммы произведений (SOP) для функций возбуждения и SR-фиксаторов для основных выходных сигналов заданного СТГ. спецификация. Позже работа Алекса Кондратьева и др. [54] обобщил это условие в понятии монотонного покрытия, которое нашло свою реализацию в программных средствах. [13] [14] Более сложной является проблема синтеза в базисах с отрицательными вентилями, И-НЕ и ИЛИ-НЕ. Для этого разработано несколько методов, в основном под руководством Николая Стародубцева. [55] [56]

Разложение СТГ для синтеза

[ редактировать ]Проблема масштабируемости синтеза STG большого размера и необходимость смягчения взрыва пространства состояний решаются с помощью методов, основанных на сжатии STG с учетом структурных свойств базовой сети Петри, таких как способы разделения сети Петри со свободным выбором. в конечные автоматы или маркированные графы [5] - а также подмножества входных сигналов (триггерные события для сигнала). [57]

Другой подход к решению проблемы масштабируемости — прямое сопоставление STG с асинхронными схемами, которое исследовал Данил Соколов. [58]

Синтез из СТГ с арбитражем

[ редактировать ]Особенно сложной проблемой является автоматический синтез асинхронных схем для арбитров, поскольку их спецификация STG будет содержать поведенческие конфликты в базовых сетях Петри. Поведенческие конфликты подразумевают существование непостоянных переходов. При обычной логической реализации таких STG схема будет подвержена опасностям. специальные методы, такие как полуавтоматическое включение переходов сигналов мьютекса с сохранением исходной спецификации. Были разработаны [59] [60] и реализован в Workcraft. [14] [61]

Ссылки

[ редактировать ]- ^ Jump up to: а б «А. Яковлев и А. Петров. Сети Петри и проектирование контроллера параллельной шины. Материалы 11-й Международной конференции по приложениям и теории сетей Петри, Париж, Франция, июнь 1990 г.» (PDF) .

- ^ Л. Я. Розенблюм. "Язык сигнальных графов и его использование для моделирования протоколов информационного обмена и апериодических схем" (PDF) . Всесоюзный семинар Моделирование дискретных управляющих и вычислительных систем, стр. 22-24, 1981 .

- ^ Jump up to: а б Yakovlev, Alex. "Design and Implementation of Asynchronous Communication Protocols in Systems Interfaces" (Проектирование и реализация протоколов асинхронного обмена информацией в межмодульном интерфейсе), PhD thesis (in Russian), 1982" .

- ^ Jump up to: а б Розенблюм, Л.Я.; Яковлев А.В. "Сигнальные графы: от самосинхронных к синхронизированным" (PDF) . Материалы международного семинара по временным сетям Петри, Турин, Италия, июль 1985 г., IEEE CS Press, стр. 199-207 .

- ^ Jump up to: а б Чу, Т.-А. (1 июня 1986 г.). «О моделях проектирования асинхронных цифровых систем СБИС» . Интеграция . 4 (2): 99–113. дои : 10.1016/S0167-9260(86)80002-5 . ISSN 0167-9260 .

- ^ Jump up to: а б Чу, Там-Ань (1987). Синтез самосинхронных СБИС по теоретико-графовым спецификациям (Диссертация). Массачусетский технологический институт. hdl : 1721.1/14794 .

- ^ Яковлев, А.В. (1992). «Об ограничениях и расширениях модели СТГ для проектирования асинхронных схем управления» . Материалы Международной конференции IEEE 1992 года по компьютерному дизайну: СБИС в компьютерах и процессорах . Кембридж, Массачусетс, США: IEEE Comput. Соц. Нажимать. стр. 396–400. дои : 10.1109/ICCD.1992.276300 . ISBN 978-0-8186-3110-8 . S2CID 47325879 .

- ^ Яковлев, Алексей; Кишиневский, Михаил; Кондратьев, Алекс; Лаваньо, Лучано (1994). «ИЛИ причинно-следственная связь: Моделирование и аппаратная реализация» . В Валетте, Роберт (ред.). Применение и теория сетей Петри 1994 . Конспекты лекций по информатике. Том. 815. Берлин, Гейдельберг: Springer. стр. 568–587. дои : 10.1007/3-540-58152-9_31 . ISBN 978-3-540-48462-2 .

- ^ Jump up to: а б Яковлев А.В.; Коелманс, AM; Лаваньо, Л. (1995). «Высокоуровневое моделирование и проектирование логики асинхронного интерфейса (21/1995)» . IEEE Проектирование и тестирование компьютеров . 12 (1): 32–40. дои : 10.1109/54.350688 .

- ^ Яковлев, Александр; Лаваньо, Лучано; Санджованни-Винсентелли, Альберто (ноябрь 1996 г.). «Единая модель графа перехода сигналов для синтеза асинхронных схем управления» . Формальные методы проектирования систем . 9 (3): 139–188. дои : 10.1007/BF00122081 . ISSN 0925-9856 . S2CID 264205433 .

- ^ Jump up to: а б Кортаделла, Дж . ; Кишиневский, М.; Кондратьев А.; Лаваньо, Л.; Яковлев, А. (2002). Логический синтез для асинхронных контроллеров и интерфейсов . Серия Springer в области передовой микроэлектроники. Том. 8. Берлин, Гейдельберг: Springer Berlin Heidelberg. дои : 10.1007/978-3-642-55989-1 . ISBN 978-3-642-62776-7 .

- ^ Лаваньо, Лучано; Санджованни-Винсентелли, Альберто (1993). Алгоритмы синтеза и тестирования асинхронных схем . дои : 10.1007/978-1-4615-3212-5 . ISBN 978-1-4613-6410-8 .

- ^ Jump up to: а б «Petrify: Публикации по теме» .

- ^ Jump up to: а б с д и «Работа» .

- ^ Яковлев, Алекс. «Проектирование арбитров с использованием сетей Петри. Материалы израильского семинара 1995 г. по асинхронным СБИС, Ноф Геноссар, Израиль, март 1995 г., Центр системных исследований СБИС, Технион, Хайфа, Израиль, стр. 178-201» (PDF) .

- ^ Яковлев А.В.; Коелманс, AM; Семенов А.; Киннимент, диджей (1 декабря 1996 г.). «Моделирование, анализ и синтез асинхронных схем управления с использованием сетей Петри» . Интеграция . 21 (3): 143–170. дои : 10.1016/S0167-9260(96)00010-7 . ISSN 0167-9260 .

- ^ Яковлев А.; Фёрбер, С.; Кренц, Р.; Быстров, А. (июль 2004 г.). «Проектирование и анализ самосинхронной дуплексной системы связи» . Транзакции IEEE на компьютерах . 53 (7): 798–814. дои : 10.1109/TC.2004.26 . ISSN 1557-9956 . S2CID 27216794 .

- ^ Соколов Данил; Хоменко Виктор; Мохов Андрей; Дубихин Владимир; Ллойд, Дэвид; Яковлев, Алексей (май 2020 г.). «Автоматизация проектирования асинхронного логического управления для электроники AMS» . Транзакции IEEE по автоматизированному проектированию интегральных схем и систем . 39 (5): 952–965. дои : 10.1109/TCAD.2019.2907905 . ISSN 1937-4151 . S2CID 133188921 .

- ^ Голубцовы, Станиславы; Мохов Андрей; Быстров, Алекс; Соколов Данил; Яковлев, Алексей (июнь 2019 г.). «Обобщенный асинхронный арбитр» . 2019 19-я Международная конференция по применению параллелизма в проектировании систем (ACSD) . стр. 3–12. дои : 10.1109/ACSD.2019.00005 . ISBN 978-1-7281-3843-5 . S2CID 148566115 .

- ^ Милейко, Сергей (2020). «Совместное проектирование мощных вычислений для надежных широко распространенных приложений Интернета вещей, докторская диссертация, Университет Ньюкасла» (PDF) .

- ^ Ли, Даньхуэй (2021). «Анализ и проектирование преобразователей постоянного тока с переключаемыми конденсаторами с дискретными моделями событий, докторская диссертация, Университет Ньюкасла» (PDF) .

- ^ А. Яковлев и А. Петров и Л. Розенблюм (1993). «Синтез схем асинхронного управления на основе графов перехода символьных сигналов, методологии асинхронного проектирования, 1993» (PDF) .

- ^ Ванбекберген, П.; Гуссенс, Г.; Де Ман, Х. (1992). «Спецификация и анализ временных ограничений в графах перехода сигналов» . [1992] Материалы Европейской конференции по автоматизации проектирования . Брюссель, Бельгия: IEEE Comput. Соц. Нажимать. стр. 302–306. дои : 10.1109/EDAC.1992.205943 . ISBN 978-0-8186-2645-6 . S2CID 61935560 .

- ^ Кортаделла, Хорди ; Кишиневский, Михаил; Кондратьев, Алекс; Лаваньо, Лучано; Таубин, Александр; Яковлев, Алексей (1998). «Ленивые переходные системы» . Материалы международной конференции IEEE/ACM 1998 года по автоматизированному проектированию - ICCAD '98 . Сан-Хосе, Калифорния, США: ACM Press. стр. 324–331. дои : 10.1145/288548.288633 . hdl : 2117/133832 . ISBN 978-1-58113-008-9 . S2CID 12302564 .

- ^ Стивенс, К.; Гиносар, Р.; Ротем, С. (1999). «Относительное время» . Слушания. Пятый международный симпозиум по перспективным исследованиям в области асинхронных цепей и систем . Барселона, Испания: IEEE Comput. Соц. стр. 208–218. дои : 10.1109/ASYNC.1999.761535 . ISBN 978-0-7695-0031-7 . S2CID 195352018 .

- ^ Кишиневский, Михаил; Кортаделла, Хорди ; Кондратьев, Алекс; Лаваньо, Лучано; Таубин, Александр; Яковлев, Алексей (1997). «Соединение асинхронности и прерываний: размещение сетей диаграмм» . В Аземе, Пьер; Бальбо, Джанфранко (ред.). Применение и теория сетей Петри 1997 . Конспекты лекций по информатике. Том. 1248. Берлин, Гейдельберг: Springer. стр. 328–347. дои : 10.1007/3-540-63139-9_44 . ISBN 978-3-540-69187-7 .

- ^ Кортаделла, Дж . ; Кишиневский, М.; Лаваньо, Л.; Яковлев, А. (август 1998 г.). «Вывод сетей Петри из конечных систем переходов» . Транзакции IEEE на компьютерах . 47 (8): 859–882. дои : 10.1109/12.707587 . hdl : 2117/125784 . S2CID 2128502 .

- ^ Бадуэль, Эрик; Дарондо, Филипп (1998). «Теория регионов». В Райзиге, Вольфганг; Розенберг, Гжегож (ред.). Лекции по сетям Петри I: базовые модели . Конспекты лекций по информатике. Берлин, Гейдельберг: Springer. стр. 529–586. дои : 10.1007/3-540-65306-6_22 . ISBN 978-3-540-49442-3 .

- ^ Яковлев, Александр (1 января 1998 г.). «Проектирование логики управления для противоточного конвейерного процессора с использованием сетей Петри». Формальные методы проектирования систем . 12 (1): 39–71. дои : 10.1023/А:1008649930696 . ISSN 1572-8102 . S2CID 14497213 .

- ^ Спроролл, РФ; Сазерленд, IE; Молнар, CE (осень 1994 г.). «Архитектура процессора конвейерного противотока» . IEEE Проектирование и тестирование компьютеров . 11 (3): 48–. дои : 10.1109/MDT.1994.303847 . ISSN 1558-1918 . S2CID 26434994 .

- ^ М.А. Кишиневский (1994). Параллельное оборудование: теория и практика самосинхронного проектирования . Чичестер: Уайли. ISBN 0-471-93536-0 . OCLC 28889359 .

- ^ Яковлев, Александр; Кишиневский, Михаил; Кондратьев, Алекс; Лаваньо, Лучано; Пьеткевич-Кутны, Марта (1 ноября 1996 г.). «О моделях поведения асинхронных схем с причинностью ИЛИ». Формальные методы проектирования систем . 9 (3): 189–233. дои : 10.1007/BF00122082 . ISSN 1572-8102 . S2CID 7456859 .

- ^ Стародубцев Н.; Яковлев А.; Петров С. «Использование среды VHDL для интерактивного синтеза асинхронных схем» (PDF) . Университет Ньюкасла .

- ^ Блунно, Иван; Лаваньо, Лучано (2000), Яковлев, Алекс; Гомес, Луис; Лаваньо, Лучано (ред.), «Получение графиков перехода сигналов на основе поведенческого Verilog HDL» , «Проектирование оборудования и сети Петри» , Бостон, Массачусетс: Springer US, стр. 151–170, doi : 10.1007/978-1-4757-3143- 9_8 , ISBN 978-1-4419-4969-1 , получено 30 мая 2022 г.

- ^ Шан, Д.; Бернс, Ф.; Коелманс, А.; Яковлев А.; Ся, Ф. (1 мая 2004 г.). «Асинхронный системный синтез на основе прямого отображения с использованием VHDL и сетей Петри» . Труды IEE - Компьютеры и цифровая техника . 151 (3): 209–220. дои : 10.1049/ip-cdt:20040525 . ISSN 1359-7027 . S2CID 62708582 .

- ^ Бернс, Ф.; Шан, Д.; Коелманс, А.; Яковлев, А. (2004). «Набор инструментов асинхронного синтеза с использованием Verilog» . Материалы конференции и выставки «Проектирование, автоматизация и испытания в Европе» . Париж, Франция: IEEE Comput. Соц. стр. 724–725. дои : 10.1109/ДАТА.2004.1268948 . ISBN 978-0-7695-2085-8 . S2CID 9219686 .

- ^ «Инструмент асинхронного синтеза высокого уровня (VERISYN)» .

- ^ Кортаделла, Хорди ; Морено, Альберто; Соколов Данил; Яковлев, Алексей; Ллойд, Дэвид (2017). «Графики перехода формы волны: удобный для разработчиков формализм для асинхронного поведения» . 2017 23-й Международный симпозиум IEEE по асинхронным схемам и системам (ASYNC) . IEEE. стр. 73–74. дои : 10.1109/ASYNC.2017.24 . hdl : 2117/114897 . ISBN 978-1-5386-2749-5 . S2CID 5836204 .

- ^ Новик, Стив. «Автоматический синтез асинхронных контроллеров пакетного режима (кандидатская диссертация)» (PDF) .

- ^ Чан, Алекс; Соколов Данил; Хоменко Виктор; Ллойд, Дэвид; Яковлев, Алекс (01.02.2021). «Синтез схем SI на основе спецификаций пакетного режима». Конференция и выставка «Проектирование, автоматизация и испытания в Европе» 2021 (ДАТА) . Гренобль, Франция: IEEE. стр. 366–369. дои : 10.23919/ДАТА51398.2021.9474117 . ISBN 978-3-9819263-5-4 . S2CID 236150734 .

- ^ Jump up to: а б Хоменко, Виктор (2003). Проверка моделей на основе префиксов разверток сети Петри, кандидатская диссертация (PDF) . Университет Ньюкасла.

- ^ Се, Айго; Берел, Питер А. (2000). «Анализ производительности асинхронных схем и систем с использованием стохастических синхронизированных сетей Петри». Яковлев, Алекс; Гомес, Луис; Лаваньо, Лучано (ред.). Проектирование аппаратуры и сети Петри . Бостон, Массачусетс: Springer US. стр. 239–268. дои : 10.1007/978-1-4757-3143-9_13 . ISBN 978-1-4757-3143-9 .

- ^ Лаваньо, Л.; Луна, CW; Брайтон, РК; Санджованни-Винсентелли, А. (1992). «Решение задачи о назначении состояний графов переходов сигналов» . [1992] Материалы 29-й конференции по автоматизации проектирования ACM/IEEE . Анахайм, Калифорния, США: IEEE Comput. Соц. Нажимать. стр. 568–572. дои : 10.1109/DAC.1992.227821 . ISBN 978-0-8186-2822-1 . S2CID 17410812 .

- ^ Ванбекберген, Питер; Лин, Билл; Гуссенс, Герт; Де Ман, Хьюго (1994). «Обобщенная теория присваивания состояний для преобразований на графах перехода сигналов». В Мэн, Тереза Х.; Малик, Шарад (ред.). Проектирование асинхронных схем для обработки сигналов СБИС . Бостон, Массачусетс: Springer US. стр. 101–115. дои : 10.1007/978-1-4615-2794-7_8 . ISBN 978-1-4615-2794-7 .

- ^ Ванбекберген, П.; Кэттур, Ф.; Гуссенс, Г.; Де Ман, Х. (1990). «Оптимизированный синтез асинхронных схем управления на основе теоретико-графовых спецификаций» . 1990 Международная конференция IEEE по компьютерному проектированию. Сборник технических статей . Санта-Клара, Калифорния, США: IEEE Comput. Соц. Нажимать. стр. 184–187. дои : 10.1109/ICCAD.1990.129875 . ISBN 978-0-8186-2055-3 .

- ^ Ванбекберген, П.; Гуссенс, Г.; Кэттур, Ф.; Де Ман, HJ (ноябрь 1992 г.). «Оптимизированный синтез асинхронных схем управления на основе теоретико-графовых спецификаций» . Транзакции IEEE по автоматизированному проектированию интегральных схем и систем . 11 (11): 1426–1438. дои : 10.1109/43.177405 . S2CID 32318274 .

- ^ Кортаделла, Дж.; Кишиневский, М.; Кондратьев А.; Лаваньо, Л.; Яковлев А. (август 1997 г.). «Региональная теория назначения состояний в схемах, независимых от скорости» . Транзакции IEEE по автоматизированному проектированию интегральных схем и систем . 16 (8): 793–812. дои : 10.1109/43.644602 . hdl : 2117/125782 .

- ^ Семенов А.; Яковлев А.; Пастор Э.; Пена, Массачусетс; Кортаделла, Дж . ; Лаваньо, Л. (1997). «Подход на основе частичного порядка к синтезу скоростно-независимых схем» . Труды Третьего международного симпозиума по перспективным исследованиям в области асинхронных цепей и систем . Эйндховен, Нидерланды: IEEE Comput. Соц. Нажимать. стр. 254–265. дои : 10.1109/ASYNC.1997.587179 . hdl : 2117/129959 . ISBN 978-0-8186-7922-3 . S2CID 7883418 .

- ^ Семенов., Алексей (1997). Верификация и синтез асинхронных схем управления с использованием разверток сети Петри (Диссертация). Университет Ньюкасла.

- ^ Хоменко, Виктор (июль 2009 г.). «Эффективное автоматическое разрешение конфликтов кодирования с использованием развертываний STG» . Транзакции IEEE в системах очень большой интеграции (VLSI) . 17 (7): 855–868. дои : 10.1109/TVLSI.2008.2012156 . ISSN 1063-8210 . S2CID 62773126 .

- ^ Мадалински, А.; Быстров А.; Хоменко В.; Яковлев, А. (2003). «Визуализация и разрешение конфликтов кодирования при проектировании асинхронных схем» . Труды IEE - Компьютеры и цифровая техника . 150 (5): 285. doi : 10.1049/ip-cdt:20030831 .

- ^ Кармона, Дж.; Кортаделла, Дж . ; Пастор Э. (2001). «Техника структурного кодирования для синтеза асинхронных схем» . Материалы Второй международной конференции по применению параллелизма в проектировании систем . Ньюкасл-апон-Тайн, Великобритания: IEEE Comput. Соц. стр. 157–166. дои : 10.1109/CSD.2001.981773 . hdl : 2117/133434 . ISBN 978-0-7695-1071-2 . S2CID 16280258 .

- ^ Яковлев, А.В. (1993). «Синтез безопасных асинхронных цепей по обобщенным графам перехода сигналов» . Шестая международная конференция по проектированию СБИС . Бомбей, Индия: IEEE. стр. 21–24. дои : 10.1109/ICVD.1993.669629 . ISBN 978-0-8186-3180-1 . S2CID 10434495 .

- ^ Кондратьев, Алекс; Кишиневский, Михаил; Лин, Билл; Ванбекберген, Питер; Яковлев, Алекс (6 июня 1994 г.). «Базовая реализация схем, независимых от скорости». Материалы 31-й ежегодной конференции по автоматизации проектирования - DAC '94 . Нью-Йорк, штат Нью-Йорк, США: Ассоциация вычислительной техники. стр. 56–62. дои : 10.1145/196244.196275 . ISBN 978-0-89791-653-0 . S2CID 10431976 .

- ^ Стародубцев Н.; Быстров С.; Гончаров М.; Клочков И.; Смирнов, А. (2001). «К синтезу монотонных асинхронных схем по графам переходов сигналов» . Материалы Второй международной конференции по применению параллелизма в проектировании систем . Ньюкасл-апон-Тайн, Великобритания: IEEE Comput. Соц. стр. 179–188. дои : 10.1109/CSD.2001.981775 . ISBN 978-0-7695-1071-2 . S2CID 39407927 .

- ^ Стародубцев Н.; Быстров С.; Яковлев, А. (2003). «Монотонные схемы с полным подтверждением» . Девятый международный симпозиум по асинхронным схемам и системам, 2003 г. Материалы . Ванкувер, Британская Колумбия, Канада: IEEE Comput. Соц. стр. 98–108. дои : 10.1109/ASYNC.2003.1199170 . ISBN 978-0-7695-1898-5 . S2CID 704120 .

- ^ Хоменко Виктор; Шефер, Марк; Фоглер, Уолтер; Волловски, Ральф (01 октября 2009 г.). «Стратегии декомпозиции STG в сочетании с развертыванием». Акта Информатика . 46 (6): 433–474. дои : 10.1007/s00236-009-0102-y . ISSN 1432-0525 . S2CID 9955410 .

- ^ Соколов Данил; Быстров, Александр; Яковлев, Алекс (июнь 2007 г.). «Прямое отображение асинхронных контроллеров с малой задержкой из STG» . Транзакции IEEE по автоматизированному проектированию интегральных схем и систем . 26 (6): 993–1009. дои : 10.1109/TCAD.2006.884416 . ISSN 0278-0070 . S2CID 6811851 .

- ^ Кортаделла, Дж . ; Лаваньо, Л.; Ванбекберген, П.; Яковлев, А. (1994). «Проектирование асинхронных схем на основе поведенческих спецификаций с внутренними конфликтами» . Материалы симпозиума IEEE 1994 года по перспективным исследованиям в области асинхронных схем и систем . Солт-Лейк-Сити, Юта, США: IEEE Comput. Соц. Нажимать. стр. 106–115. дои : 10.1109/ASYNC.1994.656296 . hdl : 2117/128605 . ISBN 978-0-8186-6210-2 . S2CID 14524732 .

- ^ Лоу, Канзас; Яковлев, А. (1995). «Арбитры Token Ring: упражнение по проектированию асинхронной логики с использованием сетей Петри» (PDF) . Университет Ньюкасла .

- ^ Соколов Данил; Хоменко Виктор; Яковлев, Алексей; Ллойд, Дэвид (май 2018 г.). «Проектирование и проверка независимых от скорости схем с арбитражем в Workcraft» . 2018 24-й Международный симпозиум IEEE по асинхронным схемам и системам (ASYNC) . стр. 30–31. дои : 10.1109/ASYNC.2018.00017 . ISBN 978-1-5386-5883-3 . S2CID 57192066 .