WD16

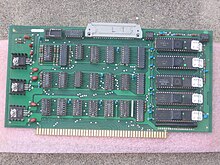

Микропроцессор WD16 в пяти 40-контактных корпусах установлен на плате процессора Alpha Microsystems AM-100, которая подключается к шине S-100 . | |

| Общая информация | |

|---|---|

| Запущен | 1976 год |

| Общий производитель | |

| Производительность | |

| Макс. процессора Тактовая частота | до 3,3 МГц |

| Ширина данных | 16 |

| Ширина адреса | 16 |

| Архитектура и классификация | |

| Набор инструкций | PDP-11 вроде |

| Количество инструкций | 119 |

| Физические характеристики | |

| Упаковка |

|

| История | |

| Преемник | никто |

WD16 , — это 16-битный микропроцессор представленный Western Digital в октябре 1976 года. Он основан на наборе микросхем MCP-1600 , конструкции общего назначения, которая также использовалась для реализации DEC LSI-11 начального уровня миникомпьютера и Pascal MicroEngine. процессор. Эти три системы различались в первую очередь своим микрокодом , что давало каждой системе уникальную архитектуру набора команд (ISA).

WD16 реализует расширение архитектуры набора команд PDP-11 , но несовместим с машинным кодом PDP-11. [1] Набор инструкций и микрокодирование были созданы Диком Уилкоксом и Ричем Нотари. [2] WD16 является примером ортогональной CISC-архитектуры . Большинство инструкций с двумя операндами могут работать с памятью-памятью в любом режиме адресации, а некоторые инструкции могут выполнять до десяти обращений к памяти.

WD16 реализован в пяти 40-контактных DIP- корпусах. Максимальная тактовая частота составляет 3,3 МГц. Его интерфейс с памятью осуществляется через 16-битную мультиплексированную шину данных/адреса. [3]

WD16 наиболее известен благодаря использованию в Alpha Microsystems . процессорных платах AM-100 и AM-100/T компании [4] Прототип был продемонстрирован в 1977 году. [5] По состоянию на 1981 год насчитывалось не менее 5000 компьютеров Alpha Micro на базе WD16. [6] Еще в 1982 году Alpha Micro на базе WD16 все еще характеризовались как «супермикро». [7] На смену WD16 пришла Motorola 68000 в июне 1982 года. [8]

Память

[ редактировать ]Форматы данных

[ редактировать ]Наименьшая единица адресной и записываемой памяти — 8-битный байт . Байты также могут храниться в нижней половине регистров от R0 до R5. [9]

16-битные слова хранятся с прямым порядком байтов, причем младшие байты располагаются по младшему адресу. Слова всегда выравниваются по четным адресам памяти. Слова могут храниться в регистрах от R0 до R7.

32-битные двойные слова могут храниться только в парах регистров, причем младшее слово хранится в регистре с меньшим номером. 32-битные значения используются командами MUL, DIV и некоторыми инструкциями вращения и арифметического сдвига.

Значения с плавающей запятой имеют длину 48 бит и могут храниться только в памяти. Этот формат находится на полпути между форматами с плавающей запятой одинарной и двойной точности. Они хранятся в необычном формате с порядком байтов, который иногда называют «PDP-endian». Значения с плавающей запятой всегда выравниваются по четным адресам. Первое слово содержит знак, показатель степени и старший байт мантиссы. Следующий более высокий адрес содержит два средних байта мантиссы, а следующий более высокий адрес содержит два младших байта мантиссы. Полный формат выглядит следующим образом:

1. 1-битный знак для всего числа, который равен нулю для положительного значения.

2. 8-битная экспонента с основанием двойки в обозначении с избытком 128 и диапазоном +127, -128. Единственное допустимое число с показателем -128 — это истинный ноль (все нули).

3. 40-битная мантисса со старшим битом.

| 15 | 14 | 7 | 6 | 0 | ||||||||||||

| Адрес+0 | С | Экспонента | Мантисса (высокая) | |||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Адрес+2 | Мантисса | (середина) | ||||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Адрес+4 | Мантисса | (низкий) | ||||||||||||||

Управление памятью

[ редактировать ]16-битные адреса WD16 могут напрямую обращаться к 64 КБ памяти. WD16 не обеспечивает никакого управления памятью или ее защиты. В приложении AM-100 последние 256 ячеек памяти отображаются в пространство портов . [10] Поскольку большинство компьютеров AM-100 использовались как многопользовательские компьютеры, память обычно расширялась до 64 КБ за счет переключения банков . Хотя AM-100 можно было настроить на 22 пользователя и 512 килобайт оперативной памяти, [6] типичная конфигурация памяти для AM-100 на 9 пользователей может находиться в диапазоне 352 килобайт. [11] В 1981 году для AM-100/T был предложен дополнительный блок управления памятью AM-700, который позволял сегментировать память с шагом 256 байт. [12]

Регистры ЦП

[ редактировать ]

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ЦП содержит восемь 16-битных регистров общего назначения , от R0 до R7. Регистры могут использоваться для любых целей, за исключением следующих: Регистр R7 — счетчик программ (ПК). Хотя в качестве указателя стека можно использовать любой регистр, R6 — это указатель стека (SP), используемый для аппаратных прерываний и прерываний. R0 — это счетчик инструкций блочной передачи. [9]

Режимы адресации

[ редактировать ]Большинство инструкций выделяют шесть бит для определения каждого операнда. Три бита выбирают один из восьми режимов адресации, а три бита выбирают регистр общего назначения. Кодировка режима адресации шестибитного операнда следующая: [9]

| 5 | 3 | 2 | 0 | ||

| Режим | Зарегистрироваться | ||||

В следующих разделах каждый элемент содержит пример того, как операнд будет записан на языке ассемблера. Rn означает один из восьми регистров, записанных от R0 до R7.

Общие режимы адресации регистров

[ редактировать ]Следующие восемь режимов могут быть применены к любому регистру общего назначения. Их эффекты при применении к R6 (указатель стека, SP) и R7 (счетчик программ, ПК) изложены отдельно в следующих разделах.

| Код | Имя | Пример | Описание |

|---|---|---|---|

| 0н | Зарегистрироваться | Рн | Операнд находится в Rn |

| 1н | Регистрация отложена | (Рн) | Rn содержит адрес операнда |

| 2н | Автоинкремент | (Рн)+ | Rn содержит адрес операнда, затем увеличиваем Rn |

| 3н | Автоинкремент отложен | @(Rn)+ | Rn содержит адрес адреса операнда, затем увеличиваем Rn на 2 |

| 4н | Автодекремент | −(Rn) | Уменьшите Rn, затем используйте результат как адрес операнда. |

| 5н | Автоуменьшение отложено | @−(Rn) | Уменьшите Rn на 2, затем используйте результат как адрес адреса операнда. |

| 6н | Индекс | Х(Рн) | Rn+X — адрес операнда |

| 7н | Индекс отложен | @X(Rn) | Rn+X — адрес адреса операнда |

В индексном и индексном режимах с отсрочкой X представляет собой 16-битное значение, взятое из второго слова инструкции. В инструкциях с двумя операндами оба операнда могут использовать эти режимы. Такие инструкции состоят из трех слов.

Операции автоинкремента и автодекремента над регистром выполняются на 1 в байтовых инструкциях, на 2 в словесных инструкциях и на 2 всякий раз, когда используется отложенный режим, поскольку величина, к которой обращается регистр, является указателем (словом).

Режимы адресации счетчика программ

[ редактировать ]Когда указан R7 (счетчик программ), четыре режима адресации естественным образом дают полезные эффекты:

| Код | Имя | Пример | Описание |

|---|---|---|---|

| 27 | Немедленный | #н | Операнд — это следующее слово инструкции. |

| 37 | Абсолютный | @#а | Адрес операнда — это следующее слово инструкции. |

| 67 | Родственник | а | Адрес операнда — это следующее слово инструкции, добавляемой в ПК. |

| 77 | Относительная отсрочка | @а | Адрес адреса операнда — это следующее слово инструкции, добавляемой в ПК. |

Есть только два распространенных варианта использования абсолютного режима, синтаксис которых сочетает в себе немедленный и отложенный режимы. Первый — доступ к зарезервированным ячейкам процессора по адресам 0000–003F. Другой способ — указать регистры ввода/вывода в пространстве портов, поскольку регистры каждого устройства имеют определенные адреса памяти. Относительный режим имеет более простой синтаксис и более типичен для обращения к программным переменным и местам перехода. Программа, которая использует относительный режим (и относительный отложенный режим) исключительно для внутренних ссылок, не зависит от позиции ; он не содержит никаких предположений о своем собственном местоположении, поэтому его можно загрузить в произвольную ячейку памяти или даже переместить без необходимости корректировки его адреса с учетом его местоположения. При вычислении таких адресов относительно текущего местоположения процессор выполняет перемещение « на лету».

Немедленный и абсолютный режимы — это просто режим автоинкремента и отложенный режим автоинкремента соответственно, применяемые к ПК. Когда в инструкции присутствует вспомогательное слово, компьютер для следующей инструкции автоматически увеличивается после вспомогательного слова. Поскольку ПК всегда указывает на слова, операция автоинкремента всегда выполняется с шагом 2.

Режимы адресации стека

[ редактировать ]R6, также называемый SP, используется в качестве аппаратного стека для ловушек и прерываний. Соглашение, реализуемое набором режимов адресации, предоставляемых WD16, заключается в том, что стек увеличивается вниз — в сторону более низких адресов — по мере того, как в него помещаются элементы. Когда режим применяется к SP или к любому регистру, который программист решает использовать в качестве программного стека, режимы адресации имеют следующие эффекты:

| Код | Имя | Пример | Описание |

|---|---|---|---|

| 16 | Отложенный | (СП) | Операнд находится на вершине стека |

| 26 | Автоинкремент | (СП)+ | Операнд находится на вершине стека, затем извлеките его |

| 36 | Автоинкремент отложен | @(СП)+ | Указатель на операнд находится на вершине стека; убрать указатель |

| 46 | Автодекремент | −(СП) | Поместить значение в стек |

| 66 | Индексировано | Х(СП) | Операнд расположен на расстоянии X от вершины стека. |

| 76 | Индексированные отложенные | @X(СП) | Указатель на операнд расположен на расстоянии X от вершины стека. |

Хотя программные стеки могут содержать байты, SP всегда указывает на стек слов. Операции автоинкремента и автодекремента на SP всегда выполняются с шагом 2.

Набор инструкций

[ редактировать ]Большинство инструкций WD16 оперируют байтами и словами. Байты задаются номером регистра, определяющим младший байт регистра, или ячейкой памяти. Слова задаются номером регистра или ячейкой памяти младшего байта, который должен быть четным числом. Все коды операций и адреса выражаются в шестнадцатеричном формате . [9]

Инструкции с двойным операндом

[ редактировать ]Четыре старших бита определяют операцию, которую необходимо выполнить. Две группы по шесть бит определяют режим адресации исходного операнда и режим адресации операнда-адресата, как определено выше. Эта группа инструкций занимает 75% доступных кодов операций.

| 15 | 12 | 11 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||

| Код операции | источник | Зарегистрироваться | рука | Зарегистрироваться | |||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 1000 | ДОБАВЛЯТЬ | Добавлять: Dest ← Dest + Src

|

| 2000 | СУБ | Вычесть: Dest ← Dest - Src

|

| 3000 | И | И: Dest ← Dest ∧ Src

|

| 4000 | БИК | Немного ясно: Dest ← Dest ∧ (-1 - Src)

|

| 5000 | ДО | Набор бит: Dest ← Dest ∨ Src

|

| 6000 | БЕСПЛАТНО | Эксклюзив или: Dest ← Dest ⊻ Src

|

| 9000 | КМП | Сравнивать: Set-flags(Src − Dest)

|

| А000 | КУСОЧЕК | Битовый тест: Set-flags(Dest ∧ Src)

|

| В000 | МОВ | Двигаться: Dest ← Src

|

| С000 | ЦМПБ | Сравнить байт: Set-flags(Src − Dest)

|

| Д000 | МОВБ | Переместить байт: Dest ← Src (Знак места назначения регистра расширяется до битов 8–15)

|

| Е000 | БИСБ | Бит установки байта: Dest ← Dest ∨ Src

|

Некоторые инструкции с двумя операндами используют режим адресации для одного операнда и регистр для второго операнда:

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Код операции | Рег | Исходный/назначенный адрес | Зарегистрироваться | ||||||||||||

Семь старших битов определяют выполняемую операцию, шесть битов определяют режим адресации операнда, а три бита определяют регистр или пару регистров. Если используется пара регистров (ниже записанная как «Reg+1:Reg»), Reg содержит младшую часть операнда. Следующий регистр с более высоким номером содержит старшую часть операнда (или остаток).

| Код операции | Мнемоника | Операция |

|---|---|---|

| 7200 | ЧТО | Загрузить эффективный адрес: Reg ← ea(Dest)

|

| 73C0 | СПМ | Прыжок: PC ← ea(Dest) (Это то же самое, что LEA PC,Dest и использует один и тот же код операции.)

|

| 7400 | ПЕПЕЛ | Арифметический сдвиг: if Src < 0 then Reg ← Shift-right(Reg, -Src) else Reg ← Shift-left(Reg, Src)

|

| 7800 | ХЧ | Обмен: Reg ↔ Src

|

| 7А00 | АШК | Комбинированный арифметический сдвиг (32 бита): if Src < 0 then (Reg+1:Reg) ← Shift-right((Reg+1:Reg), -Src) else (Reg+1:Reg) ← Shift-left((Reg+1:Reg), Src)

|

| 7C00 | У меня есть | Умножить: (Reg+1:Reg) ← Reg × Src

|

| 7E00 | ДИВ | Разделять: Compute (Reg+1:Reg) ÷ Src; Reg ← quotient; Reg+1 ← remainder

|

Инструкции с одним операндом

[ редактировать ]Старшие десять битов определяют операцию, которую необходимо выполнить, а бит 15 обычно выбирает адресацию байтов или слов. Одна группа из шести битов определяет операнд, как определено выше.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Код операции | Исходный/назначенный адрес | Зарегистрироваться | |||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0BC0 | ТАМПОН | Поменять местами байты слова: Dest ← (Dest × 256) ∨ (Dest ÷ 256)

|

| 8BC0 | СВАД | Поменять местами цифры байта: Dest ← (Dest × 16) ∨ (Dest ÷ 16)

|

| 0840 | среда CLR | Прозрачный: Dest ← 0

|

| 8840 | CLRB | |

| 0C00 | С | Дополнение: Dest ← (-1 - Dest)

|

| 8C00 | ГРЕБЕНЬ | |

| 0С80 | ИНК | Приращение: Dest ← Dest + 1

|

| 8С80 | МККН | |

| 0CC0 | Декабрь | Декремент: Dest ← Dest − 1

|

| 8CC0 | ДЕЦБ | |

| 0С40 | НЕГ | Отрицать: Dest ← -Dest

|

| 8С40 | НЭГБ | |

| 0B00 | НАБОР | Набор: Dest ← -1

|

| 8B00 | СЕТБ | |

| 0А80 | ТСТ | Тест: Set-flags(Src)

|

| 8А80 | ЦТБ | |

| 0A00 | РОР | Поворот вправо: Dest:Cflag ← Rotate-right(Dest:Cflag, 1)

|

| 8А00 | РОРБ | |

| 0А40 | РОЛЬ | Поворот влево: Cflag:Dest ← Rotate-left(Cflag:Dest, 1)

|

| 8А40 | РОЛБ | |

| 0Б80 | АСР | Арифметический сдвиг вправо: Dest ← Dest ÷ 2, sign preserved

|

| 8Б80 | АСРБ | |

| 0AC0 | АСЛ | Арифметический сдвиг влево: Dest ← Dest × 2

|

| 8AC0 | АСЛБ | |

| 8Д80 | АЦП | Добавить перенос: Dest ← Dest + Cflag

|

| 8DC0 | СБК | Вычесть перенос: Dest ← Dest - Cflag

|

| 0D00 | ИВ2 | Увеличить слово на 2: Dest ← Dest + 2

|

| 0DC0 | ТJMP | Прыжок с таблицы: PC ← PC + (Dest), PC ← PC + @PC

|

| 0D80 | TCALL | Планируемый звонок: -(SP) ← PC, PC ← PC + (Dest), PC ← PC + @PC

|

| 0D40 | SXT | Знак расширения: if N flag = 1 then Dest ← -1 else Dest ← 0

|

| 8D00 | ЛСТС | Состояние процессора загрузки: PSW ← Dest

|

| 8Д40 | ССТС | Сохранить статус процессора: Dest ← PSW

|

Короткие инструкции немедленного действия с одним операндом

[ редактировать ]Старшие семь битов, а также биты 5 и 4 определяют операцию, которую необходимо выполнить. Одна группа из трех битов определяет регистр. Четырехбитное поле счетчика содержит небольшое непосредственное значение или счетчик. Во всех случаях к этому полю добавляется единица, составляющая диапазон от 1 до 16.

| 15 | 9 | 8 | 6 | 5 | 4 | 3 | 0 | ||||||||

| Код операции | Рег | На | Считать | ||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0800 | АДДИ | Добавить немедленно: Reg ← Reg + Count + 1

|

| 0810 | СУБИ | Вычесть немедленно: Reg ← Reg - Count - 1

|

| 0820 | ВЕЛОСИПЕДЫ | Немного ясно сразу: Reg ← Reg ∧ (-1 - (Count+1))

|

| 0830 | ДВИГАТЬСЯ | Немедленно двигаться: Reg ← Count + 1

|

| 8800 | СССРР | Повернуть вправо несколько раз: Reg:C-flag ← Rotate-right(Reg:C-flag, Count+1)

|

| 8810 | SSLR | Поворот влево несколько раз: C-flag:Reg ← Rotate-left(C-flag:Reg, Count+1)

|

| 8820 | ССРА | Правый арифметический сдвиг, кратный: Reg:C-flag ← Arithmetic-shift-right(Reg, Count+1)

|

| 8830 | SSLA | Левый арифметический сдвиг, кратный: C-flag:Reg ← Arithmetic-shift-left(Reg, Count+1)

|

| 8E00 | СДРР | Двойной поворот вправо, кратный (33 бита): Reg+1:Reg:C-flag ← Rotate-right(Reg+1:Reg:C-flag, Count+1)

|

| 8Е10 | SDLR | Двойной поворот влево, кратный (33 бита): C-flag:Reg+1:Reg ← Rotate-left(C-flag:Reg+1:Reg, Count+1)

|

| 8Э20 | СДРА | Двойной арифметический сдвиг вправо, кратный (32 бита): Reg:Reg+1:C-flag ← Arithmetic-shift-right(Reg:Reg+1, Count+1)

|

| 8Э30 | SDLA | Двойной арифметический сдвиг влево, кратный (32 бита): C-flag:Reg:Reg+1 ← Arithmetic-shift-left(Reg:Reg+1, Count+1)

|

Инструкции с плавающей запятой

[ редактировать ]Старшие восемь битов определяют операцию, которую необходимо выполнить. Две группы по четыре бита определяют режим адресации источника и места назначения и регистрируют. Если поле I = 0, назначенный регистр содержит адрес операнда, эквивалентный режиму адресации (Rn). Если поле I = 1, назначенный регистр содержит адрес адреса операнда, что эквивалентно режиму адресации @0(Rn).

| 15 | 8 | 7 | 6 | 4 | 3 | 2 | 0 | ||||||||

| Код операции | я | Комфортный | я | Дрег | |||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| Ф000 | ФАДД | Плавающее добавление: Dest ← Dest + Src

|

| Ф100 | ФСУБ | Плавающее вычитание: Dest ← Dest - Src

|

| Ф200 | ФМУЛ | Плавающее умножение: Dest ← Dest × Src

|

| Ф300 | ФДИВ | Плавающее разделение: Dest ← Dest ÷ Src

|

| Ф400 | ФЦМП | Плавающее сравнение: Dest - Src

|

Инструкции по блокировке передачи

[ редактировать ]Старшие десять битов определяют операцию, которую необходимо выполнить. Две группы по три бита определяют регистры источника и назначения. Во всех случаях регистр источника содержит адрес первого слова или байта памяти, подлежащего перемещению, а регистр назначения содержит адрес первого слова или байта памяти, куда принимаются перемещаемые данные. Количество перемещаемых слов или байтов содержится в R0 как целое число без знака. Число варьируется от 1 до 65536. Эти инструкции полностью прерываемы.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Код операции | Комфортный | Дрег | |||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0E00 | БВУ | Переместить блок слов вверх: (DReg) ← (SReg), SReg ← SReg + 2, DReg ← DReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0E40 | МБВД | Переместить блок слов вниз: (DReg) ← (SReg), SReg ← SReg - 2, DReg ← DReg - 2, R0 ← R0 - 1, until R0 = 0

|

| 0E80 | МББУ | Переместить блок байтов вверх: (DReg) ← (SReg), SReg ← SReg + 1, DReg ← DReg + 1, R0 ← R0 - 1, until R0 = 0

|

| 0EC0 | МББД | Переместить блок байтов вниз: (DReg) ← (SReg), SReg ← SReg - 1, DReg ← DReg - 1, R0 ← R0 - 1, until R0 = 0

|

| 0F00 | СОБАКА | Переместить блок слов по адресу: (DReg) ← (SReg), SReg ← SReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0F40 | MBBA | Переместить блок байтов по адресу: (DReg) ← (SReg), SReg ← SReg + 1, R0 ← R0 - 1, until R0 = 0

|

| 0F80 | МИСТЕР | Переместить адрес в блок слов: (DReg) ← (SReg), DReg ← DReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0FC0 | МАББ | Переместить адрес в блок байтов: (DReg) ← (SReg), DReg ← DReg + 1, R0 ← R0 - 1, until R0 = 0

|

Инструкции филиала

[ редактировать ]Старший байт инструкции определяет операцию. Младший байт представляет собой смещение знакового слова относительно текущего положения счетчика программ. Это позволяет использовать прямые и обратные ветвления в коде. Максимальный диапазон ветвления составляет +128, -127 слов из кода операции ветвления.

В большинстве инструкций перехода выбор перехода зависит от состояния кодов условий. Инструкции ветвления обычно предшествует инструкция CMP с двумя операндами (сравнение) или BIT (проверка битов) или инструкция TST с одним операндом (проверка). Арифметические и логические инструкции также устанавливают коды условий. В отличие от процессоров Intel с архитектурой x86 , инструкции MOV также устанавливают их, поэтому можно использовать инструкцию ветвления для перехода в зависимости от того, было ли перемещаемое значение нулевым или отрицательным.

| 15 | 8 | 7 | 0 | ||||||||||||

| Код операции | Компенсировать | ||||||||||||||

| Код операции | Мнемоника | Состояние или эксплуатация |

|---|---|---|

| 0100 | БР | Филиал всегда PC ← PC + (2 × Sign-extend(Offset))

|

| 0200 | БНЕ | Разветвить, если не равно Z = 0

|

| 0300 | ЛЯГУШКА | Разветвить, если равно Z = 1

|

| 0400 | БГЭ | Ветвь, если больше или равно (N ⊻ V) = 0

|

| 0500 | БЛТ | Разветвить, если меньше (N ⊻ V) = 1

|

| 0600 | БГТ | Разветвление, если больше, чем (Z ∨ (N ⊻ V)) = 0

|

| 0700 | БЫТЬ | Разветвление, если меньше или равно (Z ∨ (N ⊻ V)) = 1

|

| 8000 | БПЛ | Ответвление если плюс N = 0

|

| 8100 | ИМТ | Разветвление, если минус N = 1

|

| 8200 | БЫТЬ | Ветвь, если выше (C ∨ Z) = 0

|

| 8300 | БЛОС | Ветвь, если ниже или такая же (C ∨ Z) = 1

|

| 8400 | БВЦ | Ветвь, если переполнение очищено V = 0

|

| 8500 | БВС | Ветвь, если установлено переполнение V = 1

|

| 8600 | BCC или BHIS | Ответвление, если перенос свободен, или ответвление, если выше или такое же C = 0

|

| 8700 | БКС или БЛО | Разветвление, если набор для переноски, или разветвление, если нижнее C = 1

|

Ограниченный диапазон инструкций ветвления означал, что по мере роста кода целевые адреса некоторых ветвей могут стать недоступными. Программист заменял однословную команду Bcc на инструкцию JMP, состоящую из двух слов. Поскольку JMP не имеет условных форм, программист изменит Bcc на противоположный смысл, чтобы разветвиться вокруг JMP.

| 15 | 9 | 8 | 6 | 5 | 0 | ||||||||||

| Код операции | Рег | Компенсировать | |||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 7600 | ПОД | Subtract One and Branch: Reg ← Reg - 1; if Reg ≠ 0 then PC ← PC - (2 × Offset)

|

SOB (вычитание единицы и ветвление) — еще одна инструкция условного перехода. Указанный регистр уменьшается на 1, и если результат не равен нулю, выполняется обратная ветвь на основе смещения 6-битного слова.

Инструкции подпрограммы

[ редактировать ]| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Код операции | Рег | источник | Зарегистрироваться | ||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 7000 | JSR | Переход к подпрограмме: -(SP) ← Reg; Reg ← PC; PC ← Src

|

JSR вызывает подпрограмму. Группа из шести битов определяет режим адресации. Инструкция JSR может сохранить любой регистр в стеке. Программы, которым не нужна эта функция, указывают ПК в качестве регистра (ПК JSR, адрес), и подпрограмма возвращается с использованием ПК RTN. Если подпрограмма была вызвана, например, с помощью «JSR R4, адрес», то старое значение R4 будет сохранено на вершине стека, а адрес возврата (сразу после JSR) будет в R4. Это позволяет подпрограмме получить доступ к значениям, закодированным в строке, указав (R4)+, или к встроенным указателям, указав @(R4)+. Автоинкрементирование проходит мимо этих данных до того момента, когда возобновляется выполнение кода вызывающего объекта. Такая процедура указывает RTN R4 вернуться к вызывающей стороне.

Форма JSR PC,@(SP)+ может использоваться для реализации сопрограмм . Первоначально адрес входа сопрограммы помещается в стек, и с этого момента инструкция JSR PC,@(SP)+ используется как для операторов вызова, так и для операторов возврата. Результатом выполнения этой инструкции JSR является обмен содержимым ПК и верхнего элемента стека, что позволяет двум процедурам поменять местами управление и возобновить работу там, где каждая из них была прервана предыдущей заменой.

| 15 | 3 | 2 | 0 | ||||||||||||

| Код операции | Рег | ||||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0018 | РТН | Возврат из подпрограммы: PC ← Reg; Reg ← (SP)+

|

| 0028 | ПРТН | Вытащить стек и вернуть: SP ← SP + (2 × @SP), PC ← Reg; Reg ← (SP)+

|

PRTN удаляет ряд параметров из стека и возвращает результат. PRTN — это ответ WD16 на сложную инструкцию MARK PDP-11. В отличие от MARK, PRTN выполняется в программном пространстве и может использовать любой регистр в качестве регистра связи. В этом объяснении в качестве связи будет использоваться R5. Сначала вызывающая сторона помещает R5 в стек. Далее в стек можно поместить любое количество словесных аргументов. Затем вызывающая сторона помещает количество слов-аргументов + 1 в R5. Вызывающая сторона выполняет инструкцию JSR R5,address, которая помещает в стек количество слов аргумента + 1, помещает адрес возврата в R5 и переходит к подпрограмме. После выполнения своего кода подпрограмма завершается с PRTN R5. PRTN удваивает число на вершине стека и добавляет его в SP, удаляя параметры. Затем PRTN продолжает, возвращаясь к вызывающему абоненту с эквивалентом RTN R5, загружая R5 в ПК и вставляя R5.

Инструкции по единому регистру

[ редактировать ]Эти инструкции имеют 13-битный код операции и трехбитный аргумент-регистр.

| 15 | 3 | 2 | 0 | ||||||||||||

| Код операции | Рег | ||||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0010 | ИАК | Подтверждение прерывания: Interrupt acknowledge state code, Reg ← Bus read

|

| 0020 | Москва | Маска вне: (002E) ← Reg, Mask out state code

|

Инструкции по подразумеваемым параметрам

[ редактировать ]| 15 | 0 | ||||||||||||||

| Код операции | |||||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0000 | НЕТ | Нет операции: Do nothing

|

| 0001 | ПЕРЕЗАГРУЗИТЬ | Перезагрузить: Transmit reset pulse to I/O devices

|

| 0002 | ОДИН | Разрешение прерываний: I2 ← 1

|

| 0003 | ИДС | Отключение прерываний: I2 ← 0

|

| 0004 | ОСТАНОВКА | Остановка: Executes the selected halt option

|

| 0005 | XCT | Выполните одну инструкцию: PC ← (SP)+, PS ← (SP)+, set trace flag, execute opcode, -(SP) ← PS, -(SP) ← PC, trace flag reset, If no error PC ← (0020) else PC ← (001E)

|

| 0006 | БПТ | Ловушка точки останова: -(SP) ← PS, -(SP) ← PC, PC ← (002C)

|

| 0007 | ВФИ | Дождитесь прерывания: Enable interrupts (I2 ← 1). Bus activity ceases.

|

| 0008 | РСВЦ | Возврат после вызова супервизора (B или C): REST, SP ← SP + 2, RTT

|

| 0009 | РРТТ | Восстановление и возврат из ловушки: REST, RTT

|

| 000А | СОХРАНЯТЬ | Сохраняем регистры: -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0

|

| 000Б | СОБСТВЕННЫЙ | Сохранить статус: SAVE, -(SP) ← (002E), (002E) ← (002E) ∨ Mask, MSKO, IEN. Note Mask is stored in the second word of instruction.

|

| 000С | ОТДЫХ | Восстановить регистры: R0 ← (SP)+, R1 ← (SP)+, R2 ← (SP)+, R3 ← (SP)+, R4 ← (SP)+, R5 ← (SP)+

|

| 000D | РРТН | Восстановить и вернуть: REST, PC ← (SP)+

|

| 000E | РСТС | Восстановить статус: (002E) ← (SP)+, MSKO, REST, RTT

|

| 000F | РТТ | Возвращение из ловушки: PC ← (SP)+, PS ← (SP)+

|

Звонок супервайзера

[ редактировать ]Эти инструкции используются для реализации вызовов операционной системы (супервизора). Все они имеют шестибитный регистровый аргумент. SVCB и SVCC разработаны таким образом, что аргумент операционной системы может использовать большинство режимов адресации, поддерживаемых собственным набором команд.

| 15 | 6 | 5 | 0 | ||||||||||||

| Код операции | Арг | ||||||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0040 | КАЖДЫЙ | Звонок супервайзеру А: -(SP) ← PS ,-(SP) ← PC, PC ← (0022) + Arg × 2, PC ← (PC)

|

| 0080 | СВКБ | Звонок супервайзеру Б: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0024)

|

| 00C0 | СВКК | Вызов супервайзера C: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0026)

|

Операции с кодом условия

[ редактировать ]| 15 | 4 | 3 | 2 | 1 | 0 | ||||||||||

| Код операции | Н | С | V | С | |||||||||||

| Код операции | Мнемоника | Операция |

|---|---|---|

| 0030 | ООО | Коды условий нагрузки: Load according to N, Z, V, C bits

|

Четыре кода состояния в слове состояния процессора (PSW):

- N указывает на отрицательное значение

- Z указывает на нулевое (равное) условие

- V, указывающий состояние переполнения , и

- C указывает на состояние переноса .

Зарезервированные места с нехваткой памяти

[ редактировать ]Ячейки памяти между 0000 и 003F имеют фиксированные функции, определенные процессором. Все адреса ниже являются адресами слов. [9]

| Вектор | Состояние |

|---|---|

| 0000-0010 | R0–R5, SP, ПК и PS для вариантов включения/остановки питания. |

| 0012 | ошибка шины ПК |

| 0014 | невекторное прерывание при сбое питания ПК |

| 0016 | опция включения/остановки питания, восстановление питания ПК |

| 0018 | ошибка четности ПК |

| 001А | зарезервированный код операции ПК |

| 001С | незаконный формат кода операции ПК |

| 001E | Ошибка XCT ПК |

| 0020 | ПК для трассировки XCT |

| 0022 | Адрес таблицы SVCA |

| 0024 | СВКБ ПК |

| 0026 | ПК СВКК |

| 0028 | Адрес таблицы векторных прерываний (I0) |

| 002А | невекторное прерывание (I1) ПК |

| 002C | БПТ ПК |

| 002E | Маска прерывания приоритета ввода-вывода |

| 0030-003C | Блокнот с плавающей запятой |

| 003E | Ошибка с плавающей запятой ПК |

Производительность

[ редактировать ]Скорость процессора WD16 зависит от тактовой частоты, конфигурации памяти, кода операции и режимов адресации. Синхронизация инструкций состоит из трех компонентов: выборки/выполнения самой инструкции и времени доступа к источнику и назначению. Последние два компонента зависят от режима адресации. Например, на частоте 3,3 МГц инструкция формы ADD x (R m ), y (R n ) имеет время выборки/выполнения 3,3 микросекунды плюс исходное время 2,7 микросекунды и время назначения 3,0 микросекунды, для общей команды. время 9,0 микросекунд. Между регистрами ADD R m ,R n выполняется за 3,3 микросекунды. Плавающая точка работает значительно медленнее. Инструкция сложения с плавающей запятой полуторной точности (48 бит) обычно занимает от 54 до 126 микросекунд. Точность WD16 представляет собой компромисс между традиционными поплавками одинарной и двойной точности. [9]

Напротив, самым быстрым компьютером PDP-11 в то время был PDP-11/70. Команда формы ADD x (R m ), y (R n ) имеет время выборки/выполнения 1,35 микросекунды плюс время источника и места назначения 0,6 микросекунды каждое, что дает общее время инструкции 2,55 микросекунды. Любой случай, когда адресованная память не была в кеше, добавляет 1,02 микросекунды. Между регистрами ADD R m ,R n может выполняться из кэша за 0,3 микросекунды. [13] Команда сложения с плавающей запятой одинарной точности, выполняемая сопроцессором FP11-C, может занимать от 0,9 до 2,5 микросекунд плюс время для выборки операндов, которое может достигать 4,2 микросекунды. [14]

Инструкции по передаче блоков WD16 примерно удваивают скорость перемещения и блочного ввода-вывода. Слово переместилось с MOV (R1)+,(R2)+, SOB R0,loop инструкции занимают 9,6 микросекунд на итерацию. MBWU R1,R2 эквивалент занимает 4,8 микросекунды на итерацию.

Ассоциация пользователей компьютеров провела серию тестов на системе на базе AM-100T стоимостью 35 680 долларов США (что эквивалентно 131 941 доллару США в 2023 году). Они обнаружили, что их тест с привязкой к ЦП на AM-100T выполнялся за 31,4 секунды по сравнению с 218 секундами для средней однопользовательской системы в ценовом диапазоне от 15 000 до 25 000 долларов. [15] В группе многопользовательских компьютеров стоимостью от 25 000 до 50 000 долларов AM-100T находился в «верхней трети» по скорости. [16]

В тесте Creative Computing Benchmark, проведенном в мае 1984 года, WD16 (в приложении AM-100T) был поставлен на 34-е место из 183 протестированных машин. Затраченное время составило 10 секунд по сравнению с 24 секундами для IBM PC . [17]

Эмулятор

[ редактировать ]Virtual Alpha Micro — это эмулятор WD16 с открытым исходным кодом. Написанный на языке C, он эмулирует процессор WD16 и аппаратную среду Alpha Micro AM-100. Автор утверждает, что он работает на настольных компьютерах Linux (включая Raspberry Pi), Windows и Macintosh, хотя двоичные файлы не предоставляются. На нем будет работать операционная система Alpha Micro (AMOS) и все связанные с ней программы. В 2002 году Alpha Micro предоставила ограниченное разрешение на распространение двоичных файлов AMOS 4.x или 5.0, включая руководства, только для любительского использования. [18]

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ Флистра, Дэниел (апрель 1977 г.). «Новая система для любителей поддерживает разделение времени» (PDF) . Байт . 2 (4): 142–144 . Проверено 21 ноября 2022 г.

- ^ Уилкокс, Дик (январь 1977 г.). «16-битный микроконтроллер типа PDP-11 для шины S-100» . Журнал доктора Доббса по компьютерной гимнастике и ортодонтии . 2 (1): 3–7 . Проверено 14 июня 2022 г.

- ^ Руководство пользователя микропроцессора MCP-1600 (PDF) . Вестерн Диджитал. 1975 год . Проверено 28 апреля 2022 г.

- ^ Стэн, Вьетнам (май 1983 г.). «Битва дисковых операционных систем» (PDF) . Компьютеры и электроника . 21 (5): 19 . Проверено 8 июня 2023 г.

- ^ Крейг, Джон (апрель 1977 г.). «Вокруг отрасли» (PDF) . Килобод: Журнал Small Computer Magazine (4): 10 . Проверено 23 ноября 2022 г.

- ^ Перейти обратно: а б Ки, Хэнк (август 1981 г.). «Возвращение к системе Alpha Micro» (PDF) . Микросистемы . 2 (4):26 . Проверено 1 марта 2022 г.

- ^ Фокс, Том (январь 1982 г.). «Бизнес-системы 82 года» . Возраст интерфейса . 7 (1):75 . Проверено 3 ноября 2022 г.

- ^ «Альфа Микросистемы делает рекордные продажи» . Инфомир . 4 (44): 11. 8 ноября 1982 г. Проверено 3 ноября 2022 г.

- ^ Перейти обратно: а б с д и ж «Справочное руководство для программиста микрокомпьютера WD16» (PDF) . Вестерн Диджитал . Проверено 10 декабря 2021 г.

- ^ «Техническое руководство АМ-100» (PDF) . Альфа Микросистемс . Проверено 19 декабря 2021 г.

- ^ «Альфа Микро АМ100» . Музей устаревших компьютеров . Проверено 19 декабря 2021 г.

- ^ Управление памятью с помощью контроллера разделов памяти (PDF) (изд. A01). Альфа Микро. Октябрь 1981 г., стр. 139–155 . Проверено 14 июня 2022 г.

- ^ Справочник по процессору PDP-11/70 (PDF) . ДЕКАБРЬ. 1976. Приложение C, Сроки обучения.

- ^ Справочник по процессору DEC PDP-11, 1975, страницы 379-391, Синхронизация инструкций FP11-C

- ^ «Альфа Микро АМ-100Т» . Сравнительный отчет Ассоциации пользователей компьютеров . 3.2 (6): 9 ноября 1980 г. Проверено 3 ноября 2022 г.

- ^ «Краткое содержание 12 выпусков» . Ассоциация пользователей компьютеров: Сравнительный отчет . 3.2 (14): 4 июня 1982 г. Проверено 3 ноября 2022 г.

- ^ Ахл, Дэвид Х. (май 1984 г.). «Бенчмарк творческих вычислений» . Журнал Creative Computing . 10 (5): 6 . Проверено 2 ноября 2022 г.

- ^ Ноэль, Майк. «ВАМ Виртуальная Альфа Микро» . Проверено 13 июля 2022 г.