Делитель частоты

Эта статья в значительной степени или полностью опирается на один источник . ( декабрь 2023 г. ) |

Делитель частоты , также называемый делителем тактовой частоты , масштабатором или прескалером , представляет собой схему , которая принимает входной сигнал определенной частоты . , и генерирует выходной сигнал частоты:

где является целым числом. с фазовой автоподстройкой частоты Синтезаторы частоты используют делители частоты для генерации частоты, кратной опорной частоте. Делители частоты могут быть реализованы как для аналоговых , так и для цифровых приложений.

Аналоговый

[ редактировать ]Аналоговые делители частоты менее распространены и используются только на очень высоких частотах. Цифровые делители, реализованные в современных ИС-технологиях, могут работать на частотах до десятков ГГц. [ нужна ссылка ]

Регенеративный

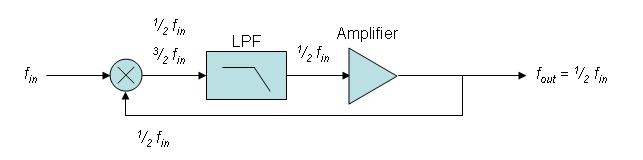

[ редактировать ]Регенеративный делитель частоты, также известный как делитель частоты Миллера , [1] смешивает входной сигнал с сигналом обратной связи от микшера.

Сигнал обратной связи . Это дает сумму и разность частот. , на выходе смесителя. Фильтр нижних частот удаляет более высокие частоты, а частота усиливается и подается обратно в смеситель.

с блокировкой впрыска

[ редактировать ]Автономный генератор , на который подается небольшой объем высокочастотного сигнала, будет стремиться колебаться синхронно с входным сигналом. Такие делители частоты сыграли важную роль в развитии телевидения .

Он работает аналогично генератору с синхронизацией по впрыску . В делителе частоты с синхронизацией по инжекции частота входного сигнала кратна (или дробной) частоте автономного генератора. Хотя эти делители частоты, как правило, имеют меньшую мощность, чем широкополосные статические (или триггерные) делители частоты, недостатком является их низкий диапазон блокировки. Диапазон блокировки ILFD обратно пропорционален добротности (Q) резервуара генератора. В интегральных схемах это делает ILFD чувствительным к изменениям процесса. Необходимо позаботиться о том, чтобы диапазон настройки схемы управления (например, генератора, управляемого напряжением) находился в пределах диапазона блокировки входа ILFD.

Цифровой

[ редактировать ]

Для целочисленного деления степени 2 можно использовать простой двоичный счетчик, синхронизируемый входным сигналом. Младший выходной бит чередуется с частотой 1/2 частоты входного тактового сигнала, следующий бит — с частотой 1/4 частоты, третий бит — с частотой 1/8 частоты и т. д. Расположение триггеров — это классический метод вычисления целых чисел. -n деление. Такое разделение является согласованным по частоте и фазе с источником в зависимости от изменений окружающей среды, включая температуру. Самая простая конфигурация — это серия, в которой каждый триггер представляет собой деление на 2. Для серии из трех таких чисел такой системой будет деление на 8. Добавив в цепочку триггеров дополнительные логические элементы, можно получить другие коэффициенты деления. Семейства логических интегральных схем могут обеспечить однокристальное решение для некоторых распространенных коэффициентов деления.

Другой популярной схемой деления цифрового сигнала на четное целое кратное является счетчик Джонсона . Это тип сети сдвиговых регистров , которая тактируется входным сигналом. Дополненный вывод последнего регистра подается обратно на вход первого регистра. Выходной сигнал получается из одного или нескольких выходов регистра. Например, делитель деления на 6 можно построить с помощью трехрегистрового счетчика Джонсона. Шесть допустимых значений счетчика: 000, 100, 110, 111, 011 и 001. Этот шаблон повторяется каждый раз, когда входной сигнал синхронизирует сеть. Выход каждого регистра представляет собой прямоугольный сигнал f/6 со сдвигом фазы между регистрами 120°. Могут быть добавлены дополнительные регистры для предоставления дополнительных целочисленных делителей.

Смешанный сигнал

[ редактировать ]( Классификация: асинхронная последовательная логика )

Расположение D-триггеров является классическим методом деления целого числа n. Такое разделение является согласованным по частоте и фазе с источником в зависимости от изменений окружающей среды, включая температуру. Самая простая конфигурация — это серия, в которой каждый D-триггер представляет собой деление на 2. Для серии из трех таких чисел такой системой будет деление на 8. Были обнаружены более сложные конфигурации, которые генерируют нечетные коэффициенты, такие как деление на 5. К стандартным классическим логическим микросхемам, реализующим эту или аналогичные функции частотного деления, относятся 7456, 7457, 74292 и 74294 (см. список логических микросхем серии 7400 и список логических микросхем серии 4000).

Синтез дробного N

[ редактировать ]Синтезатор частоты с дробным n может быть построен с использованием двух целочисленных делителей: делителя частоты на N и делителя частоты на (N + 1). При использовании контроллера модуля N переключается между двумя значениями, так что ГУН поочередно переключается между одной заблокированной частотой и другой. ГУН стабилизируется на частоте, которая является средним временем двух зафиксированных частот. Изменяя процент времени, в течение которого делитель частоты поддерживает два значения делителя, можно выбрать частоту заблокированного ГУН с очень высокой степенью детализации.

Дельта-сигма

[ редактировать ]Если последовательность деления на N и деления на (N+1) периодическая, на выходе ГУН помимо нужной частоты появляются побочные сигналы. Делители дробного n дельта-сигма решают эту проблему, рандомизируя выбор N и (N + 1), сохраняя при этом усредненные по времени отношения.

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ Р. Л. Миллер (1939). «Генератор дробной частоты, использующий регенеративную модуляцию». Труды ИРЭ . 27 (7): 446–457. дои : 10.1109/JRPROC.1939.228513 .

Внешние ссылки

[ редактировать ]- Цифровые делители частоты

- Делим на 2 и асинхронно 2 Н Делители счетчика пульсаций - Учебники по электронике

- Синхронное деление на 3, 6, 9, 12 с коэффициентом заполнения 50 % — ON Semiconductor

- Синхронное деление на 3 или 5 с выходным коэффициентом заполнения 50% и деление на 1,5 и 2,5 схемы - Xilinx

- Разделите на N-0,5, используя счетчики 74x161 – технический документ