Обнаружение последовательного присутствия

В технике вычислительной обнаружение последовательного присутствия ( SPD ) — это стандартизированный способ автоматического доступа к информации о модуле памяти . Ранее 72-контактные SIMM включали пять контактов, которые обеспечивали пять бит данных параллельного обнаружения присутствия (PPD), но стандарт 168-контактного DIMM изменился на последовательное обнаружение присутствия для кодирования большего количества информации. [1]

Когда обычный современный компьютер включается, он начинает с выполнения самотестирования при включении (POST). Примерно с середины 1990-х годов этот процесс включает автоматическую настройку имеющегося в настоящее время оборудования. SPD — это аппаратная функция памяти, которая позволяет компьютеру узнать, какая память имеется и какие тайминги памяти следует использовать для доступа к ней.

Некоторые компьютеры полностью автоматически адаптируются к изменениям в оборудовании. В большинстве случаев существует специальная дополнительная процедура доступа к параметрам BIOS , для просмотра и возможного внесения изменений в настройки. Возможно, можно будет контролировать, как компьютер использует данные SPD памяти — выбирать настройки, выборочно изменять тайминги памяти или, возможно, полностью переопределять данные SPD (см. «Разгон »).

Сохраненная информация

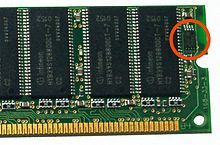

[ редактировать ]Чтобы модуль памяти поддерживал SPD, стандарты JEDEC требуют, чтобы определенные параметры находились в младших 128 байтах EEPROM, расположенного на модуле памяти. Эти байты содержат параметры синхронизации, производителя, серийный номер и другую полезную информацию о модуле. Устройства, использующие память, автоматически определяют ключевые параметры модуля, считывая эту информацию. Например, данные SPD в модуле SDRAM могут предоставить информацию о задержке CAS , чтобы система могла правильно установить ее без вмешательства пользователя.

Доступ к прошивке SPD EEPROM осуществляется через SMBus , вариант I 2 С. Протокол Это уменьшает количество коммуникационных контактов на модуле до двух: тактового сигнала и сигнала данных. EEPROM имеет общие контакты заземления с ОЗУ, имеет собственный контакт питания и три дополнительных контакта (SA0–2) для идентификации слота, которые используются для присвоения EEPROM уникального адреса в диапазоне 0x50–0x57. Мало того, что линии связи могут быть разделены между 8 модулями памяти, один и тот же SMBus обычно используется на материнских платах для задач мониторинга состояния системы, таких как считывание напряжения питания, температуры процессора и скорости вращения вентилятора.

SPD EEPROM также реагирует на I 2 Адреса C 0x30–0x37, если они не защищены от записи, а расширение (серия TSE) использует адреса 0x18–0x1F для доступа к дополнительному встроенному датчику температуры. Все эти значения семибитные. 2 Адреса C, образованные префиксом кода идентификатора типа устройства (DTIC) с SA0-2: для чтения (1100) из слота 3 используется 110 0011 = 0x33. Последний бит чтения/записи формирует 8-битный код выбора устройства. [2] Обратите внимание, что семантика slot-id для операций защиты от записи отличается: для них они вообще не могут передаваться по контактам SA. [3]

До появления SPD чипы памяти обнаруживались с помощью параллельного обнаружения присутствия (PPD). В PPD для каждого бита информации использовался отдельный вывод, а это означало, что можно было хранить только скорость и плотность модуля памяти из-за ограниченного пространства для выводов.

СДР SDRAM

[ редактировать ]

Первая спецификация SPD была выпущена JEDEC и дополнена Intel как часть спецификации памяти PC100 , представленной в 1998 году. [4] [5] [6] Большинство указанных значений представлены в двоично-десятичной форме. Самый значимый полубайт может содержать значения от 10 до 15, а в некоторых случаях простирается и выше. В таких случаях кодировки 1, 2 и 3 вместо этого используются для кодирования 16, 17 и 18. Самый старший полубайт, равный 0, зарезервирован для обозначения «неопределенного».

ПЗУ SPD определяет до трех таймингов DRAM для трех задержек CAS, заданных установленными битами в байте 18. Сначала идет самая высокая задержка CAS (самая быстрая тактовая частота), затем две меньшие задержки CAS с постепенно снижающимися тактовыми частотами.

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (декабрь) | (шестнадцатеричное) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество присутствующих байтов | Обычно 128 | |||||||

| 1 | 0x01 | журнал 2 (размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (4: SPD SDRAM) | ||||||||

| 3 | 0x03 | Биты адреса строки 2 банка (0–15) | Биты адреса строки банка 1 (1–15) | Банк 2 равен 0, если такой же, как банк 1. | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Биты адреса столбца банка 1 (1–15) | Банк 2 равен 0, если такой же, как банк 1. | ||||||

| 5 | 0x05 | Количество банков ОЗУ на модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей ECC DIMM. | |||||||

| 7 | 0x07 | Ширина данных модуля, старший байт | 0, если ширина не превышает 256 бит. | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (отличен от напряжения питания Vcc ) (0–4) | Декодируется поиском по таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при максимальной задержке CAS | ||||||

| 10 | 0x0a | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время доступа к SDRAM от часов (t AC ) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск по таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Банк 2 2× | Ширина первичной SDRAM банка 1 (1–127, обычно 8) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или двойную ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2× | Ширина ECC SDRAM банка 1 (0–127) | Ширина банка 1 устройств SDRAM ECC/четности. Банк 2 может иметь одинаковую ширину или двойную ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Задержка часов для случайного чтения столбца | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемая длина пакета (растровое изображение) |

| 17 | 0x11 | Банки на устройство SDRAM (1–255) | Обычно 2 или 4 | |||||||

| 18 | 0x12 | — | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Поддерживаемые задержки CAS (растровое изображение) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки CS (растровое изображение) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки WE (растровое изображение) |

| 21 | 0x15 | — | Избыточный | Диф. часы | Зарегистрированные данные | Буферизованные данные | Встроенная система PLL | Зарегистрированный адрес. | Буферизованный адрес. | Растровое изображение функции модуля памяти |

| 22 | 0x16 | — | — | Верхний допуск V cc (напряжения питания) | Нижний допуск V cc (напряжения питания) | Запись/1 пакетное чтение | Предварительная зарядка всех | Автоматическая предзарядка | Ранняя RAS предоплата | Растровое изображение поддержки функции чипа памяти |

| 23 | 0x17 | Наносекунды (4–18) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время тактового цикла при средней задержке CAS | ||||||

| 24 | 0x18 | Наносекунды (4–18) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время доступа к данным от часов (t AC ) | ||||||

| 25 | 0x19 | Наносекунды (1–63) | 0,25 нс (0–3: 0,00–0,75) | Время тактового цикла при короткой задержке CAS. | ||||||

| 26 | 0x1a | Наносекунды (1–63) | 0,25 нс (0–3: 0,00–0,75) | Время доступа к данным от часов (t AC ) | ||||||

| 27 | 0x1b | Наносекунды (1–255) | Минимальное время предварительной зарядки ряда (t RP ) | |||||||

| 28 | 0x1c | Наносекунды (1–255) | Минимальная задержка активности строки – активная задержка строки (t RRD ) | |||||||

| 29 | 0x1d | Наносекунды (1–255) | Минимальная задержка между RAS и CAS (t RCD ) | |||||||

| 30 | 0x1е | Наносекунды (1–255) | Минимальное время активности для предварительной зарядки (t RAS ) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МБ | 8 МБ | 4 МБ | Плотность банка модулей (растровое изображение). Два бита устанавливаются, если банки разного размера. |

| 32 | 0x20 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время установки адреса/команды по часам | |||||

| 33 | 0x21 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время удержания адреса/команды после часов | |||||

| 34 | 0x22 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время установки ввода данных от часов | |||||

| 35 | 0x23 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время удержания ввода данных после часов | |||||

| 36–61 | 0x24–0x3d | Сдержанный | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная редакция (0–9) | Незначительная доработка (0–9) | уровень ревизии СПД; например, 1,2 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, затем не инвертируется. | |||||||

| 64–71 | 0x40–47 | Идентификатор производителя JEDEC. | Сохраняется с прямым порядком байтов, завершающийся нулем. | |||||||

| 72 | 0x48 | Место производства модуля | Код конкретного поставщика | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами | |||||||

| 91–92 | 0x5b–0x5c | Код версии модуля | Код конкретного поставщика | |||||||

| 93 | 0x5d | Десятки лет (0–9: 0–90) | Годы (0–9) | Дата изготовления (ГГWW) | ||||||

| 94 | 0x5e | Десятки недель (0–5: 0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f–0x62 | Серийный номер модуля | Код конкретного поставщика | |||||||

| 99–125 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

| 126 | 0x7e | 0x66 [ так в оригинале ] для 66 МГц, 0x64 для 100 МГц | Поддержка частоты Intel | |||||||

| 127 | 0x7f | CLK0 | CLK1 | CLK3 | CLK3 | 90/100 °С | CL3 | CL2 | Параллельная точка доступа | Растровое изображение функции Intel |

ГДР SDRAM

[ редактировать ]Формат DDR DIMM SPD является расширением формата SDR SDRAM. Чаще всего диапазоны параметров масштабируются для обеспечения более высоких скоростей.

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (декабрь) | (шестнадцатеричное) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество записанных байт | Обычно 128 | |||||||

| 1 | 0x01 | журнал 2 (размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (7 = DDR SDRAM) | ||||||||

| 3 | 0x03 | Биты адреса строки 2 банка (0–15) | Биты адреса строки банка 1 (1–15) | Банк 2 равен 0, если такой же, как банк 1. | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Биты адреса столбца банка 1 (1–15) | Банк 2 равен 0, если такой же, как банк 1. | ||||||

| 5 | 0x05 | Количество банков ОЗУ на модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей ECC DIMM. | |||||||

| 7 | 0x07 | Ширина данных модуля, старший байт | 0, если ширина не превышает 256 бит. | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (отличен от напряжения питания Vcc ) (0–5) | Декодируется поиском по таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к SDRAM от часов (t AC ) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск по таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Банк 2 2× | Ширина первичной SDRAM банка 1 (1–127) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или двойную ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2× | Ширина ECC SDRAM банка 1 (0–127) | Ширина банка 1 устройств SDRAM ECC/четности. Банк 2 может иметь одинаковую ширину или двойную ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Задержка часов для случайного чтения столбца | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемая длина пакета (растровое изображение) |

| 17 | 0x11 | Банки на устройство SDRAM (1–255) | Обычно 4 | |||||||

| 18 | 0x12 | — | 4 | 3.5 | 3 | 2.5 | 2 | 1.5 | 1 | Поддерживаемые задержки CAS (растровое изображение) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки CS (растровое изображение) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки WE (растровое изображение) |

| 21 | 0x15 | — | х | Разница часов | Внешнее включение FET-переключателя | Встроенный переключатель FET | Встроенная система PLL | Зарегистрирован | Буферизованный | Растровое изображение функции модуля памяти |

| 22 | 0x16 | Быстрая точка доступа | Одновременная автоматическая предоплата | Верхний допуск V cc (напряжения питания) | Нижний допуск V cc (напряжения питания) | — | — | — | Включает слабый драйвер | Растровое изображение функции чипа памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при средней задержке CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к данным от часов (t AC ) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при короткой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к данным от часов (t AC ) | ||||||

| 27 | 0x1b | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время предварительной зарядки ряда (t RP ) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальная задержка активности строки – активная задержка строки (t RRD ) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальная задержка между RAS и CAS (t RCD ) | ||||||

| 30 | 0x1е | Наносекунды (1–255) | Минимальное время активности для предварительной зарядки (t RAS ) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МБ/ 4 ГиБ |

8 МБ/ 2 ГиБ |

4 МБ/ 1 ГиБ |

Плотность банка модулей (растровое изображение). Два бита устанавливаются, если банки разного размера. |

| 32 | 0x20 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время установки адреса/команды по часам | ||||||

| 33 | 0x21 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время удержания адреса/команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время установки ввода данных от часов | ||||||

| 35 | 0x23 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время удержания ввода данных после часов | ||||||

| 36–40 | 0x24–0x28 | Сдержанный | Информация о суперсете | |||||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности/обновления (t RC ) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до активного/обновления (t RFC ) | |||||||

| 43 | 0x2b | Наносекунды (1–63 или 255: без максимума) | 0,25 нс (0–0,75) | Максимальное время тактового цикла (t CK макс.) | ||||||

| 44 | 0x2c | Сотые доли наносекунды (0,01–2,55) | Максимальный перекос, DQS к любому DQ. (t DQSQ макс.) | |||||||

| 45 | 0x2d | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунды (0,00–0,09) | Коэффициент асимметрии удержания считываемых данных (t QHS ) | ||||||

| 46 | 0x2e | Сдержанный | Для будущей стандартизации | |||||||

| 47 | 0x2f | — | Высота | Высота модуля DIMM, поиск по таблице | ||||||

| 48–61 | 0x30–0x3d | Сдержанный | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная редакция (0–9) | Незначительная доработка (0–9) | Уровень версии SPD, 0,0 или 1,0. | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, затем не инвертируется. | |||||||

| 64–71 | 0x40–47 | Идентификатор производителя JEDEC. | Сохраняется с прямым порядком байтов, завершающийся нулем. | |||||||

| 72 | 0x48 | Место производства модуля | Код конкретного поставщика | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами | |||||||

| 91–92 | 0x5b–0x5c | Код версии модуля | Код конкретного поставщика | |||||||

| 93 | 0x5d | Десятки лет (0–90) | Годы (0–9) | Дата изготовления (ГГWW) | ||||||

| 94 | 0x5e | Десятки недель (0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f–0x62 | Серийный номер модуля | Код конкретного поставщика | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

DDR2 SDRAM

[ редактировать ]Стандарт DDR2 SPD вносит ряд изменений, но примерно аналогичен приведенному выше. Одним из заметных исключений является запутанная и малоиспользуемая поддержка модулей DIMM двух рангов разных размеров.

Для полей времени цикла (байты 9, 23, 25 и 49), которые закодированы в BCD , для десятых разрядов определены некоторые дополнительные кодировки, чтобы точно представлять некоторые общие моменты времени:

| Шестигранник | Двоичный | Значение |

|---|---|---|

| А | 1010 | 0.25 ( 1 ⁄ 4 ) |

| Б | 1011 | 0.33 ( 1 ⁄ 3 ) |

| С | 1100 | 0.66 ( 2 ⁄ 3 ) |

| Д | 1101 | 0.75 ( 3 ⁄ 4 ) |

| И | 1110 | 0.875 ( 7 ⁄ 8 , расширение Nvidia XMP) |

| Ф | 1111 | Сдержанный |

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество записанных байт | Обычно 128 | |||||||

| 1 | 0x01 | журнал 2 (размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (8 = DDR2 SDRAM) | ||||||||

| 3 | 0x03 | Сдержанный | Биты адреса строки (1–15) | |||||||

| 4 | 0x04 | Сдержанный | Биты адреса столбца (1–15) | |||||||

| 5 | 0x05 | Вертикальная высота | Куча? | КонС? | Ранги −1 (1–8) | Обычно 0 или 1, что означает 1 или 2. | ||||

| 6 | 0x06 | Ширина данных модуля | Обычно 64 или 72 для модулей ECC DIMM. | |||||||

| 7 | 0x07 | Сдержанный | ||||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (отличен от напряжения питания Vcc ) (0–5) | Декодируется поиском по таблице. Обычно 5 = SSTL 1,8 В | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к SDRAM от часов (t AC ) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск по таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Ширина первичной SDRAM (1–255) | Обычно 8 (модуль состоит из 8 частей) или 16. | |||||||

| 14 | 0x0e | Ширина ECC SDRAM (0–255) | Ширина банка устройств SDRAM с ECC/четностью. Обычно 0 или 8. | |||||||

| 15 | 0x0f | Сдержанный | ||||||||

| 16 | 0x10 | — | — | — | — | 8 | 4 | — | — | Поддерживаемая длина пакета (растровое изображение) |

| 17 | 0x11 | Банки на устройство SDRAM (1–255) | Обычно 4 или 8 | |||||||

| 18 | 0x12 | 7 | 6 | 5 | 4 | 3 | 2 | — | — | Поддерживаемые задержки CAS (растровое изображение) |

| 19 | 0x13 | Сдержанный | ||||||||

| 20 | 0x14 | — | — | Мини-UDIMM | Мини-RDIMM | Микро-DIMM | SO-DIMM | UDIMM | RDIMM | Тип DIMM данной сборки (растровый) |

| 21 | 0x15 | — | Модуль - зонд для анализа | — | Внешнее включение FET-переключателя | — | — | — | — | Растровое изображение функции модуля памяти |

| 22 | 0x16 | — | — | — | — | — | — | — | Включает слабый драйвер | Растровое изображение функции чипа памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при средней задержке CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к данным от часов (t AC ) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при короткой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время доступа к данным от часов (t AC ) | ||||||

| 27 | 0x1b | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальное время предварительной зарядки ряда (t RP ) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальная задержка активности строки – активная задержка строки (t RRD ) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальная задержка между RAS и CAS (t RCD ) | ||||||

| 30 | 0x1е | Наносекунды (1–255) | Минимальное время активности для предварительной зарядки (t RAS ) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 16 ГиБ | 8 ГиБ | 4 ГиБ | 2 ГиБ | 1 ГиБ | Размер каждого ранга (растровое изображение). |

| 32 | 0x20 | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунды (0,00–0,09) | Время установки адреса/команды по часам | ||||||

| 33 | 0x21 | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунды (0,00–0,09) | Время удержания адреса/команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время настройки ввода данных со стробоскопа | ||||||

| 35 | 0x23 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время удержания ввода данных после стробоскопа | ||||||

| 36 | 0x24 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время восстановления записи (t WR ) | ||||||

| 37 | 0x25 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутренняя задержка команды записи для чтения (t WTR ) | ||||||

| 38 | 0x26 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутреннее чтение для задержки команды предварительной зарядки (t RTP ) | ||||||

| 39 | 0x27 | Сдержанный | Зарезервировано для «характеристик датчика анализа памяти». | |||||||

| 40 | 0x28 | — | t RC дробный нс (0–5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 |

t RFC дробные нс (0–5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 |

t RFC + 256 нс | Расширение байтов 41 и 42. | ||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности/обновления (t RC ) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до активного/обновления (t RFC ) | |||||||

| 43 | 0x2b | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Максимальное время тактового цикла (t CK max) | ||||||

| 44 | 0x2c | Сотые доли наносекунды (0,01–2,55) | Максимальный перекос, DQS к любому DQ. (t DQSQ макс) | |||||||

| 45 | 0x2d | Сотые доли наносекунды (0,01–2,55) | Коэффициент асимметрии удержания считываемых данных (t QHS ) | |||||||

| 46 | 0x2e | Микросекунды (1–255) | Время повторной блокировки ФАПЧ | |||||||

| 47–61 | 0x2f–0x3d | Сдержанный | Для будущей стандартизации. | |||||||

| 62 | 0x3e | Основная редакция (0–9) | Незначительная доработка (0,0–0,9) | Уровень версии SPD, обычно 1.0. | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не инвертируется. | |||||||

| 64–71 | 0x40–47 | Идентификатор JEDEC производителя | Сохраненный прямой порядок байтов, завершающий нулевой блок. | |||||||

| 72 | 0x48 | Место производства модуля | Код конкретного поставщика | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами (ограничено (,-,), A–Z, a–z, 0–9, пробелом) | |||||||

| 91–92 | 0x5b–0x5c | Код версии модуля | Код конкретного поставщика | |||||||

| 93 | 0x5d | Годы с 2000 г. (0–255) | Дата изготовления (ГГWW) | |||||||

| 94 | 0x5e | Недели (1–52) | ||||||||

| 95–98 | 0x5f–0x62 | Серийный номер модуля | Код конкретного поставщика | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

DDR3 SDRAM

[ редактировать ]Стандарт DDR3 SDRAM значительно пересматривает и упрощает структуру содержимого SPD. Вместо ряда наносекундных полей в двоично-десятичном кодировании некоторые единицы «временной развертки» указываются с высокой точностью, а различные параметры синхронизации кодируются как кратные этой базовой единице. [10] Кроме того, была отменена практика указания разных значений времени в зависимости от задержки CAS; теперь существует только один набор параметров синхронизации.

Версия 1.1 позволяет выражать некоторые параметры как значение «средней временной развертки» плюс поправку (со знаком, -128 +127) «тонкой временной развертки». Обычно средняя развертка составляет 1/8 нс (125 пс), а точная развертка — 1, 2,5 или 5 пс. Для совместимости с более ранними версиями, в которых отсутствует коррекция, средневременное базовое число обычно округляется в большую сторону, а поправка отрицательна. Значения, которые работают таким образом:

| МТБ байт | ФТБ байт | Ценить |

|---|---|---|

| 12 | 34 | t CK min, минимальный период тактирования |

| 16 | 35 | t AA min, минимальное время задержки CAS |

| 18 | 36 | t RCD min, минимальная задержка между RAS# и CAS# |

| 20 | 37 | t RP min, минимальная задержка предварительной зарядки ряда |

| 21, 23 | 38 | t RC min, минимальная задержка между активным и предварительным зарядом |

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Исключить серийный номер из CRC | Всего SPD в байтах (undef/256) | Используемые байты SPD (undef/128/176/256) | ||||||

| 1 | 0x01 | Основная редакция СПД | Небольшая доработка СПД | 1,0, 1,1, 1,2 или 1,3 | ||||||

| 2 | 0x02 | Базовый тип памяти (11 = DDR3 SDRAM) | Тип чипов оперативной памяти | |||||||

| 3 | 0x03 | Сдержанный | Тип модуля | Тип модуля; например, 2 = DIMM без буферизации, 3 = SO-DIMM, 11 = LRDIMM | ||||||

| 4 | 0x04 | — | Биты адреса банка-3 | log 2 (бит на чип)-28 | Ноль означает 8 банков, 256 Мибит. | |||||

| 5 | 0x05 | — | Биты адреса строки-12 | Биты адреса столбца −9 | ||||||

| 6 | 0x06 | Сдержанный | 1.25 V | 1.35 V | Не 1,5 В | Поддерживаемые напряжения модулей. 1,5 В — значение по умолчанию. | ||||

| 7 | 0x07 | — | ранги-1 | log 2 (биты ввода-вывода/чип)-2 | Организация модулей | |||||

| 8 | 0x08 | — | Биты ECC (001=8) | журнал 2 (биты данных)-3 | 0x03 для 64-разрядного модуля DIMM без ECC. | |||||

| 9 | 0x09 | Дивиденд, пикосекунды (1–15) | Делитель, пикосекунды (1–15) | Точная временная база, делимое/делитель | ||||||

| 10 | 0x0a | Дивиденд, наносекунды (1–255) | Средняя временная база, дивиденд/делитель; обычно 1/8 | |||||||

| 11 | 0x0b | Делитель, наносекунды (1–255) | ||||||||

| 12 | 0x0c | Минимальное время цикла t CK мин | В кратности МТБ | |||||||

| 13 | 0x0d | Сдержанный | ||||||||

| 14 | 0x0e | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | Поддерживаемые задержки CAS (растровое изображение) |

| 15 | 0x0f | — | 18 | 17 | 16 | 15 | 14 | 13 | 12 | |

| 16 | 0x10 | Минимальное время задержки CAS, t AA min | В кратности МТБ; например, 80/8 нс. | |||||||

| 17 | 0x11 | Минимальное время восстановления записи, t WR min | В кратности МТБ; например, 120/8 нс. | |||||||

| 18 | 0x12 | Минимальное время задержки между RAS и CAS, t RCD min | В кратности МТБ; например, 100/8 нс. | |||||||

| 19 | 0x13 | Минимальное время активной задержки между строками, t RRD min | В кратности МТБ; например, 60/8 нс. | |||||||

| 20 | 0x14 | Минимальное время подзарядки ряда, т об/ мин мин | В кратности МТБ; например, 100/8 нс. | |||||||

| 21 | 0x15 | t RC мин, биты 11:8 | т РАН кто, биты 11:8 | Старшие 4 бита байтов 23 и 22 | ||||||

| 22 | 0x16 | Минимальное активное время, t RAS min, биты 7:0 | В кратности МТБ; например, 280/8 нс. | |||||||

| 23 | 0x17 | Минимум от активного до активного/обновления, t RC min, биты 7:0 | В кратности МТБ; например, 396/8 нс. | |||||||

| 24 | 0x18 | Минимальная задержка восстановления при обновлении, t RFC min, биты 7:0 | В кратности МТБ; например, 1280/8 нс. | |||||||

| 25 | 0x19 | Минимальная задержка восстановления при обновлении, t RFC min, биты 15:8 | ||||||||

| 26 | 0x1a | Минимальная внутренняя задержка записи для чтения, t WTR min | В кратности МТБ; например, 60/8 нс. | |||||||

| 27 | 0x1b | Минимальное внутреннее чтение для задержки предварительной зарядки, t RTP min | В кратности МТБ; например, 60/8 нс. | |||||||

| 28 | 0x1c | Сдержанный | t FAW мин, биты 11:8 | В кратности МТБ; например, 240/8 нс. | ||||||

| 29 | 0x1d | Минимум четыре задержки активации окна t FAW min, биты 7:0 | ||||||||

| 30 | 0x1е | DLL отключена | — | РЗК/7 | РЗК/6 | Дополнительные функции SDRAM поддерживают растровое изображение | ||||

| 31 | 0x1f | ПАСР | — | ОДТС | АСР | ЭТР 1× | ЭТР (95 °С) | Параметры нагрева и обновления SDRAM | ||

| 32 | 0x20 | Подарок | Точность (подлежит уточнению; в настоящее время 0 = не определено) | Присутствует термодатчик DIMM? | ||||||

| 33 | 0x21 | Нестандартный. | Количество кубиков | — | Сигнальная нагрузка | Нестандартный тип устройства SDRAM (например, многослойный кристалл) | ||||

| 34 | 0x22 | t CK минимальная коррекция (новое в версии 1.1) | Знаковое кратное FTB, добавленное к байту 12. | |||||||

| 35 | 0x23 | t AA Минимальная коррекция (новое в версии 1.1) | Знаковое кратное FTB, добавленное к байту 16. | |||||||

| 36 | 0x24 | t УЗО Минимальная коррекция (новая версия 1.1) | Знаковое кратное FTB, добавленное к байту 18. | |||||||

| 37 | 0x25 | t RP Коррекция мин. (новое в версии 1.1) | Знаковое кратное FTB, добавленное к байту 20. | |||||||

| 38 | 0x26 | t RC Коррекция мин. (новое в версии 1.1) | Знаковое кратное FTB, добавленное к байту 23. | |||||||

| 39–40 | 0x27–0x28 | Сдержанный | Для будущей стандартизации. | |||||||

| 41 | 0x29 | Зависит от поставщика | т МАВ | Максимальное количество активаций (MAC) (непроверено/700 тыс./600 тыс./.../200 тыс./зарезервировано/∞) | Для последствий молотков смягчения | |||||

| 42–59 | 0x2a–0x3b | Сдержанный | Для будущей стандартизации. | |||||||

| 60 | 0x3c | — | Высота модуля, мм (1–31, >45) | Номинальная высота модуля | ||||||

| 61 | 0x3d | Толщина спинки, мм (1–16) | Толщина фасада, мм (1–16) | Толщина модуля, значение = ячейка (мм) − 1 | ||||||

| 62 | 0x3e | Дизайн | Редакция | Номер конструкции JEDEC | Используемый эталонный проект JEDEC (11111 = нет) | |||||

| 63–116 | 0x3f–0x74 | Раздел, посвященный конкретному модулю | Различия между зарегистрированными/небуферизованными | |||||||

| 117 | 0x75 | Идентификатор производителя модуля, lsbyte | Назначено JEP-106 | |||||||

| 118 | 0x76 | Идентификатор производителя модуля, мсбайт | ||||||||

| 119 | 0x77 | Место производства модуля | Код конкретного поставщика | |||||||

| 120 | 0x78 | Десятки лет | Годы | Год выпуска (BCD) | ||||||

| 121 | 0x79 | Десятки недель | Недели | Производственная неделя (BCD) | ||||||

| 122–125 | 0x7a–0x7d | Серийный номер модуля | Код конкретного поставщика | |||||||

| 126–127 | 0x7e–0x7f | СПД ЦРК-16 | Включает байты 0–116 или 0–125; см. байт 0, бит 7 | |||||||

| 128–145 | 0x80–0x91 | Номер детали модуля | Подмножество ASCII, дополненное пробелами | |||||||

| 146–147 | 0x92–0x93 | Код версии модуля | Определяется поставщиком | |||||||

| 148–149 | 0x94–0x95 | Идентификатор производителя DRAM | В отличие от производителя модуля | |||||||

| 150–175 | 0x96–0xAF | Данные производителя | ||||||||

| 176–255 | 0xB0–0xFF | Доступно для использования клиентом | ||||||||

Объем памяти модуля можно вычислить по байтам 4, 7 и 8. Ширина модуля (байт 8), разделенная на количество битов на чип (байт 7), дает количество чипов на ранг. Затем это значение можно умножить на емкость каждого чипа (байт 4) и количество рангов чипов в модуле (обычно 1 или 2, начиная с байта 7).

DDR4 SDRAM

[ редактировать ]Стандарт DDR4 SDRAM «Приложение L» для SPD изменяет используемый модуль EEPROM. Вместо старых 256-байтовых EEPROM, совместимых с AT24C02, JEDEC теперь определяет новый нестандартный тип EE1004 с двумя страницами на уровне SMBus, каждая по 256 байт. Новая память по-прежнему использует старые адреса 0x50–0x57, но два дополнительных адреса 0x36 (SPA0) и 0x37 (SPA1) теперь используются для приема команд выбора текущей активной страницы для шины, что является формой переключения банков . [13] Внутри каждая логическая страница делится на два физических блока по 128 байт каждый, всего четыре блока по 512 байт. [14] Другая семантика для «специальных» диапазонов адресов осталась прежней, хотя защита от записи теперь реализуется блоками, и для изменения ее состояния теперь требуется высокое напряжение на SA0. [15]

Приложение L определяет несколько различных макетов, которые можно подключить к шаблону размером 512 байт (из которых определено максимум 320 байт), в зависимости от типа модуля памяти. Определения битов аналогичны DDR3. [14]

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Используемые байты SPD | ||||||||

| 1 | 0x01 | СПД ревизия n | Обычно 0x10, 0x11, 0x12. | |||||||

| 2 | 0x02 | Базовый тип памяти (12 = DDR4 SDRAM) | Тип чипов оперативной памяти | |||||||

| 3 | 0x03 | Сдержанный | Тип модуля | Тип модуля; например, 2 = DIMM без буферизации, 3 = SO-DIMM, 11 = LRDIMM | ||||||

| 4 | 0x04 | Биты банковской группы | Биты адреса банка-2 | Общая емкость SDRAM на кристалл в мегабитах | Ноль означает отсутствие банковских групп, 4 банка, 256 Mibit. | |||||

| 5 | 0x05 | Сдержанный | Биты адреса строки-12 | Биты адреса столбца −9 | ||||||

| 6 | 0x06 | Тип первичного пакета SDRAM | Количество кубиков | Сдержанный | Загрузка сигнала | |||||

| 7 | 0x07 | Сдержанный | Максимальное окно активации (tMAW) | Максимальное количество активаций (MAC) | Дополнительные функции SDRAM | |||||

| 8 | 0x08 | Сдержанный | Параметры нагрева и обновления SDRAM | |||||||

| 9 | 0x09 | Почтовый ремонт упаковки (PPR) | Мягкий ППР | Сдержанный | Другие дополнительные функции SDRAM | |||||

| 10 | 0x0a | Тип пакета SDRAM | Количество кубиков − 1 | Коэффициент плотности DRAM | Загрузка сигнала | Тип вторичного пакета SDRAM | ||||

| 11 | 0x0b | Сдержанный | Непреходящий флаг | Действующий флаг | Номинальное напряжение модуля, ВДД | |||||

| 12 | 0x0c | Сдержанный | Ранговый микс | Ранги пакетов на DIMM-1 | Ширина устройства SDRAM | Организация модулей | ||||

| 13 | 0x0d | Сдержанный | Увеличение ширины автобуса | Основная ширина шины | Ширина шины памяти модуля в битах | |||||

| 14 | 0x0e | Термальный датчик | Сдержанный | Модуль термодатчика | ||||||

| 15 | 0x0f | Сдержанный | Тип расширенного базового модуля | |||||||

| 16 | 0x10 | Сдержанный | ||||||||

| 17 | 0x11 | Сдержанный | Средняя временная развертка (MTB) | Точная временная развертка (FTB) | Измеряется в пс. | |||||

| 18 | 0x12 | Минимальное время цикла SDRAM, t CKAVG min | В кратности МТБ; например, 100/8 нс. | |||||||

| 19 | 0x13 | Максимальное время цикла SDRAM, t CKAVG max | В кратности МТБ; например, 60/8 нс. | |||||||

| 20 | 0x14 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | Битовая маска поддерживаемых задержек CAS |

| 21 | 0x15 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | Битовая маска поддерживаемых задержек CAS |

| 22 | 0x16 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | Битовая маска поддерживаемых задержек CAS |

| 23 | 0x17 | Низкий диапазон CL | Сдержанный | 36 | 35 | 34 | 33 | 32 | 31 | Битовая маска поддерживаемых задержек CAS |

| 24 | 0x18 | Минимальное время задержки CAS, t AA min | В кратности МТБ; например, 1280/8 нс. | |||||||

| 25 | 0x19 | Минимальное время задержки между RAS и CAS, t RCD min | В кратности МТБ; например, 60/8 нс. | |||||||

| 26 | 0x1a | Минимальное время задержки предзаряда ряда, т об/ мин мин | В кратности МТБ; например, 60/8 нс. | |||||||

| 27 | 0x1b | Верхние полубайты для t RAS min и t RC min | ||||||||

| 28 | 0x1c | Минимальное активное время задержки предварительной зарядки, t RAS мин. младший значащий байт | В кратности МТБ | |||||||

| 29 | 0x1d | Минимальное время задержки перехода от активного к активному/обновлению, t RC min младший значащий байт | В кратности МТБ | |||||||

| 30 | 0x1е | Минимальное время задержки восстановления обновления, t RFC1 мин. младший байт | В кратности МТБ | |||||||

| 31 | 0x1f | Минимальное время задержки восстановления после обновления, t RFC1 мин. старший байт | В кратности МТБ | |||||||

| 32 | 0x20 | Минимальное время задержки восстановления после обновления, t RFC2 мин. младший байт | В кратности МТБ | |||||||

| 33 | 0x21 | Минимальное время задержки восстановления после обновления, t RFC2 мин. старший байт | В кратности МТБ | |||||||

| 34 | 0x22 | Минимальное время задержки восстановления после обновления, t RFC4 мин. младший байт | В кратности МТБ | |||||||

| 35 | 0x23 | Минимальное время задержки восстановления после обновления, t RFC4 мин. старший байт | В кратности МТБ | |||||||

| 36 | 0x24 | Сдержанный | t FAW мин. наиболее значимый полубайт | |||||||

| 37 | 0x25 | Минимум четыре времени задержки активации окна, t FAW мин. младший байт | В кратности МТБ | |||||||

| 38 | 0x26 | Минимальное время активации для активации времени задержки, t RRD_S min, другая группа банков | В кратности МТБ | |||||||

| 39 | 0x27 | Минимальное время активации для активации времени задержки, t RRD_L min, та же группа банков | В кратности МТБ | |||||||

| 40 | 0x28 | Минимальное время задержки между CAS и CAS, t CCD_L min, та же группа банков | В кратности МТБ | |||||||

| 41 | 0x29 | Верхний полубайт для t WR мин. | ||||||||

| 42 | 0x2a | Минимальное время восстановления записи, t WR min | В кратности МТБ | |||||||

| 43 | 0x2b | Верхние полубайты для t WTR min | ||||||||

| 44 | 0x2c | Минимальное время записи для чтения, t WTR_S мин, другая группа банков | В кратности МТБ | |||||||

| 45 | 0x2d | Минимальное время записи для чтения, t WTR_L мин, та же группа банков | В кратности МТБ | |||||||

| 49–59 | 0x2e–0x3b | Сдержанный | Раздел базовой конфигурации | |||||||

| 60–77 | 0x3c–0x4d | Разъем для битового сопоставления SDRAM | ||||||||

| 78–116 | 0x4e–0x74 | Сдержанный | Раздел базовой конфигурации | |||||||

| 117 | 0x75 | Точное смещение минимального времени задержки между CAS и CAS, t CCD_L min, тот же банк | Дополнительный множитель до двух для единиц FTB | |||||||

| 118 | 0x76 | Точное смещение минимального времени активации для активации, t RRD_L min, та же группа банков | Дополнительный множитель до двух для единиц FTB | |||||||

| 119 | 0x77 | Точное смещение минимального времени активации для активации, t RRD_S min, другая группа банков | Дополнительный множитель до двух для единиц FTB | |||||||

| 120 | 0x78 | Точное смещение минимального времени задержки между активным и активным/обновлением, t RC min | Дополнительный множитель до двух для единиц FTB | |||||||

| 121 | 0x79 | Точное смещение минимального времени задержки предварительной зарядки ряда, t RP min | Дополнительный множитель до двух для единиц FTB | |||||||

| 122 | 0x7a | Точное смещение минимального времени задержки между RAS и CAS, t RCD min | Дополнительный множитель до двух для единиц FTB | |||||||

| 123 | 0x7b | Точное смещение минимального времени задержки CAS, t AA min | Дополнительный множитель до двух для единиц FTB | |||||||

| 124 | 0x7c | Точное смещение максимального времени цикла SDRAM, t CKAVG max | Дополнительный множитель до двух для единиц FTB | |||||||

| 125 | 0x7d | Точное смещение минимального времени цикла SDRAM, t CKAVG min | Дополнительный множитель до двух для единиц FTB | |||||||

| 126 | 0x7e | Циклический избыточный код (CRC) для раздела базовой конфигурации, младший байт | Алгоритм CRC16 | |||||||

| 127 | 0x7f | Циклический избыточный код (CRC) для раздела базовой конфигурации, старший байт | Алгоритм CRC16 | |||||||

| 128–191 | 0x80–0xbf | Раздел, посвященный конкретному модулю | В зависимости от семейства модулей памяти (UDIMM, RDIMM, LRDIMM) | |||||||

| 192–255 | 0xc0–0xff | Особые параметры архитектуры гибридной памяти | ||||||||

| 256–319 | 0x100–0x13f | Расширенный блок функциональных параметров | ||||||||

| 320–321 | 0x140–0x141 | Производитель модуля | См. JEP-106. | |||||||

| 322 | 0x142 | Место производства модуля | Код места производства, определенный производителем | |||||||

| 323 | 0x143 | Год выпуска модуля | Представлено в двоично-десятичном формате (BCD). | |||||||

| 324 | 0x144 | Неделя изготовления модулей | Представлено в двоично-десятичном формате (BCD). | |||||||

| 325–328 | 0x145–0x148 | Серийный номер модуля | Определенный производителем формат уникального серийного номера для номеров деталей. | |||||||

| 329–348 | 0x149–0x15c | Номер детали модуля | Номер детали в формате ASCII, неиспользуемые цифры должны быть установлены на 0x20. | |||||||

| 349 | 0x15d | Код версии модуля | Код версии, определенный производителем | |||||||

| 350–351 | 0x15e–0x15f | Идентификационный код производителя DRAM | См. JEP-106. | |||||||

| 352 | 0x160 | Степпинг DRAM | Степпинг, определяемый производителем, или 0xFF, если не используется. | |||||||

| 353–381 | 0x161–0x17d | Особые данные производителя | ||||||||

| 382–383 | 0x17e–0x17f | Сдержанный | ||||||||

DDR5 SDRAM

[ редактировать ]Предварительная таблица для DDR5 на основе спецификации JESD400-5. [17]

DDR5 расширяет таблицу SPD до 1024 байт. SPD DDR5 использует шину I3C .

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество байтов в устройстве SPD | ||||||||

| 1 | 0x01 | Версия SPD для параметров базовой конфигурации | ||||||||

| 2 | 0x02 | Ключевой байт/тип протокола командной шины | ||||||||

| 3 | 0x03 | Ключевой байт/тип модуля | ||||||||

| 4 | 0x04 | Первая плотность и корпус SDRAM | ||||||||

| 5 | 0x05 | Первая адресация SDRAM | ||||||||

| 6 | 0x06 | Первая ширина ввода-вывода SDRAM | ||||||||

| 7 | 0x07 | Первые группы банков SDRAM и банки на группу банков | ||||||||

| 8 | 0x08 | Вторая плотность и корпус SDRAM | ||||||||

| 9 | 0x09 | Вторая адресация SDRAM | ||||||||

| 10 | 0x0a | Ширина ввода-вывода второй SDRAM | ||||||||

| 11 | 0x0b | Вторые группы банков SDRAM и банки на группу банков | ||||||||

| 12 | 0x0c | Дополнительные функции SDRAM | ||||||||

| 13 | 0x0d | Опции термообработки и обновления | ||||||||

| 14 | 0x0e | Сдержанный | ||||||||

| 15 | 0x0f | Сдержанный | ||||||||

| 16 | 0x10 | Номинальное напряжение SDRAM, ВДД | ||||||||

Расширения

[ редактировать ]Стандарт JEDEC определяет только некоторые байты SPD. По-настоящему важные данные умещаются в первые 64 байта. [8] [9] [18] [19] [20] а часть оставшейся суммы предназначена для идентификации производителя. Однако обычно предоставляется 256-байтовая EEPROM. Оставшееся пространство было использовано по-разному.

Расширенные профили производительности (EPP)

[ редактировать ]Память обычно поставляется с консервативными рекомендациями по синхронизации в ПЗУ SPD, чтобы обеспечить базовую функциональность во всех системах. Энтузиасты часто тратят значительное время на ручную настройку таймингов памяти для более высокой скорости.

Расширенные профили производительности — это расширение SPD, разработанное Nvidia и Corsair , которое включает дополнительную информацию для более высокопроизводительной работы DDR2 SDRAM , включая информацию о напряжениях питания и синхронизации команд, не включенную в спецификацию JEDEC SPD. Информация EPP хранится в той же EEPROM, но в байтах 99–127, которые не используются стандартным DDR2 SPD. [21]

| Байты | Размер | Полные профили | Сокращенные профили |

|---|---|---|---|

| 99–103 | 5 | заголовок EPP | |

| 104–109 | 6 | Профиль ФП1 | Профиль AP1 |

| 110–115 | 6 | Профиль AP2 | |

| 116–121 | 6 | Профиль ФП2 | Профиль AP3 |

| 122–127 | 6 | Профиль AP4 | |

Параметры специально разработаны для контроллера памяти на чипсетах nForce 5 , nForce 6 и nForce 7 . Nvidia поощряет поддержку EPP в BIOS своих высокопроизводительных чипсетов материнских плат. Это предназначено для обеспечения « разгона в один клик » для повышения производительности с минимальными усилиями.

Память EPP, сертифицированная по производительности и стабильности, Nvidia называет «память с поддержкой SLI». [22] Термин «SLI-ready-memory» вызвал некоторую путаницу, поскольку не имеет ничего общего с SLI-видео . Можно использовать память EPP/SLI с одной видеокартой (даже с картой стороннего производителя), а можно запустить настройку видео SLI с несколькими картами без памяти EPP/SLI.

Расширенная версия EPP 2.0 также поддерживает память DDR3. [23]

Профиль Intel Extreme Memory (XMP)

[ редактировать ]Аналогичное расширение JEDEC SPD, разработанное Intel, было разработано для модулей DIMM DDR3 SDRAM , которые позже использовались в DDR4 SDRAM также . XMP использует байты 176–255, которые не выделяются JEDEC, для кодирования таймингов памяти с более высокой производительностью. [24]

Позже AMD разработала AMP, технологию, эквивалентную XMP, для использования в линейке модулей памяти Radeon Memory, оптимизированных для использования на платформах AMD. [25] [26] Кроме того, разработчики материнских плат внедрили свои собственные технологии, позволяющие материнским платам на базе AMD читать профили XMP: MSI предлагает A-XMP, [27] У ASUS есть DOCP (Direct Over Clock Profile), а у Gigabyte — EOCP (расширенный профиль Over Clock). [28]

| Байты DDR3 | Размер | Использовать |

|---|---|---|

| 176–184 | 10 | XMP-заголовок |

| 185–219 | 33 | Профиль XMP 1 (настройки «энтузиаста») |

| 220–254 | 36 | Профиль XMP 2 («экстремальные» настройки) |

Заголовок содержит следующие данные. Самое главное, что он содержит значение MTB «средней временной развертки» как рациональное число наносекунд (обычные значения: 1/8, 1/12 и 1/16 нс). Многие другие более поздние значения синхронизации выражаются как целое число единиц MTB.

В заголовок также включено количество модулей DIMM на канал памяти, для поддержки которых предназначен профиль; включение большего количества модулей DIMM может оказаться неэффективным.

| DDR3 Байт | Биты | Использовать |

|---|---|---|

| 176 | 7:0 | XMP, Магическое число байт 1 0x0C |

| 177 | 7:0 | Магическое число XMP, байт 2 0x4A |

| 178 | 0 | Профиль 1 включен (если 0, отключен) |

| 1 | Профиль 2 включен | |

| 3:2 | Профиль 1 модуль DIMM на канал (1–4 закодирован как 0–3) | |

| 5:4 | Профиль: 2 модуля DIMM на канал | |

| 7:6 | Сдержанный | |

| 179 | 3:0 | Дополнительный номер версии XMP (x.0 или x.1) |

| 7:4 | Основной номер версии XMP (0.x или 1.x) | |

| 180 | 7:0 | Средневременной дивиденд для профиля 1 |

| 181 | 7:0 | Делитель средней временной развертки для профиля 1 (MTB = делимое/делитель ns) |

| 182 | 7:0 | Средневременной дивиденд для профиля 2 (например, 8) |

| 183 | 7:0 | Делитель средней временной развертки для профиля 2 (например, 1, что дает MTB = 1/8 нс) |

| 184 | 7:0 | Сдержанный |

| DDR3 Байт 1 | DDR3 Байт 2 | Биты | Использовать |

|---|---|---|---|

| 185 | 220 | 0 | Модуль Vdd напряжения двадцатых (0,00 или 0,05) |

| 4:1 | Модуль напряжения Vdd, десятые доли (0,0–0,9) | ||

| 6:5 | Единицы измерения напряжения модуля Vdd (0–2) | ||

| 7 | Сдержанный | ||

| 186 | 221 | 7:0 | Минимальный период тактовой частоты SDRAM t CK min (единицы MTB) |

| 187 | 222 | 7:0 | Минимальное время задержки CAS t AA min (единицы MTB) |

| 188 | 223 | 7:0 | Поддерживаются задержки CAS (растровое изображение, 4–11, закодированное как биты 0–7) |

| 189 | 224 | 6:0 | Поддерживаются задержки CAS (растровое изображение, 12–18, закодированное как биты 0–6) |

| 7 | Сдержанный | ||

| 190 | 225 | 7:0 | Минимальное время задержки записи CAS t CWL min (единицы MTB) |

| 191 | 226 | 7:0 | Минимальное время задержки предварительной зарядки ряда t RP min (единиц MTB) |

| 192 | 227 | 7:0 | Минимальное время задержки между RAS и CAS t RCD min (блоки MTB) |

| 193 | 228 | 7:0 | Минимальное время восстановления записи t WR min (единицы MTB) |

| 194 | 229 | 3:0 | t RAS мин. верхний полубайт (биты 11:8) |

| 7:4 | t RC min старший полубайт (биты 11:8) | ||

| 195 | 230 | 7:0 | Минимальное время задержки активации для предварительной зарядки t RAS , мин. биты 7:0 (единицы MTB) |

| 196 | 231 | 7:0 | Минимальное время задержки перехода от активного к активному/обновлению t Минимальные биты RC 7:0 (модули MTB) |

| 197 | 232 | 7:0 | Максимальный средний интервал обновления t REFI lsbyte (единицы MTB) |

| 198 | 233 | 7:0 | Максимальный средний интервал обновления t REFI мсбайт (единицы MTB) |

| 199 | 234 | 7:0 | Минимальное время задержки восстановления после обновления t RFC min lsbyte (единицы MTB) |

| 200 | 235 | 7:0 | Минимальное время задержки восстановления после обновления t RFC мин мсбайт (единицы MTB) |

| 201 | 236 | 7:0 | Минимальное время задержки внутреннего чтения для команды предварительной зарядки t RTP min (единицы MTB) |

| 202 | 237 | 7:0 | Минимальное время задержки между активными строками t RRD min (единицы MTB) |

| 203 | 238 | 3:0 | t FAW мин. верхний полубайт (биты 11:8) |

| 7:4 | Сдержанный | ||

| 204 | 239 | 7:0 | Минимум четыре времени задержки активации окна t FAW мин. биты 7:0 (блоки MTB) |

| 205 | 240 | 7:0 | Минимальное время задержки внутренней команды записи для чтения t WTR min (единицы MTB) |

| 206 | 241 | 2:0 | Регулировка времени выполнения команды записи для чтения (0–7 тактов) |

| 3 | Знак регулировки поворота команды записи и чтения (0 = втягивание, 1 = выталкивание) | ||

| 6:4 | Регулировка времени цикла чтения и записи команды (0–7 тактов) | ||

| 7 | Знак регулировки поворота команды чтения для записи (0 = втягивание, 1 = выталкивание) | ||

| 207 | 242 | 2:0 | Регулировка времени выполнения обратной команды (0–7 тактовых циклов) |

| 3 | Знак регулировки обратного поворота (0 = втягивание, 1 = выталкивание) | ||

| 7:4 | Сдержанный | ||

| 208 | 243 | 7:0 | Системный режим скорости CMD. 0 = JTAG по умолчанию, в противном случае — в особых единицах MTB × t CK /нс. Например, если MTB составляет 1/8 нс, то это значение измеряется в 1/8 такта. |

| 209 | 244 | 7:0 | Производительность автоматического самообновления SDRAM. В стандартной версии 1.1 указано, что документация подлежит уточнению . |

| 210–218 | 245–253 | 7:0 | Сдержанный |

| 219 | 254 | 7:0 | Зарезервированный персональный код, зависящий от поставщика. |

Все приведенные выше данные относятся к DDR3 (XMP 1.1); Спецификации DDR4 пока недоступны.

Расширенные профили AMD для разгона (EXPO)

[ редактировать ]Расширенные профили для разгона AMD (EXPO) — это расширение JEDEC SPD, разработанное для модулей DIMM DDR5 для применения профиля автоматического разгона одним щелчком мыши к системной памяти. [30] [31] Модули DIMM, сертифицированные AMD EXPO, включают оптимизированные тайминги, которые оптимизируют производительность процессоров Zen 4 . [32] В отличие от закрытого стандарта Intel XMP, стандарт EXPO является открытым и не требует лицензионных отчислений. [31] Его можно использовать на платформах Intel. [31] На момент запуска в сентябре 2022 года будет доступно 15 партнерских комплектов RAM с EXPO-сертификацией, обеспечивающих скорость до 6400 МТ/с. [33]

Память конкретного производителя

[ редактировать ]Распространенным злоупотреблением является запись информации в определенные области памяти для привязки модулей памяти конкретного поставщика к конкретной системе. Fujitsu Technology Solutions Известно, что делает это. Добавление в систему другого модуля памяти обычно приводит к отказу или другим контрмерам (например, нажатию F1 при каждой загрузке).

02 0E 00 01-00 00 00 EF-02 03 19 4D-BC 47 C3 46 ...........M.G.F 53 43 00 04-EF 4F 8D 1F-00 01 70 00-01 03 C1 CF SC...O....p.....

Это результат модуля памяти емкостью 512 МБ от Micron Technologies, выпускаемого под брендом Fujitsu-Siemens Computers, обратите внимание на строку «FSC». Системный BIOS отклоняет модули памяти, которые не имеют этой информации, начиная со смещения 128h.

Некоторые ноутбуки Packard Bell AMD также используют этот метод. В этом случае симптомы могут различаться, но это может привести к миганию курсора, а не к звуковому сигналу. Кстати, это также может быть признаком повреждения BIOS. [34] Хотя обновление 2 ГБ до 4 ГБ также может привести к проблемам.

Чтение и запись информации SPD

[ редактировать ]Производители модулей памяти записывают информацию SPD в EEPROM модуля. материнской платы BIOS считывает информацию SPD для настройки контроллера памяти. Существует несколько программ, которые могут читать и изменять информацию SPD на большинстве, но не на всех чипсетах материнских плат.

- dmidecode программа, способная декодировать информацию о памяти (и других вещах) и работающая в Linux , FreeBSD , NetBSD , OpenBSD , BeOS , Cygwin и Solaris . dmidecode не имеет прямого доступа к информации SPD; он сообщает данные SMBIOS о памяти. [35] Эта информация может быть ограниченной или неверной.

- В системах Linux и FreeBSD программа decode-dimms пользовательского пространства , предоставляемая i2c-tools, декодирует и печатает информацию в любой памяти с информацией SPD на компьютере. [36] [37] Для этого требуется поддержка контроллера SMBus в ядре, драйвер ядра EEPROM, а также подключение EEPROM SPD к SMBus. В старых дистрибутивах Linux decode-dimms.pl был доступен как часть lm_sensors .

- Начиная с версии 4.3, в OpenBSD включен драйвер ( spdmem(4) ) для предоставления информации о модулях памяти. Драйвер портирован из NetBSD, где он доступен с версии 5.0.

- Coreboot считывает и использует информацию SPD для инициализации всех контроллеров памяти на компьютере с указанием времени, размера и других свойств.

- Системы Windows используют такие программы, как HWiNFO , [38] CPU-Z и Speccy , которые могут считывать и отображать информацию о модуле DRAM из SPD.

Независимое от набора микросхем чтение и запись информации SPD осуществляется путем прямого доступа к EEPROM памяти с помощью аппаратного и программного обеспечения программатора EEPROM.

Старые ноутбуки не так часто используются в качестве обычных считывателей SMBus, поскольку внутреннюю EEPROM на модуле можно отключить после того, как BIOS ее прочитает, и шина по существу будет доступна для использования. Используемый метод заключается в понижении уровня напряжения на линиях A0, A1, чтобы внутренняя память отключилась, позволяя внешнему устройству получить доступ к SMBus. Как только это будет сделано, специальная сборка Linux или приложение DOS смогут получить доступ к внешнему устройству. Обычно используется восстановление данных из микросхем памяти ЖК-панели для модернизации стандартной панели в фирменном ноутбуке. На некоторых микросхемах также рекомендуется разделить линии защиты от записи, чтобы встроенные микросхемы не были стерты во время перепрограммирования. Связанный с этим метод — перезапись чипа на веб-камерах, часто входящих в состав многих ноутбуков, поскольку скорость шины существенно выше и даже может быть изменена так, чтобы чипы, совместимые с 25x, можно было считывать обратно для последующего клонирования uEFI в случае сбоя чипа.

К сожалению, это работает только с DDR3 и ниже, поскольку DDR4 использует другую безопасность и обычно может быть только прочитан. Можно использовать такой инструмент, как SPDTool или аналогичный, и заменить чип на тот, у которого линия WP свободна, чтобы его можно было изменить на месте. На некоторых чипсетах появляется сообщение «Несовместимый драйвер SMBus?» может быть видно, поэтому чтение также запрещено.

Управление RGB-светодиодом

[ редактировать ]Некоторые модули памяти (особенно на игровых ПК ) [39] поддержка светодиодов RGB, которые управляются собственными командами SMBus. Это позволяет управлять цветом светодиодов без дополнительных разъемов и кабелей. Драйверы ядра от нескольких производителей, необходимые для управления подсветкой, неоднократно использовались для получения доступа, начиная от полного доступа к памяти ядра и заканчивая MSR и управлением портами ввода-вывода, только в 2020 году. [40] [41] [42]

На старом оборудовании

[ редактировать ]Некоторое старое оборудование требует использования модулей SIMM с параллельным обнаружением присутствия (чаще называемое просто обнаружением присутствия или PD). В некотором из этого оборудования используется нестандартное кодирование PD, компьютеры IBM , Hewlett-Packard LaserJet в частности, и другие принтеры.

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ Томас П. Кениг; Натан Джон (3 февраля 1997 г.), «Обнаружение серийного присутствия готово к всеобщему вниманию» , Electronic News , 43 (2153)

- ^ Стандарт JEDEC 21-C, раздел 4.1.4 «Определение EEPROM TSE2002av Serial Presence Detect (SPD) с датчиком температуры (TS) для приложений модуля памяти»

- ^ «TN-04-42: Защита от записи при обнаружении последовательного присутствия модуля памяти» (PDF) . Микрон .

- ^ Дин Кент (24 октября 1998 г.). «Рам Гид» . Аппаратное обеспечение Тома .

- ^ Шимпи, Ананд Лал. «PC100 SDRAM: Введение» . www.anandtech.com .

- ^ Примечание по применению INN-8668-APN3: Стандарты данных SDRAM SPD , Memorytesters.com

- ^ Спецификация обнаружения последовательного присутствия PC SDRAM (SPD) (PDF) , 1.2A, декабрь 1997 г., стр. 28

- ^ Перейти обратно: а б Стандарт JEDEC 21-C, раздел 4.1.2.4 «SPD для DDR SDRAM»

- ^ Перейти обратно: а б Стандарт JEDEC 21-C, раздел 4.1.2.10 «Специальные SPD для DDR2 SDRAM»

- ^ «Понимание таблицы обнаружения последовательного присутствия (SPD) DDR3» .

- ^ JESD21-C Приложение K: Обнаружение последовательного присутствия для модулей DDR3 SDRAM , версия 4, версия SPD 1.1

- ^ JESD21-C Приложение K: Обнаружение последовательного присутствия для модулей DDR3 SDRAM , выпуск 6, версия SPD 1.3

- ^ Дельвар, Жан. «[ИСПРАВЛЕНИЕ] eeprom: Новый драйвер ee1004 для памяти DDR4» . ЛКМЛ . Проверено 7 ноября 2019 г.

- ^ Перейти обратно: а б ДЖЕДЕК. «Приложение L: Обнаружение последовательного присутствия (SPD) для модулей DDR4 SDRAM» (PDF) .

- ^ ДЖЕДЕК. «Спецификация устройства EE1004 и TSE2004 (проект)» (PDF) . Проверено 7 ноября 2019 г.

- ^ JESD21-C Приложение L: Обнаружение последовательного присутствия для модулей DDR4 SDRAM , выпуск 5

- ^ «JESD400-5B(JESD400-5B)» . джедек . 2023 . Проверено 31 декабря 2023 г.

- ^ Стандарт JEDEC 21-C, раздел 4.1.2.11 «Обнаружение последовательного присутствия (SPD) для модулей DDR3 SDRAM»

- ^ Стандарт JEDEC 21-C, раздел 4.1.2 «СТАНДАРТ ОБНАРУЖЕНИЯ ПОСЛЕДОВАТЕЛЬНОГО ПРИСУТСТВИЯ, Общий стандарт»

- ^ Стандарт JEDEC 21-C, раздел 4.1.2.5 «Особые PD для синхронной DRAM (SDRAM)»

- ^ Спецификация дизайна профилей улучшенной производительности DDR2 UDIMM (PDF) , Nvidia , 12 мая 2006 г. , дата обращения 5 мая 2009 г.

- ^ http://www.nvidia.com/docs/CP/45121/sli_memory.pdf [ только URL-адрес PDF ]

- ^ Расширенные профили производительности 2.0 (стр. 2–3).

- ^ «Что такое профиль памяти Intel Extreme Memory (Intel XMP)?» . Интел . Проверено 26 сентября 2022 г.

- ^ «Технология профиля памяти — увеличьте объем оперативной памяти» . АМД . 2012 . Проверено 8 января 2018 г.

- ^ Мартин, Райан (23 июля 2012 г.). «AMD представляет XMP-эквивалент AMP — eTeknix» . еТехникс . Проверено 8 января 2018 г.

- ^ «MSI — первый в мире бренд, внедривший A-XMP на Ryzen для обеспечения максимальной производительности DDR4, запускает новые модели» . МСИ . 21 марта 2017 года . Проверено 8 января 2018 г.

- ^ Торговец1 (26 августа 2016 г.). «Что означает XMP, DOCP, EOCP — Решено — Память» . Форумы Тома по аппаратному обеспечению . Проверено 8 января 2018 г.

{{cite web}}: CS1 maint: числовые имена: список авторов ( ссылка ) - ^ Перейти обратно: а б с «Спецификация профиля Intel Extreme Memory (XMP), версия 1.1» (PDF) . Интел . Октябрь 2007 г. Архивировано из оригинала (PDF) 6 марта 2012 г. . Проверено 25 мая 2010 г.

- ^ «Расширенные профили AMD для разгона» . АМД . Проверено 26 сентября 2022 г.

- ^ Перейти обратно: а б с Роуч, Джейкоб (6 сентября 2022 г.). «Что такое AMD EXPO и должна ли она быть у моей DDR5?» . Цифровые тенденции . Проверено 26 сентября 2022 г.

- ^ Боншор, Гэвин (30 августа 2022 г.). «Технология памяти AMD EXPO: профили разгона в один клик для Ryzen 7000» . АнандТех . Проверено 26 сентября 2022 г.

- ^ «AMD анонсирует технологию EXPO для разгона памяти DDR5» . ВидеоКардз . 30 августа 2022 г. Проверено 26 сентября 2022 г.

- ^ «Обновление оперативной памяти Packard Bell LJ65» . Аппаратный форум Тома . 9 января 2014 г.

- ^ "dmidecode: Для чего это нужно?" . Linux.com | Источник информации о Linux . 29 ноября 2004 г.

- ^ "декодировать-диммс(1)" . Страница руководства Debian . Проверено 16 декабря 2020 г.

- ^ "декодирование-затемнение" . www.freebsd.org . Проверено 24 января 2021 г.

- ^ «HWiNFO — Профессиональная системная информация и диагностика» . ХВИНФО .

- ^ «Память DDR4 серии VENGEANCE RGB PRO | Память для настольных ПК | CORSAIR» . www.corsair.com . Проверено 26 ноября 2020 г.

- ^ АктивКибер. Повышение локальных привилегий драйвера Viper RGB (технический отчет). CVE - 2019-18845 – через корпорацию MITRE.

- ^ АктивКибер. Повышение локальных привилегий драйвера CORSAIR iCUE (CVE-2020-8808) (технический отчет). CVE - 2020-8808 – через корпорацию MITRE.

- ^ АктивКибер. ACTIVE-2020-003: Повышение локальных привилегий драйвера управления освещением Trident Z (технический отчет). CVE - 2020-12446 – через корпорацию MITRE.

Внешние ссылки

[ редактировать ]- Стандарт обнаружения присутствия последовательного порта, общий стандарт

- SPD Rev1.0 для DDR SDRAM

- SPD Rev1.2 для DDR2 SDRAM

- SPD Rev1.3 для DDR2 SDRAM

- СПЕЦИАЛЬНАЯ DDR2-1066 SDRAM

- Linux-пакет i2c-tools

- Инструкции по использованию lm-сенсоров или i2c-инструментов для считывания данных. Архивировано 19 мая 2007 г. на Wayback Machine.

- Производительность памяти: от 16 ГБ от DDR3-1333 до DDR3-2400 на Ivy Bridge IGP с G.Skill – объяснение различных значений таймингов