Приоритетный кодер

— Приоритетный кодер это схема или алгоритм , который сжимает несколько двоичных входов в меньшее количество выходов, аналогично простому кодировщику . Выходной сигнал приоритетного кодера представляет собой двоичное представление индекса наиболее значимой активированной строки. В отличие от простого кодера, если два или более входов приоритетного кодера активны одновременно, вход, имеющий наивысший приоритет, будет иметь приоритет . Это улучшение простого кодера, поскольку оно может обрабатывать все возможные входные комбинации, но за счет дополнительной логики. [1]

Приложения приоритетных кодировщиков включают их использование в контроллерах прерываний (чтобы некоторые запросы прерываний имели более высокий приоритет, чем другие), десятичное или двоичное кодирование , а также аналого-цифровое / цифро-аналоговое преобразование. [2]

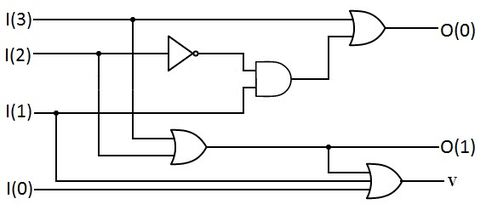

Показана таблица истинности однобитового кодера с приоритетом 4 к 2, где входные данные показаны в порядке убывания приоритета слева направо, а «x» указывает на неважный термин , то есть любое входное значение там. дает тот же результат, поскольку он заменяется входом с более высоким приоритетом. (обычно включенный [а] ) Выход «v» указывает, действителен ли ввод.

| Вход | Выход | |||||

| я 3 | я 2 | я 1 | я 0 | О 1 | О 0 | v |

| 0 | 0 | 0 | 0 | х | 0 | |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | х | 0 | 1 | 1 |

| 0 | 1 | х | 1 | 0 | 1 | |

| 1 | х | 1 | 1 | 1 | ||

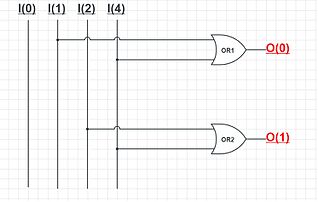

Приоритетные энкодеры можно легко объединить в массивы для создания более крупных энкодеров, например, один кодер 16:4, состоящий из шести приоритетных энкодеров 4:2 – четыре энкодера 4:2, источник сигнала которых подключен к их входам, и два оставшихся кодера принимают на вход выходные данные первых четырех.

Рекурсивное построение приоритетных кодировщиков [3] [4] [5]

[ редактировать ]Приоритетный энкодер, также называемый детектором ведущих нулей (LZD) или счетчиком ведущих нулей (LZC), получает сигнал -битный входной вектор и определяет индекс первой двоичной '1' во входном векторе. Действительный сигнал указывает, была ли обнаружена двоичная единица во входном векторе, следовательно, индекс действителен.

Приоритетные кодировщики могут быть эффективно созданы с помощью рекурсии. Входной вектор разбивается на равные фрагменты с биты. Приоритетный кодер с более узкой шириной 𝑛/𝑘 применяется для каждого фрагмента. Действительный бит каждого из идет в кусочек для обнаружения первого допустимого фрагмента. Местоположение этого фрагмента является верхней частью общего индекса и определяет точное местоположение внутри самого фрагмента для создания нижней части общего индекса.

Глубина предлагаемой конструкции составляет , а сложность аппаратной области . Если используется Stratix V компании Altera или эквивалентное устройство, рекомендуется для достижения более высокой производительности и сжатия области, поскольку мультиплексор может быть реализован с использованием 6-LUT, а значит, и всего ALM.

Генератор Verilog с открытым исходным кодом для рекурсивного кодировщика приоритетов доступен в Интернете. [6]

Поведенческое описание приоритетного кодировщика в Verilog выглядит следующим образом. [6]

// behavioural description of priority enconder;

// https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM

module pe_bhv

#( parameter OHW = 512 ) // encoder one-hot input width

( input clk , // clock for pipelined priority encoder

input rst , // registers reset for pipelined priority encoder

input [ OHW -1:0] oht , // one-hot input / [ OHW -1:0]

output reg [`log2(OHW)-1:0] bin , // first '1' index/ [`log2(OHW)-1:0]

output reg vld ); // binary is valid if one was found

// use while loop for non fixed loop length

// synthesizable well with Intel's QuartusII

always @(*) begin

bin = {`log2(OHW){1'b0}};

vld = oht[bin] ;

while ((!vld) && (bin!=(OHW-1))) begin

bin = bin + 1 ;

vld = oht[bin];

end

end

endmodule

Простой кодер

[ редактировать ]

Простая схема энкодера представляет собой преобразователь «один горячий» в двоичный. То есть, если есть 2 н входных строк, и не более чем одна из них когда-либо будет высокой, двоичный код этой «горячей» строки создается в n -битных выходных строках.

Примечания

[ редактировать ]- ^ Например, кодер 74x147 с преобразованием 10 в 4 приоритетный BCD- не имеет выделенного выходного действительного сигнала. Однако недействительность отображается одновременно высоким уровнем на всех выходах. https://www.ti.com/lit/ds/symlink/sn74ls148.pdf

Ссылки

[ редактировать ]- ^ Мано, Моше Моррис; Силетти, Майкл Д. (2007). Цифровой дизайн (Четвертое изд.). Река Аппер-Сэддл, Нью-Джерси: Пирсон Прентис Холл. п. 156. ИСБН 978-0-13-198924-5 .

- ^ Справочник по приложениям TTL . Фэйрчайлд Полупроводник. Август 1973 г. с. 4-4.

- ^ Абдельхади, Амир М.С. (2016). Архитектура массивно-параллельных структур памяти на основе блочного ОЗУ: многопортовая память и память с контентной адресацией (Диссертация). Университет Британской Колумбии.

- ^ Абдельхади, Амир М.С.; Лемье, Гай Г.Ф. (май 2015 г.). «Модульные двоичные памяти с адресацией по содержимому на основе SRAM». 23-й ежегодный международный симпозиум IEEE по программируемым пользовательским вычислительным машинам , 2015 г. стр. 207–214. дои : 10.1109/FCCM.2015.69 . ISBN 978-1-4799-9969-9 . S2CID 16985129 .

- ^ Абдельхади, Амир М.С.; Лемье, Гай Г.Ф. (декабрь 2014 г.). «Глубокая и узкая память с адресацией двоичного содержимого с использованием BRAM на основе FPGA». 2014 Международная конференция по программируемым технологиям (FPT) . стр. 318–321. дои : 10.1109/FPT.2014.7082808 . ISBN 978-1-4799-6245-7 . S2CID 2074456 .

- ^ Jump up to: а б Абдельхади, AMS; Лемье, GGF (2014). «Модульная адресуемая память 2D с двоичным контентом на основе SRAM II2DCAM» . Университет Британской Колумбии.

Абдельхади, AMS; Лемье, GGF (2015). «Модульные двоичные памяти с адресацией по содержимому на основе SRAM» (PDF) . 2015 23-й ежегодный международный симпозиум IEEE по программируемым пользовательским вычислительным машинам . IEEE. стр. 207–214. дои : 10.1109/FCCM.2015.69 . ISBN 978-1-4799-9969-9 . S2CID 16985129 .