Счетчик отметок времени

Эта статья нуждается в дополнительных цитатах для проверки . ( апрель 2012 г. ) |

Счетчик меток времени ( TSC ) — это 64-битный регистр, присутствующий на всех x86, процессорах начиная с Pentium . Он подсчитывает количество циклов процессора с момента его сброса. Инструкция RDTSC возвращает TSC в EDX:EAX. В x86-64 режиме RDTSC также очищает старшие 32 бита RAX и RDX . Его код операции 0F 31. [1] Конкуренты Pentium, такие как Cyrix 6x86, не всегда имели TSC и могут рассмотреть возможность RDTSC незаконное указание. Cyrix включила счетчик отметок времени в свой MII .

Использовать

[ редактировать ]Счетчик отметок времени когда-то был способом с высоким разрешением и низкими издержками, позволяющим программе получать информацию о синхронизации процессора. С появлением многоядерных / гиперпоточных процессоров, систем с несколькими процессорами и , находящихся в спящем режиме операционных систем , на TSC нельзя полагаться в предоставлении точных результатов — если не уделять должного внимания исправлению возможных недостатков: скорости такта и все ядра (процессоры) имеют одинаковые значения в своих регистрах хранения времени. Нет никаких гарантий, что счетчики временных меток нескольких процессоров на одной материнской плате будут синхронизированы. Следовательно, программа может получить надежные результаты, только ограничившись выполнением на одном конкретном процессоре. Даже в этом случае скорость ЦП может измениться из-за мер по энергосбережению, принятых ОС или BIOS , или система может перейти в режим гибернации, а затем возобновить работу со сбросом TSC. В последних случаях, чтобы оставаться актуальной, программа должна периодически перекалибровывать счетчик.

Использование TSC также снижает мобильность, поскольку другие процессоры могут не иметь аналогичной функции. Последние процессоры Intel включают TSC с постоянной скоростью (идентифицируемый системным файлом kern.timecounter.invariant_tsc во FreeBSD или " constant_tsc" флаг в Linux /proc/cpuinfo). В этих процессорах TSC работает на номинальной частоте процессора, независимо от фактической тактовой частоты процессора из-за режимов турбо или энергосбережения. Следовательно, тики TSC подсчитывают время, а не количество прошедших тактов процессора.

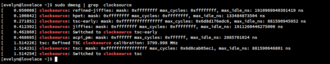

На платформах Windows Microsoft настоятельно не рекомендует использовать TSC для синхронизации с высоким разрешением именно по этим причинам, предоставляя вместо этого API-интерфейсы Windows. QueryPerformanceCounter и QueryPerformanceFrequency (который сам использует RDTSCP, если в системе имеется инвариантный TSC, т.е. частота TSC не меняется в зависимости от текущей частоты ядра). [2] В системах Linux программа может получить аналогичную функцию, прочитав значение CLOCK_MONOTONIC_RAW часы с помощью clock_gettime функция. [3]

Начиная с Pentium Pro , в процессорах Intel практикуется выполнение вне порядка , когда инструкции не обязательно выполняются в том порядке, в котором они появляются в программе. Это может привести к тому, что процессор выполнит RDTSC раньше, чем ожидает простая программа, что приводит к вводящему в заблуждение количеству циклов. [4] Программист может решить эту проблему, вставив инструкцию сериализации, например CPUID , чтобы принудительно завершить каждую предыдущую инструкцию, прежде чем программа сможет продолжить работу. RDTSCP инструкция представляет собой вариант RDTSC который предполагает частичную сериализацию потока команд, но не должен рассматриваться как сериализация.

Реализация в различных процессорах

[ редактировать ]Семейства процессоров Intel увеличивают счетчик меток времени по-разному: [5]

- Для процессоров Pentium M (семейство [06H], модели [09H, 0DH]); для процессоров Pentium 4 — процессоры Intel Xeon (семейство [0FH], модели [00H, 01H или 02H]); а для процессоров семейства P6: счетчик меток времени увеличивается с каждым тактом внутреннего процессора. Тактовый цикл внутреннего процессора определяется текущим соотношением частоты ядра и частоты шины. Переход на технологию Intel SpeedStep также может повлиять на тактовую частоту процессора.

- Для процессоров Pentium 4 , процессоров Intel Xeon (семейство [0FH], модели [03H и выше]); для процессоров Intel Core Solo и Intel Core Duo (семейство [06H], модель [0EH]); для процессоров Intel Xeon серии 5100 и процессоров Intel Core 2 Duo (семейство [06H], модель [0FH]); для процессоров Intel Core 2 и Intel Xeon (семейство [06H], display_model [17H]); для процессоров Intel Atom (семейство [06H], display_model [1CH]): счетчик отметок времени увеличивается с постоянной скоростью. Эта частота может быть установлена максимальным отношением тактовой частоты ядра к тактовой частоте шины процессора или максимальной разрешенной частотой, с которой загружается процессор. Максимальная разрешенная частота может отличаться от максимальной квалифицированной частоты процессора.

Конкретная конфигурация процессора определяет поведение. Постоянное поведение TSC гарантирует, что продолжительность каждого такта часов одинакова, и позволяет использовать TSC в качестве настенного таймера, даже если ядро процессора меняет частоту. Это архитектурное поведение всех более поздних процессоров Intel.

Процессоры AMD вплоть до ядра K8 всегда увеличивали счетчик меток времени каждый такт. [6] Таким образом, функции управления питанием могли изменять количество приращений в секунду, и значения могли рассинхронизироваться между разными ядрами или процессорами в одной системе. Для Windows AMD предоставляет утилиту [7] для периодической синхронизации счетчиков на нескольких ядерных процессорах.

Начиная с семейства 10h (Barcelona/Phenom), чипы AMD имеют постоянный TSC, который может управляться либо скоростью HyperTransport , либо самым высоким состоянием P. Бит CPUID ( Fn8000_0007:EDX_8) рекламирует это; Процессоры Intel также сообщают об этом инвариантном TSC.

Использование операционной системы

[ редактировать ]Операционная система может предоставлять методы, которые как используют, так и не используют RDTSC инструкция по хронометражу, под контролем администратора. Например, в некоторых версиях ядра режим Linux песочницы seccomp отключает RDTSC. [8] Его также можно отключить с помощью PR_SET_TSC аргумент в пользу prctl() системный вызов. [9]

Использование при атаках по побочному каналу кэша.

[ редактировать ]Счетчик отметок времени можно использовать для точного определения времени выполнения инструкций, что может быть использовано при уязвимостях безопасности Meltdown и Spectre . [10] [11] Однако, если он недоступен, можно использовать другие счетчики или таймеры, как в случае с процессорами ARM , уязвимыми для атак такого типа.

Другие архитектуры

[ редактировать ]Другие процессоры также имеют регистры, подсчитывающие тактовые циклы ЦП, но с другими именами. Например, в AVR32 он называется регистром счетчика тактовой частоты (PCCNT). SPARC V9 обеспечивает TICK зарегистрироваться. PowerPC обеспечивает 64-битную TBR зарегистрироваться.

ARMv7 [12] и ARMv8-A [13] архитектуры предоставляют общий счетчик, который считает с постоянной частотой. ARMv7 предоставляет регистр счетчика циклов ( CCNT инструкция) для чтения и записи счетчика, но эта инструкция является привилегированной. [14]

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ Руководство разработчика программного обеспечения для архитектур Intel 64 и IA-32, том 2B: Справочник по набору команд, MZ (PDF) . п. 545.

- ^ Игровое время и многоядерные процессоры . стр. 251–252.

- ^ «lock_getres, clock_gettime, clock_settime — функции часов и таймера» .

- ^ «Использование инструкции RDTSC для мониторинга производительности» (PDF) .

- ^ «Том 3А, глава 16». Руководство разработчика программного обеспечения для архитектур Intel 64 и IA-32 .

- ^ «Том 3». Руководство программиста по архитектуре AMD64 .

- ^ «Двуядерный оптимизатор AMD» .

- ^ «Блог cr0: Счетчик временных меток, отключающий странности в ядре Linux» . Май 2009.

- ^ – Linux программиста Руководство – Системные вызовы

- ^ "meltdown.c" .

- ^ "спектр.с" .

- ^ «Справочное руководство по ARMv7» .

- ^ «Справочное руководство по ARMv8» .

- ^ «Регистр счетчика циклов (CCNT)» . ARM Ltd. Проверено 5 марта 2021 г.

Внешние ссылки

[ редактировать ]- Cycle.h — код C для чтения таймера высокого разрешения на многих процессорах и компиляторах.

- Инженер AMD о дрейфе TSC в процессорах AMD