Симметричная многопроцессорная обработка

Эта статья нуждается в дополнительных цитатах для проверки . ( ноябрь 2012 г. ) |

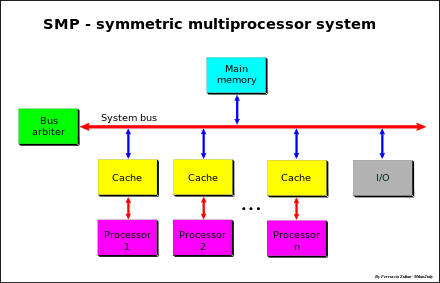

Симметричная многопроцессорная обработка или многопроцессорная обработка с общей памятью [1] ( SMP ) включает в себя многопроцессорную компьютерную аппаратную и программную архитектуру, в которой два или более идентичных процессора подключены к одной общей основной памяти , имеют полный доступ ко всем устройствам ввода и вывода и управляются одним экземпляром операционной системы, который обрабатывает все процессоры. в равной степени, не оставляя ни одного для особых целей. Большинство многопроцессорных систем сегодня используют архитектуру SMP. В случае многоядерных процессоров архитектура SMP применяется к ядрам, рассматривая их как отдельные процессоры.

Профессор Джон Д. Кубятович считает, что традиционно SMP-системы содержат процессоры без кэшей. [2] Каллер и Пал-Сингх в своей книге 1998 года «Параллельная компьютерная архитектура: аппаратно-программный подход» упоминают: «Термин SMP широко используется, но вызывает некоторую путаницу. [...] Более точное описание того, что подразумевается под SMP — это мультипроцессор с общей памятью, в котором стоимость доступа к ячейке памяти одинакова для всех процессоров; то есть затраты на доступ одинаковы, когда доступ фактически осуществляется к памяти. Если область кэшируется, доступ будет быстрее, но будет быстрее. время доступа к кэшу и время доступа к памяти одинаково на всех процессорах». [3]

Системы SMP — это тесно связанные многопроцессорные системы с пулом однородных процессоров, работающих независимо друг от друга. Каждый процессор, выполняющий разные программы и работающий с разными наборами данных, имеет возможность совместного использования общих ресурсов (памяти, устройства ввода-вывода, системы прерываний и т. д.), которые соединяются с помощью системной шины или кроссбара .

Дизайн [ править ]

Системы SMP имеют централизованную разделяемую память, называемую основной памятью (MM), работающую под управлением одной операционной системы с двумя или более однородными процессорами. Обычно каждый процессор имеет связанную с ним частную высокоскоростную память, известную как кэш-память (или кэш), для ускорения доступа к данным основной памяти и уменьшения трафика системной шины.

Процессоры могут быть соединены между собой с помощью шин, перекрестных переключателей или ячеистых сетей на кристалле. Узким местом в масштабируемости SMP с использованием шин или перекрестных коммутаторов является пропускная способность и энергопотребление соединения между различными процессорами, памятью и дисковыми массивами. Ячеистые архитектуры позволяют избежать этих узких мест и обеспечивают почти линейную масштабируемость до гораздо большего числа процессоров, жертвуя программируемостью:

С такой архитектурой остаются серьезные проблемы программирования, поскольку она требует двух различных режимов программирования; один для самих процессоров и один для соединения между процессорами. Единый язык программирования должен быть способен не только распределять рабочую нагрузку, но и учитывать локальность памяти, что является серьезной проблемой в ячеистой архитектуре. [4]

Системы SMP позволяют любому процессору работать над любой задачей независимо от того, где в памяти расположены данные для этой задачи, при условии, что каждая задача в системе не выполняется на двух или более процессорах одновременно. При надлежащей поддержке операционной системы системы SMP могут легко перемещать задачи между процессорами для эффективной балансировки рабочей нагрузки.

История [ править ]

Самой ранней производственной системой с несколькими идентичными процессорами была Burroughs B5000 , которая начала функционировать примерно в 1961 году. Однако во время работы она была асимметричной : один процессор был ограничен прикладными программами, в то время как другой процессор в основном обрабатывал операционную систему и аппаратные прерывания. В Burroughs D825 впервые реализован SMP в 1962 году. [5] [6]

IBM предложила двухпроцессорные компьютерные системы на основе своей System/360 Model 65 и близкой ей Model 67. [7] и 67–2. [8] На этих машинах работали операционные системы OS/360 M65MP. [9] и ТСС/360 . Другое программное обеспечение, разработанное в университетах, в частности Michigan Terminal System (MTS), использовало оба процессора. Оба процессора могли получать доступ к каналам данных и инициировать ввод-вывод. В OS/360 M65MP периферийные устройства обычно можно было подключить к любому процессору, поскольку ядро операционной системы работало на обоих процессорах (хотя и с «большой блокировкой» вокруг обработчика ввода-вывода). [10] Супервизор MTS (UMMPS) может работать на обоих процессорах IBM System/360 модели 67–2. Блокировки супервизора были небольшими и использовались для защиты отдельных общих структур данных, к которым можно было получить доступ одновременно с любого ЦП. [11]

Другие мэйнфреймы, поддерживавшие SMP, включали UNIVAC 1108 II , выпущенный в 1965 году и поддерживавший до трех ЦП, а также GE-635 и GE-645 . [12] [13] хотя GECOS в многопроцессорных системах GE-635 работал асимметрично по принципу «главный-подчиненный», в отличие от Multics в многопроцессорных системах GE-645, которые работали симметрично. [14]

Начиная с версии 7.0 (1972 г.), компании Digital Equipment Corporation операционная система TOPS-10 реализовала функцию SMP, самой ранней системой, работающей с SMP, была DECSystem 1077 KI10. двухпроцессорная система [15] Более поздняя система KL10 могла объединять до 8 процессоров по принципу SMP. Напротив, первая многопроцессорная система VAX DEC , VAX-11/782, была асимметричной. [16] но более поздние многопроцессорные системы VAX стали SMP. [17]

Ранние коммерческие реализации Unix SMP включали Sequent Computer Systems Balance 8000 (выпущенный в 1984 году) и Balance 21000 (выпущенный в 1986 году). [18] Обе модели были основаны на процессорах National Semiconductor NS32032 с тактовой частотой 10 МГц , каждый из которых имел небольшой кэш со сквозной записью, подключенный к общей памяти для формирования общей системы памяти . Еще одной ранней коммерческой реализацией Unix SMP была система Honeywell Information Systems Italy XPS-100 на базе NUMA, разработанная Дэном Гиланом из VAST Corporation в 1985 году. Ее конструкция поддерживала до 14 процессоров, но из-за электрических ограничений самой крупной продаваемой версией была двухпроцессорная система. . Операционная система была получена и портирована корпорацией VAST на основе кода AT&T 3B20 Unix SysVr3, используемого внутри AT&T.

Ранее существовали некоммерческие многопроцессорные порты UNIX, в том числе порт под названием MUNIX, созданный в Военно-морской аспирантуре к 1975 году. [19]

Использует [ править ]

Системы с разделением времени и серверные системы часто могут использовать SMP без внесения изменений в приложения, поскольку в них может работать несколько процессов параллельно, а система, в которой запущено более одного процесса, может запускать разные процессы на разных процессорах.

На персональных компьютерах SMP менее полезен для приложений, которые не были модифицированы. Если система редко запускает более одного процесса одновременно, SMP полезен только для приложений, модифицированных для многопоточной (многозадачной) обработки. Специально запрограммированное программное обеспечение может быть написано или модифицировано для использования нескольких потоков, чтобы оно могло использовать несколько процессоров.

Многопоточные программы также можно использовать в системах с разделением времени и серверных системах, поддерживающих многопоточность, что позволяет им более эффективно использовать несколько процессоров.

Преимущества/недостатки [ править ]

В современных системах SMP все процессоры тесно связаны внутри одного блока с помощью шины или коммутатора; в более ранних системах SMP один процессор занимал весь шкаф. Некоторые из общих компонентов — это глобальная память, диски и устройства ввода-вывода. На всех процессорах работает только одна копия ОС, и ОС должна быть спроектирована так, чтобы использовать преимущества этой архитектуры. Некоторые из основных преимуществ включают экономичные способы увеличения пропускной способности. Для решения различных проблем и задач SMP применяет несколько процессоров для решения одной задачи, известной как параллельное программирование .

Однако существует несколько ограничений масштабируемости SMP из-за согласованности кэша и общих объектов.

Программирование [ править ]

Однопроцессорные и SMP-системы требуют разных методов программирования для достижения максимальной производительности. Программы, работающие в системах SMP, могут испытывать повышение производительности, даже если они были написаны для однопроцессорных систем. Это связано с тем, что аппаратные прерывания обычно приостанавливают выполнение программы, в то время как ядро , которое их обрабатывает, вместо этого может выполняться на простаивающем процессоре. Эффект в большинстве приложений (например, игр) заключается не столько в увеличении производительности, сколько в том, что программа работает гораздо более плавно. Некоторые приложения, особенно создание программного обеспечения и некоторые проекты распределенных вычислений , работают быстрее в раз (почти) количества дополнительных процессоров. (Компиляторы сами по себе являются однопоточными, но при создании программного проекта с несколькими модулями компиляции, если каждая единица компиляции обрабатывается независимо, это создает до неловкости параллельную ситуацию во всем проекте с несколькими модулями компиляции, позволяя почти линейно масштабировать компиляцию. Проекты распределенных вычислений по своей сути параллельны.)

Системные программисты должны встроить поддержку SMP в операционную систему , иначе дополнительные процессоры останутся бездействующими и система будет функционировать как однопроцессорная.

Системы SMP также могут привести к увеличению сложности наборов команд. Однородная процессорная система обычно требует дополнительных регистров для «специальных инструкций», таких как SIMD (MMX, SSE и т. д.), тогда как гетерогенная система может реализовывать разные типы аппаратного обеспечения для разных инструкций/использований.

Производительность [ править ]

Когда одновременно выполняется более одной программы, производительность SMP-системы значительно выше, чем однопроцессорной, поскольку разные программы могут одновременно выполняться на разных процессорах. И наоборот, асимметричная многопроцессорная обработка (AMP) обычно позволяет только одному процессору одновременно запускать программу или задачу. Например, AMP можно использовать для назначения ЦП определенных задач в зависимости от приоритета и важности выполнения задач. AMP был создан задолго до SMP с точки зрения работы с несколькими процессорами, что объясняет недостаточную производительность в приведенном примере.

В тех случаях, когда среда SMP обрабатывает множество заданий, администраторы часто сталкиваются с потерей эффективности оборудования. Программное обеспечение было разработано для планирования заданий и других функций компьютера, чтобы загрузка процессора достигла максимального потенциала. Хорошие пакеты программного обеспечения могут достичь этого максимального потенциала за счет планирования каждого процессора отдельно, а также за счет интеграции нескольких компьютеров и кластеров SMP.

Доступ к оперативной памяти сериализован; из-за этого и проблем с когерентностью кэша производительность немного отстает от количества дополнительных процессоров в системе.

Альтернативы [ править ]

SMP использует единую общую системную шину , которая представляет собой один из самых ранних стилей архитектуры многопроцессорных машин, обычно используемый для создания небольших компьютеров с числом процессоров до 8.

Более крупные компьютерные системы могут использовать новые архитектуры, такие как NUMA (неоднородный доступ к памяти), которая выделяет разные банки памяти для разных процессоров. В архитектуре NUMA процессоры могут получать доступ к локальной памяти быстрее, а к удаленной памяти медленнее. Это может значительно повысить пропускную способность памяти, если данные локализованы для конкретных процессов (и, следовательно, процессоров). С другой стороны, NUMA увеличивает стоимость перемещения данных с одного процессора на другой, как и при балансировке рабочей нагрузки. Преимущества NUMA ограничены определенными рабочими нагрузками, особенно на серверах , где данные часто тесно связаны с определенными задачами или пользователями.

Наконец, существует компьютерная кластерная многопроцессорная обработка (например, Beowulf ), в которой не вся память доступна всем процессорам. Методы кластеризации довольно широко используются для создания очень больших суперкомпьютеров.

Переменная SMP [ править ]

Переменная симметричная многопроцессорность (vSMP) — это особая технология мобильного использования, разработанная NVIDIA. Эта технология включает в себя дополнительное пятое ядро в четырехъядерном устройстве, называемое ядром Companion, созданное специально для выполнения задач на более низкой частоте во время мобильного активного режима ожидания, воспроизведения видео и воспроизведения музыки.

Проект Кал-Эл ( Тегра 3 ), [20] запатентованная NVIDIA, была первой SoC (системой на кристалле), реализовавшей эту новую технологию vSMP. Эта технология не только снижает энергопотребление мобильных устройств в активном режиме ожидания, но также максимизирует производительность четырехъядерных процессоров во время активного использования для интенсивных мобильных приложений. В целом эта технология удовлетворяет потребность в увеличении срока службы батареи во время активного использования и в режиме ожидания за счет снижения энергопотребления мобильных процессоров.

В отличие от нынешних архитектур SMP, ядро vSMP Companion прозрачно для ОС. Это означает, что операционная система и запущенные приложения совершенно не знают об этом дополнительном ядре, но все же могут использовать его преимущества. Некоторые из преимуществ архитектуры vSMP включают согласованность кэша, эффективность ОС и оптимизацию энергопотребления. Преимущества этой архитектуры описаны ниже:

- Согласованность кэша. Синхронизация кэшей между ядрами, работающими на разных частотах, не имеет последствий, поскольку vSMP не позволяет сопутствующему ядру и основным ядрам работать одновременно.

- Эффективность ОС: неэффективно, когда несколько ядер ЦП работают на разных асинхронных частотах, поскольку это может привести к возможным проблемам с планированием. [ как? ] При использовании vSMP активные ядра ЦП будут работать на одинаковых частотах для оптимизации планирования ОС.

- Оптимизация энергопотребления. В архитектуре на основе асинхронной тактовой частоты каждое ядро находится в отдельной плоскости питания, что позволяет регулировать напряжение для разных рабочих частот. Результат этого может повлиять на производительность. [ как? ] Технология vSMP способна динамически включать и отключать определенные ядра для активного и резервного использования, снижая общее энергопотребление.

Эти преимущества позволяют архитектуре vSMP значительно выиграть. [ павлинья проза ] по сравнению с другими архитектурами, использующими технологии асинхронной синхронизации.

См. также [ править ]

- Асимметричная многопроцессорная обработка

- Двоичная модульная машина потока данных

- Сотовая многопроцессорная обработка

- Локаль (компьютерное оборудование)

- Массивная параллель

- Разделенное глобальное адресное пространство

- Одновременная многопоточность – когда функциональные элементы ядра ЦП распределяются по нескольким потокам выполнения.

- Программная блокировка

- Ксеон Пхи

Ссылки [ править ]

- ^ Паттерсон, Дэвид ; Хеннесси, Джон (2018). Компьютерная организация и дизайн: аппаратно-программный интерфейс (изд. RISC-V). Кембридж, США: Морган Кауфманн. п. 509. ИСБН 978-0-12-812275-4 .

- ^ Джон Кубятович. Введение в параллельные архитектуры и Pthreads . 2013 Краткий курс по параллельному программированию.

- ^ Дэвид Каллер ; Джасвиндер Пал Сингх; Ануп Гупта (1999). Параллельная компьютерная архитектура: аппаратно-программный подход . Морган Кауфманн . п. 47. ИСБН 978-1-55860-343-1 .

- ^ Лина Дж. Карам; Исмаил Аль-Камаль; Алан Гатерер; Джин А. Франц; Дэвид В. Андерсон; Брайан Л. Эванс (2009). «Тенденции в развитии многоядерных платформ DSP» (PDF) . Журнал обработки сигналов IEEE . 26 (6): 38–49. Бибкод : 2009ISPM...26...38K . дои : 10.1109/MSP.2009.934113 . S2CID 9429714 .

- ^ Грегори В. Уилсон (октябрь 1994 г.). «История развития параллельных вычислений» .

- ^ Мартин Х. Вейк (январь 1964 г.). «Четвертый обзор отечественных электронных цифровых вычислительных систем» . Лаборатории баллистических исследований , Абердинский полигон . Берроуз D825.

- ^ Функциональные характеристики IBM System/360 Model 65 (PDF) . Четвертое издание. ИБМ. Сентябрь 1968 г. А22-6884-3.

- ^ Функциональные характеристики IBM System/360 Model 67 (PDF) . Третье издание. ИБМ. Февраль 1972 г. GA27-2719-2.

- ^ M65MP: Эксперимент в многопроцессорной обработке OS / 360

- ^ Руководство по программной логике, Логика супервизора ввода-вывода ОС, выпуск 21 (R21.7) (PDF) (Десятое изд.). ИБМ. Апрель 1973 г. GY28-6616-9.

- ^ Программы управления разделением времени Майка Александра (май 1971 г.) содержат информацию о MTS, TSS, CP / 67 и Multics.

- ^ Системное руководство GE-635 (PDF) . Дженерал Электрик . Июль 1964 года.

- ^ Системное руководство GE-645 (PDF) . Дженерал Электрик. Январь 1968 года.

- ^ Ричард Шетрон (5 мая 1998 г.). «Страх перед многопроцессорностью?» . Группа новостей : alt.folklore.computers . Usenet: [электронная почта защищена] .

- ^ ДЕКАБРЬ 1077 г. и СМП

- ^ Руководство по продажам продукции VAX, страницы 1-23 и 1-24 : VAX-11/782 описан как асимметричная многопроцессорная система в 1982 году.

- ^ Руководство пользователя системного оборудования VAX 8820/8830/8840 : к 1988 году операционная система VAX была SMP.

- ^ Хокни, RW; Джессоуп, ЧР (1988). Параллельные компьютеры 2: Архитектура, программирование и алгоритмы . Тейлор и Фрэнсис. п. 46. ИСБН 0-85274-811-6 .

- ^ Хоули, Джон Альфред (июнь 1975 г.). «MUNIX, многопроцессорная версия UNIX» (PDF) . core.ac.uk. Проверено 11 ноября 2018 г.

- ^ Variable SMP — архитектура многоядерного процессора с низким энергопотреблением и высокой производительностью. NVIDIA. 2011.