Моделирование полупроводниковых устройств

Моделирование полупроводниковых устройств создает модели поведения электрических устройств на основе фундаментальной физики, такие как профили легирования устройств. Это может также включать создание компактных моделей (таких как хорошо известные модели транзисторов SPICE ), которые пытаются отразить электрическое поведение таких устройств, но обычно не выводят его из базовой физики. Обычно все начинается с результатов моделирования полупроводникового процесса .

Введение

[ редактировать ]

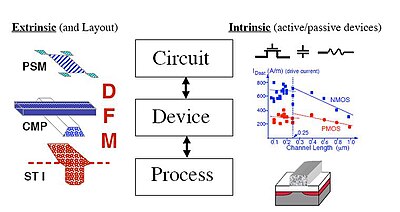

Рисунок справа представляет собой упрощенное концептуальное представление «общей картины». На этом рисунке показаны два каскада инвертора и результирующая диаграмма зависимости входного-выходного напряжения от времени. С точки зрения цифровых систем ключевыми параметрами, представляющими интерес, являются: временные задержки, мощность переключения, ток утечки и перекрестные связи ( перекрестные помехи ) с другими блоками. Уровни напряжения и скорость перехода также вызывают беспокойство.

На рисунке также схематически показано значение I on по сравнению с I off , что, в свою очередь, связано с током возбуждения (и подвижностью) для «включенного» устройства и несколькими путями утечки для «выключенных» устройств. На рисунке явно не показаны емкости (как собственные, так и паразитные), влияющие на динамические характеристики.

Масштабирование мощности, которое сейчас является основной движущей силой в отрасли, отражено в упрощенном уравнении, показанном на рисунке: критическими параметрами являются емкость, источник питания и тактовая частота. Ключевые параметры, которые связывают поведение устройства с производительностью системы, включают пороговое напряжение , ток возбуждения и подпороговые характеристики.

Именно сочетание проблем производительности системы с лежащими в основе технологиями и переменными конструкции устройства приводит к постоянным законам масштабирования, которые мы теперь кодифицируем как закон Мура .

Моделирование устройств

[ редактировать ]В физике и моделировании устройств в интегральных схемах преобладают моделирование МОП и биполярных транзисторов. Однако важны и другие устройства, например устройства памяти, к моделированию которых предъявляются совсем другие требования. Конечно, существуют также вопросы обеспечения надежности — например, схемы и устройства защиты от электростатического разряда (ESD), — где подложка и паразитные устройства имеют решающее значение. Эти эффекты и моделирование не учитываются большинством программ моделирования устройств; Заинтересованному читателю мы отсылаем к нескольким превосходным монографиям в области ESD и моделирования ввода-вывода. [1] [2] [3]

Физические модели против компактных моделей

[ редактировать ]

Моделирование устройств, основанное на физике, должно быть точным, но оно недостаточно быстрое для инструментов более высокого уровня, включая симуляторы схем , такие как SPICE . Поэтому в симуляторах схем обычно используются более эмпирические модели (часто называемые компактными моделями), которые напрямую не моделируют основную физику. Например, моделирование мобильности на инверсионном уровне , или моделирование мобильности и ее зависимости от физических параметров, условий окружающей среды и эксплуатации, является важной темой как для физических моделей TCAD (технология компьютерного проектирования), так и для компактных моделей схемного уровня. Однако оно неточно смоделировано на основе первых принципов, поэтому приходится прибегать к подгонке экспериментальных данных. Для моделирования подвижности на физическом уровне электрическими переменными являются различные механизмы рассеяния, плотности носителей, а также локальные потенциалы и поля, включая их зависимости от технологии и окружающей среды.

Напротив, на уровне схемы модели параметризуют эффекты с точки зрения напряжения на клеммах и эмпирических параметров рассеяния. Эти два представления можно сравнить, но во многих случаях неясно, как интерпретировать экспериментальные данные с точки зрения более микроскопического поведения.

История

[ редактировать ]Эволюция технологии автоматизированного проектирования (TCAD) — синергетического сочетания инструментов моделирования процессов, устройств и схем — берет свое начало в биполярной технологии, начиная с конца 1960-х годов, и в проблемах изолированных, двойных и двойных переходов. с тройной Транзисторы диффузией . Эти устройства и технологии легли в основу первых интегральных схем; тем не менее, многие проблемы масштабирования и лежащие в их основе физические эффекты являются неотъемлемой частью проектирования ИС , даже после четырех десятилетий разработки ИС. В этих первых поколениях ИС вариативность процесса и параметрический выход были проблемой — тема, которая снова станет контролирующим фактором в будущих технологиях ИС.

Проблемы управления процессами — как для внутренних устройств, так и для всех связанных с ними паразитных элементов — представляли собой огромные проблемы и требовали разработки ряда передовых физических моделей для моделирования процессов и устройств. Начиная с конца 1960-х и до 1970-х годов в качестве подходов к моделированию использовались преимущественно одномерные и двумерные симуляторы. В то время как TCAD в этих первых поколениях показал многообещающие перспективы в решении физических проблем биполярной технологии, превосходная масштабируемость и энергопотребление технологии МОП произвели революцию в индустрии интегральных схем. К середине 1980-х годов КМОП стала доминирующей движущей силой интегрированной электроники. Тем не менее, эти ранние разработки TCAD [4] [5] заложили основу для их роста и широкого внедрения в качестве важнейшего набора инструментов, который способствовал развитию технологий в эпоху СБИС и ULSI, которые сейчас стали основным направлением.

В разработке ИС на протяжении более четверти века доминировала технология МОП. В 1970-х и 1980-х годах предпочтение отдавалось NMOS из-за преимуществ в скорости и площади, а также из-за технологических ограничений и проблем, связанных с изоляцией, паразитными эффектами и сложностью процесса. В эпоху доминирования NMOS в LSI и появления VLSI фундаментальные законы масштабирования MOS-технологии были систематизированы и широко применялись. [6] Именно в этот период TCAD достигла зрелости в плане реализации надежного моделирования процессов (в основном одномерного), которое затем стало неотъемлемым инструментом технологического проектирования, повсеместно используемым в отрасли. [7] В то же время моделирование устройств, преимущественно двумерное из-за природы МОП-устройств, стало рабочей лошадкой технологов при проектировании и масштабировании устройств. [8] [9] Переход от технологии NMOS к технологии CMOS привел к необходимости тесно связанных и полностью двумерных симуляторов для моделирования процессов и устройств. Это третье поколение инструментов TCAD стало решающим для решения всей сложности технологии двухъячеечного КМОП (см. Рисунок 3а), включая проблемы правил проектирования и паразитных эффектов, таких как защелка . [10] [11] Дается сокращенный обзор этого периода до середины 1980-х годов; [12] а с точки зрения того, как в процессе проектирования использовались инструменты TCAD, см. [13]

См. также

[ редактировать ]Ссылки

[ редактировать ]- ^ К. Дуввури и А. Амерасекера, ESD: повсеместная проблема надежности IC-технологий , Proc. IEEE, том. 81, стр. 690–702, 1993.

- ^ А. Амерасекера и К. Дуввури, ESD в кремниевых интегральных схемах, второе издание, Нью-Йорк, John Wiley & Sons, 2002. ISBN 0-471-49871-8

- ^ С. Дабрал и Ти Джей Мэлони, Базовое проектирование электростатического разряда и ввода-вывода, Нью-Йорк, John Wiley & Sons, 1998. ISBN 0-471-25359-6

- ^ Х. Дж. Деман и Р. Мертенс, SITCAP - симулятор биполярных транзисторов для программ компьютерного анализа цепей. [ мертвая ссылка ] , Международная конференция по твердотельным схемам (ISSCC), Технический дайджест, стр. 104–5, февраль 1973 г.

- ^ Р.В. Даттон и Д.А. Антониадис, Моделирование процессов для проектирования и управления устройствами [ мертвая ссылка ] , Международная конференция по твердотельным схемам (ISSCC), Технический дайджест, стр. 244–245, февраль 1979 г.

- ^ Р. Х. Деннард, Ф. Х. Генсслен, Х. Н. Ю, В. Л. Родеут, Э. Бассус и А. Р. Леблан, Проектирование ионно-имплантированных МОП-транзисторов с очень малыми физическими размерами , IEEE Jour. Твердотельные схемы, вып. SC-9, стр. 256-268, октябрь 1974 г.

- ^ Р.В. Даттон и С.Э. Хансен, Моделирование процесса технологии устройств на интегральных схемах , Труды IEEE, том. 69, нет. 10, стр. 1305–1320, октябрь 1981 г.

- ^ PE Cottrell и EM Buturla, «Двумерное статическое и переходное моделирование переноса мобильных носителей в полупроводнике», Proceedings NASECODE I (Численный анализ полупроводниковых устройств), стр. 31-64, Boole Press, 1979.

- ^ С. Зельберхерр , В. Фихтнер и Х. В. Поцль, «Minimos - пакет программ для облегчения проектирования и анализа МОП-устройств», Proceedings NASECODE I (Численный анализ полупроводниковых устройств), стр. 275-79, Boole Press, 1979.

- ^ К.С. Рафферти, М.Р. Пинто и Р.В. Даттон, Итеративные методы моделирования полупроводниковых устройств , IEEE Trans. Электр. Дев., вып. ЭД-32, №10, стр.2018-2027, октябрь 1985 г.

- ^ М. Р. Пинто и Р. У. Даттон, Точный анализ условий триггера для защелки CMOS , Письма об электронных устройствах IEEE , том. ЭДЛ-6, нет. 2 февраля 1985 г.

- ^ Р.В. Даттон, Моделирование и симуляция для СБИС , Международное собрание электронных устройств (IEDM), Технический дайджест, стр. 2–7, декабрь 1986 г.

- ^ К.М. Чам, С.-Ю. О, Д. Чин и Дж. Л. Молл, Компьютерное проектирование и разработка устройств СБИС, Kluwer Academic Publishers (KAP), 1986. ISBN 0-89838-204-1

- Справочник по автоматизации проектирования электронных систем для интегральных схем , автор: Лаваньо, Мартин и Шеффер, ISBN 0-8493-3096-3 Обзор области автоматизации электронного проектирования . Это краткое изложение было взято (с разрешения) из тома II, главы 25 « Моделирование устройств — от физики к извлечению электрических параметров» , авторами Робертом В. Даттоном, Чанг-Хуном Чой и Эдвином К. Каном.

- Р. В. Даттон и А. Дж. Стройвас, Перспективы технологий и САПР, основанных на технологиях , IEEE Trans. CAD-ICAS, вып. 19, нет. 12, стр. 1544–1560, декабрь 2000 г.