Пиксельное визуальное ядро

Pixel Visual Core ( PVC ) — это серия на базе ARM «система в корпусе» (SiP) процессоров обработки изображений , разработанная Google . [1] PVC — это полностью программируемая ) для изображений , видения и искусственного интеллекта многоядерная предметно-ориентированная архитектура ( DSA для мобильных устройств и, в будущем, для Интернета вещей . [2] Впервые он появился в Google Pixel 2 и 2 XL , представленных 19 октября 2017 года. Он также появился в Google Pixel 3 и 3 XL . Начиная с Pixel 4, этот чип был заменен на Pixel Neural Core .

История [ править ]

Ранее Google использовала Qualcomm Snapdragon для процессоры , графические процессоры , IPU и DSP обработки изображений на своих устройствах Google Nexus и Google Pixel . С ростом важности методов вычислительной фотографии Google разработал Pixel Visual Core (PVC). Google утверждает, что PVC потребляет меньше энергии, чем использование процессора и графического процессора, но при этом остается полностью программируемым, в отличие от их (ASIC) тензорного процессора (TPU специализированной интегральной схемы ).Действительно, классические мобильные устройства оснащены процессором сигналов изображения с фиксированной функциональностью (ISP), который представляет собой конвейер обработки изображений . В отличие от этого, PVC имеет гибкую программируемую функциональность, не ограничивающуюся только обработкой изображений.

PVC в Google Pixel 2 и 2 XL имеет маркировку SR3HX X726C502. [3]

PVC в Google Pixel 3 и 3 XL имеет маркировку SR3HX X739F030. [4]

Благодаря PVC Pixel 2 и Pixel 3 получили мобильный рейтинг DxOMark 98. [5] и 101. [6] Последний результат стал лучшим в рейтинге DxOMark для мобильных устройств с одним объективом, сравнявшись с iPhone XR. [7]

Программное обеспечение Pixel Visual Core [ править ]

Типичная программа обработки изображений PVC написана на языке Halide . В настоящее время он поддерживает только подмножество языка программирования Halide без операций с плавающей запятой и с ограниченными шаблонами доступа к памяти. [8] Halide — это предметно-ориентированный язык , который позволяет пользователю отделить алгоритм от планирования его выполнения.Таким образом, разработчик может написать программу, оптимизированную для целевой аппаратной архитектуры. [2]

Pixel Visual Core ISA [ править ]

PVC имеет два типа архитектуры набора команд (ISA) : виртуальный и физический. Сначала программа на языке высокого уровня компилируется в виртуальную ISA (vISA) , вдохновленную RISC-V ISA. [2] который полностью абстрагируется от поколения целевого оборудования. Затем программа vISA компилируется в так называемую физическую ISA (pISA) , то есть VLIW ISA. На этом этапе компиляции учитываются параметры целевого оборудования (например, размер массива PE, размер STP и т. д.) и явно указываются перемещения памяти. Разделение vISA и pISA позволяет первому быть кросс-архитектурным и независимым от поколения, тогда как pISA можно компилировать в автономном режиме или посредством JIT-компиляции . [8]

Pixel Visual Архитектура Core

Pixel Visual Core представляет собой масштабируемую многоядерную энергоэффективную архитектуру с четными числами от 2 до 16 ядер. [2] Ядром PVC является блок обработки изображений (IPU), программируемый блок, предназначенный для обработки изображений. Архитектура Pixel Visual Core также была разработана либо как отдельный чип, как SR3HX, либо как IP-блок для системы на кристалле (SOC) . [2]

Блок обработки изображений (IPU) [ править ]

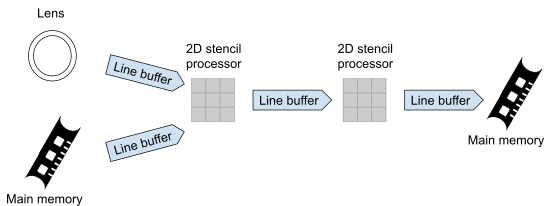

Ядро IPU имеет трафаретный процессор (STP), пул строковых буферов (LBP) и NoC .STP в основном предоставляет двумерный SIMD- массив обрабатывающих элементов (PE), способный выполнять трафаретные вычисления , небольшую окрестность пикселей. Хотя это похоже на вычисления систолического массива и волнового фронта, STP имеет явное программное управление перемещением данных. Каждый PE имеет 2 16-битных арифметико-логических блока (ALU) , 1 16-битный умножитель-аккумулятор (MAC) , 10 16-битных регистров и 10 1-битных регистров предикатов. [2]

Пул буферов строк (LBP) [ править ]

Учитывая, что одной из наиболее энергозатратных операций является доступ к DRAM, каждый STP имеет временные буферы для повышения локальности данных , а именно LBP. Используемый LBP представляет собой двумерный FIFO , который поддерживает операции чтения и записи разных размеров. LBP использует поведенческую модель одного производителя и нескольких потребителей. Каждый LBP может иметь восемь логических блоков памяти LB и один для операций ввода-вывода DMA . [8] Из-за действительно высокой сложности системы памяти разработчики PVC называют контроллер LBP одним из самых сложных компонентов. [2] Используемый NoC представляет собой кольцевую сеть на кристалле, используемую для связи только с соседними ядрами для экономии энергии и сохранения конвейерной вычислительной схемы. [2]

Трафаретный процессор (STP) [ править ]

STP имеет двумерный массив PE: например, массив полных PE 16x16 и четыре полосы упрощенных PE, называемых «гало» .STP имеет скалярный процессор, называемый скалярной полосой (SCL), который добавляет управляющие инструкции в небольшую память для команд.Последний компонент STP — это блок хранения загрузки, называемый генератором листов (SHG), где лист — это блок доступа к памяти PVC. [2]

Краткое описание конструкции SR3HX [ править ]

SR3HX PVC оснащен 64-битным процессором ARMv8a ARM Cortex-A53 , 8 ядрами блока обработки изображений (IPU), 512 МБ LPDDR4 , MIPI, PCIe.Каждое ядро IPU имеет 512 арифметико-логических блоков (ALU), состоящих из 256 процессорных элементов (PE), расположенных в виде двумерного массива 16 x 16. Эти ядра выполняют специальную VLIW ISA.На каждый процессорный элемент приходится два 16-битных АЛУ, и они могут работать тремя различными способами: независимым, объединенным и объединенным. [9] ПВХ SR3HX производится в виде SiP компанией TSMC с использованием процесса 28HPM HKMG . [1] Он разрабатывался более 4 лет в сотрудничестве с Intel . (Кодовое имя: Монетт Хилл) [10] Google утверждает, что SR3HX PVC в 7-16 раз более энергоэффективен, чем Snapdragon 835 . [1] И что SR3HX PVC может выполнять 3 триллиона операций в секунду, HDR+ может работать в 5 раз быстрее и потреблять менее одной десятой энергии, чем Snapdragon 835 . [11] Он поддерживает Halide для обработки изображений и TensorFlow для машинного обучения. [11] Текущий чип работает на частоте 426 МГц, а один IPU способен выполнять более 1 TeraOPS. [2] [8]

Ссылки [ править ]

- ↑ Перейти обратно: Перейти обратно: а б с Катресс, Ян. «Горячие фишки 2018: живой блог Google Pixel Visual Core (10:00 по тихоокеанскому времени, 17:00 по всемирному координированному времени)» . www.anandtech.com . Проверено 2 февраля 2019 г.

- ↑ Перейти обратно: Перейти обратно: а б с д и ж г час я дж Хеннесси, Джон; Паттерсон, Дэвид (2017). Компьютерная архитектура: количественный подход (шестое изд.). Морган Кауфманн. стр. 579–606. ISBN 978-0-12-811905-1 .

- ^ «Разборка Google Pixel 2 XL» . iFixit . 19 октября 2017 г. Проверено 2 февраля 2019 г.

- ^ «Разборка Google Pixel 3 XL» . iFixit . 16.10.2018 . Проверено 2 февраля 2019 г.

- ^ «Пиксель 2 DxOMark» .

- ^ «Пиксель 3 DxOMark» .

- ^ «iPhone XR DxOMark» .

- ↑ Перейти обратно: Перейти обратно: а б с д «Pixel Visual Core: полностью программируемый процессор изображения, зрения и искусственного интеллекта Google для мобильных устройств. HotChips2018» (PDF) .

- ^ «Пиксельное визуальное ядро (PVC) — Google — WikiChip» . ru.wikichip.org . Проверено 2 февраля 2019 г.

- ^ «Google заключила партнерское соглашение с Intel для создания чипа Pixel Visual Core в Pixel 2» . xda-разработчики . 25 октября 2017 г. Проверено 2 февраля 2019 г.

- ↑ Перейти обратно: Перейти обратно: а б «Pixel Visual Core: обработка изображений и машинное обучение на Pixel 2» . Google . 17.10.2017 . Проверено 2 февраля 2019 г.