4000 рэндов

R4000 микропроцессор — это , разработанный MIPS Computer Systems , который реализует MIPS III архитектуру набора команд (ISA). Официально анонсированный 1 октября 1991 года, это был один из первых 64-битных микропроцессоров и первая реализация MIPS III. В начале 1990-х годов, когда ожидалось, что микропроцессоры RISC заменят микропроцессоры CISC, такие как Intel i486 , R4000 был выбран в качестве микропроцессора Advanced Computing Environment (ACE), отраслевого стандарта, призванного определить общую платформу RISC. В конечном итоге ACE потерпела неудачу по ряду причин , но R4000 добился успеха на рынках рабочих станций и серверов.

Модели

[ редактировать ]Существует три конфигурации R4000: R4000PC — модель начального уровня без поддержки вторичного кэша; R4000SC, модель со вторичной кэш-памятью, но без возможности многопроцессорности; и R4000MC, модель с вторичным кэшем и поддержкой протоколов когерентности кэша, необходимых многопроцессорным системам.

Описание

[ редактировать ]R4000 — это скалярный суперконвейерный микропроцессор с восьмиступенчатым целочисленным конвейером. На первом этапе (IF) генерируется виртуальный адрес для инструкции, и резервный буфер трансляции инструкций (TLB) начинает преобразование адреса в физический адрес. На втором этапе (IS) трансляция завершается, и инструкция извлекается из внутреннего кэша инструкций объемом 8 КБ. Кэш инструкций напрямую отображается и виртуально индексируется, физически помечается тегами . Он имеет размер строки 16 или 32 байта. Архитектурно его можно было расширить до 32 КБ.

На третьем этапе (RF) инструкция декодируется и файл регистров считывается . MIPS III определяет два файла регистров: один для целочисленных единиц, а другой для чисел с плавающей запятой. Каждый файл регистров имеет ширину 64 бита и содержит 32 записи. Файл целочисленных регистров имеет два порта чтения и один порт записи, а файл регистров с плавающей запятой имеет два порта чтения и два порта записи. Выполнение начинается на четвертом этапе (EX) как для целочисленных инструкций, так и для инструкций с плавающей запятой; и записывается обратно в файлы регистров после завершения восьмого этапа (WB). Результаты могут быть пропущены, если это возможно.

Целочисленное исполнение

[ редактировать ]R4000 имеет арифметико-логическое устройство (АЛУ), устройство сдвига, умножитель, делитель и выравниватель нагрузки для выполнения целочисленных инструкций. АЛУ состоит из 64-битного сумматора с выбором переноса и логического блока и является конвейерным. Шифтер — это 32-битный бочкообразный шифтер . Он выполняет 64-битные сдвиги за два цикла, в результате чего конвейер останавливается. Такая конструкция была выбрана для экономии площади матрицы. Умножитель и делитель не являются конвейерными и имеют значительные задержки: умножения имеют задержку 10 или 20 циклов для 32-битных или 64-битных целых чисел соответственно; тогда как деления имеют задержку 69 или 133 цикла для 32-битных или 64-битных целых чисел соответственно. Большинство инструкций имеют задержку в один цикл. Сумматор ALU также используется для расчета виртуальных адресов для нагрузок, магазинов и филиалов.

Инструкции загрузки и сохранения выполняются целочисленным конвейером и получают доступ к встроенному кэшу данных объемом 8 КБ.

Выполнение с плавающей запятой

[ редактировать ]R4000 имеет встроенный стандарту IEEE 754-1985 (FPU), соответствующий модуль вычислений с плавающей запятой , называемый R4010. FPU представляет собой сопроцессор, обозначенный CP1. [1] (MIPS ISA определил четыре сопроцессора, обозначенных от CP0 до CP3). FPU может работать в двух режимах: 32- или 64-битном, которые выбираются установкой бита FR в регистре состояния ЦП. В 32-битном режиме 32 регистра с плавающей запятой становятся шириной 32 бита, когда они используются для хранения чисел с плавающей запятой одинарной точности. При использовании для хранения чисел двойной точности имеется 16 регистров с плавающей запятой (регистры спарены).

FPU может работать параллельно с ALU, если только нет зависимости от данных или ресурсов, которая приводит к его остановке. Он содержит три подблока: сумматор, умножитель и делитель. Умножитель и делитель могут выполнять инструкцию параллельно с сумматором, но они используют сумматор на последних этапах выполнения, тем самым накладывая ограничения на перекрывающееся выполнение. Таким образом, при определенных условиях он может одновременно выполнять до трех инструкций, по одной в каждом блоке. FPU способен удалять одну инструкцию за такт.

Сумматор и умножитель являются конвейерными. Множитель имеет четырехступенчатый конвейер умножения. Он тактируется на удвоенной тактовой частоте микропроцессора для обеспечения адекватной производительности и использует динамическую логику для достижения высокой тактовой частоты. Деление имеет задержку 23 или 36 тактов для операций с одинарной или двойной точностью, а квадратный корень имеет задержку 54 или 112 тактов. Для деления и извлечения квадратного корня используется алгоритм SRT .

Управление памятью

[ редактировать ]Блок управления памятью на 48 записей (MMU) использует резервный буфер трансляции для трансляции виртуальных адресов . R4000 использует 64-битный виртуальный адрес, но реализует только 40 из 64 бит, что позволяет использовать 1 ТБ виртуальной памяти ; остальные биты проверяются, чтобы убедиться, что они содержат ноль. R4000 использует 36-битный физический адрес , что позволяет адресовать 64 ГБ физической памяти .

Вторичный кэш

[ редактировать ]R4000 (только конфигурации SC и MC) поддерживает внешний вторичный кэш емкостью от 128 КБ до 4 МБ. Доступ к кэшу осуществляется через выделенную 128-битную шину данных. Вторичный кэш можно настроить либо как единый кэш, либо как разделенный кэш инструкций и данных. В последней конфигурации каждый кэш может иметь емкость от 128 КБ до 2 МБ. [2] Вторичный кэш физически индексируется, физически помечен и имеет программируемый размер строки 128, 256, 512 или 1024 байта. Контроллер кэша встроен в кристалл. Кэш построен из стандартной статической оперативной памяти (SRAM). Шины данных и тегов защищены ECC.

Системная шина

[ редактировать ]R4000 использует 64-битную системную шину, называемую шиной SysAD. Шина SysAD представляла собой мультиплексированную шину адресов и данных, то есть для передачи данных и адресов использовалась один и тот же набор проводов. Хотя это снижает пропускную способность, это также дешевле, чем предоставление отдельной адресной шины, которая требует большего количества контактов и увеличивает сложность системы. Шину SysAD можно настроить на работу на половине, трети или четверти внутренней тактовой частоты. Шина SysAD генерирует тактовый сигнал путем деления рабочей частоты.

Количество транзисторов, размеры кристалла и детали процесса

[ редактировать ]R4000 содержит 1,2 миллиона транзисторов. [3] Он был разработан для двухслойного процесса комплементарного металла-оксида-полупроводника (КМОП) толщиной 1,0 мкм. Поскольку MIPS была компанией без производственных мощностей , R4000 был изготовлен партнерами по их собственным процессам, минимальный размер элемента которых составлял 0,8 мкм. [4]

Тактирование

[ редактировать ]R4000 генерирует различные тактовые сигналы из главного тактового сигнала, генерируемого извне. Что касается рабочей частоты, R4000 умножает главный тактовый сигнал на два с помощью встроенной системы фазовой автоподстройки частоты (ФАПЧ).

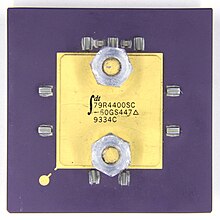

Упаковка

[ редактировать ]R4000PC выполнен в виде 179-контактной керамической матрицы контактов (CPGA). R4000SC и R4000MC упакованы в 447-контактную керамическую решетку с шахматным расположением контактов (SPGA). Вывод R4000MC отличается от R4000SC: некоторые контакты, которые не используются в R4000SC, используются для сигналов для реализации когерентности кэша на R4000MC. Распиновка R4000PC аналогична распиновке микропроцессоров R4200 и R4600 в корпусе PGA . Эта характеристика позволяет правильно спроектированной системе использовать любой из трех микропроцессоров.

4400 рэндов

[ редактировать ]

R4400 . является дальнейшим развитием R4000 Об этом было объявлено в начале ноября 1992 года. До этого образцы микропроцессора были отправлены избранным клиентам, а общедоступная версия появилась в январе 1993 года. R4400 работает на тактовых частотах 100, 133, 150, 200 и 250 МГц. Единственное существенное улучшение по сравнению с R4000 — это более крупные первичные кэши, емкость которых была увеличена вдвое до 16 КБ каждый с 8 КБ каждый. Он содержал 2,3 миллиона транзисторов.

R4400 был лицензирован компаниями Integrated Device Technology (IDT), LSI Logic , NEC , Performance Semiconductor, Siemens AG и Toshiba . IDT, NEC, Siemens и Toshiba изготовили и продали микропроцессор. LSI Logic использовала R4400 в нестандартных продуктах. Performance Semiconductor продала свое подразделение логики компании Cypress Semiconductor , где производство микропроцессоров MIPS было прекращено.

NEC продавала свою версию как VR4400. Первая версия, часть с частотой 150 МГц, была анонсирована в ноябре 1992 года. Ранние версии производились по технологии 0,6 мкм. [5] В середине 1995 года началась дискретизация участка 250 МГц. Он был изготовлен методом четырехслойного металла толщиной 0,35 мкм. [6] NEC также выпустила MR4401, керамический многочиповый модуль (MCM), который содержал VR4400SC с десятью микросхемами SRAM по 1 Мбит, реализовавшими вторичный кэш объемом 1 МБ. MCM был совместим по выводам с R4x00PC. Первая версия, часть 150 МГц, была анонсирована в 1994 году. В 1995 году была анонсирована часть 200 МГц.

Toshiba продавала свою версию как TC86R4400. Часть с частотой 200 МГц, содержащая 2,3 миллиона транзисторов и имеющая размер 134 мм. 2 Изготовленный по технологии 0,3 мкм, был представлен в середине 1994 года. Цена R4400PC составляла 1600 долларов США , R4400SC — 1950 долларов США , а R4400MC — 2150 долларов США в количестве 10 000 штук. [7]

Использование

[ редактировать ]R4400 используется:

- Компьютеры Carrera в своих с Windows NT персональных компьютерах и рабочих станциях [8]

- Concurrent Computer Corporation в своих многопроцессорных системах Maxion реального времени [9]

- Технология DeskStation на персональных компьютерах под управлением Windows NT и DeskStation Tyne. рабочей станции [10]

- Digital Equipment Corporation на своей DECstation 5000/260 рабочей станции и сервере

- Корпорация NEC на своих рабочих станциях RISCstation , серверах RISCserver и суперкомпьютере Cenju-3. [11]

- NeTPower на своих рабочих станциях и серверах под управлением Windows NT.

- Pyramid Technology использовала R4400MC в своих серверах серии Nile. [12]

- Siemens Nixdorf Informationssysteme (SNI) в своих UNIX - серверах серии RM и мэйнфрейме SR2000

- Silicon Graphics в своих рабочих станциях Onyx , Indigo , Indigo2 и Indy ; и на их Challenge сервере

- Тандемные компьютеры в своих NonStop Himalaya отказоустойчивых серверах

Чипсеты

[ редактировать ]Микропроцессоры R4000 и R4400 были подключены к системе с помощью специальных ASIC или коммерчески доступных наборов микросхем. Поставщики систем, такие как SGI, разработали собственные ASIC для своих систем. Коммерческие наборы микросхем разрабатывались, производились и продавались такими компаниями, как Toshiba с их набором микросхем Tiger Shark, который обеспечивал шину, совместимую с i486 . [13]

Примечания

[ редактировать ]- ^ Руководство пользователя микропроцессора MIPS R4000, второе издание , стр. 152

- ^ Генрих, «Руководство пользователя микропроцессора MIPS R4000», стр. 248

- ^ Мирапури, «Процессор Mips R4000» , стр. 10

- ^ Мирапури, «Процессор Mips R4000» , стр. 21

- ^ "NEC VR4400 RISC с удвоением тактовой частоты имеет 2 млн транзисторов"

- ^ «NEC готова к использованию 250-мегагерцовой версии 64-битного MIPS R4400 RISC»

- ^ «Toshiba имеет MIPS R4400 с частотой 200 МГц»

- ^ "...И с компьютеров Каррера"

- ^ «Параллельные мультипроцессоры имеют новую архитектуру шины»

- ^ «Персональные компьютеры Windows NT на базе MIPS R с настольной станции ...»

- ^ «NEC выходит на бизнес-рынок со своей последней линейкой рабочих станций RISC UNIX»

- ^ «Технология пирамид направлена на разрушение мэйнфрейма с помощью серии Nile»

- ^ «Toshiba Образцы набора микросхем 80486-Bus для серии R» .

Ссылки

[ редактировать ]- Генрих, Джо. Руководство пользователя микропроцессора MIPS R4000 , второе издание.

- Сунил Мирапури, Майкл Вудакр, Надер Вассеги, «Процессор Mips R4000», IEEE Micro , vol. 12. нет. 2, стр. 10–22, март/апрель 1992 г.