ДЕК V-11

V -11 под кодовым названием «Scorpio» представляет собой набор микросхем минипроцессора, реализующий VAX архитектуру набора команд и изготовленный (ISA), разработанный Digital Equipment Corporation (DEC).

История

[ редактировать ]V-11 был первым микропроцессором VAX компании Digital, но вторым после MicroVAX 78032 . Он был представлен на 39-й Международной конференции по твердотельным схемам, состоявшейся в 1984 году вместе с MicroVAX 78032, и был представлен в начале 1986 года в системах, работающих на частоте 5 МГц (время цикла 200 нс) и в 1987 году на частоте 6,25 МГц (время цикла 160 нс). V-11 был собственностью DEC и использовался только в их VAX 8200 , VAX 8250 , VAX 8300 и VAX 8350 миникомпьютерах ; и VAXstation 8000 рабочая станция .

На частоте 5 МГц V-11 работал примерно так же, как VAX-11/780 суперминикомпьютер . На частоте 6,25 МГц он работал примерно в 1,2 раза быстрее, чем VAX-11/780.

V-11 был частью программы Скорпион, целью которой было предоставить DEC возможность разрабатывать и производить сверхбольшой интеграции (ИС) интегральные схемы (СБИС). Другими аспектами программы были разработка нового пакета автоматизированного проектирования (САПР) и полупроводникового процесса, результатами которых являются CHAS и ZMOS соответственно. ZMOS был первым полупроводниковым процессом, полностью разработанным DEC.

Описание

[ редактировать ]V-11 представлял собой многочиповую конструкцию, состоящую в основном из микросхемы I/E, микросхемы M, микросхемы F и пяти микросхем ПЗУ/ОЗУ. В отличие от MicroVAX 78032, который реализовал подмножество VAX ISA, V-11 представлял собой полную реализацию VAX, поддерживающую все 304 инструкции и 17 типов данных (байт, слово, длинное слово, четверное слово, октаслово, F-плавающее, D-слово). плавающее, G-плавающее, H-плавающее, бит, битовое поле переменной длины, символьная строка, завершающая числовая строка, начальная отдельная числовая строка, упакованная десятичная строка, абсолютная очередь и самоотносительная очередь).

Чипы в наборе микросхем были соединены четырьмя шинами: MIB, DAL, PAL и CAL. MIB (шина микроинструкций) передавала сигналы управления микроинструкциями и адреса из хранилища управления на микросхемы I/E и F. MIB имеет ширину 40 бит, такую же, как микрослово, и защищен четностью . DAL — это 32-битная шина с защитой по четности, по которой данные и адреса передаются к и от микросхем I/E, M и F, кэша, ОЗУ резервного буфера трансляции и интерфейса порта.

Чип ПЗУ/ОЗУ

[ редактировать ]Чип ПЗУ/ОЗУ (DC327) реализовал одну пятую изменяемого хранилища управления . (ПЗУ) размером 16 384 на 8 бит (16 КБ) Он содержал постоянное запоминающее устройство 1024 на 8 бит (1 КБ) , ОЗУ с произвольным доступом размером 32 на 14 бит и память с адресной адресацией по содержимому (CAM) . ПЗУ содержало хранилище управления, а ОЗУ использовалось для хранения исправлений хранилища управления. ПЗУ/ОЗУ состояло из 208 000 транзисторов на кристалле размером 344 на 285 мил (8,74 на 7,24 мм) площадью 98 040 мил. 2 (63,25 мм 2 ). Он рассеял 1 Вт.

чип ввода-вывода

[ редактировать ]

Чип ввода-вывода (DC328) содержал буфер инструкций, микросеквенсор , исполнительный блок и буфер мини-трансляции (MTB). Буфер инструкций представляет собой 32-битный буфер с двумя записями, в котором хранятся предварительно выбранные инструкции. Это улучшило производительность за счет сохранения ряда инструкций готовыми к выполнению. Аппаратное обеспечение пыталось постоянно поддерживать заполненность буфера инструкций. Исполнительный блок состоял из шестнадцати 32-битных регистров общего назначения, определенных VAX ISA, арифметико-логического устройства (АЛУ) и устройства сдвига. MTB — это резервный буфер трансляции (TLB). Он содержал пять записей таблицы страниц (PTE): одну для инструкций и четыре для данных. В случае промаха используется резервный буфер трансляции (BTB) в микросхеме М. Чип I/E состоял из 60 000 транзисторов на кристалле размером 354 на 358 мил (8,99 на 9,09 мм) и площадью 126 732 мил. 2 (81,76 мм 2 ). Он рассеивал 5 Вт.

М чип

[ редактировать ]Микросхема M (DC329) отвечала за управление памятью и обработку прерываний. Он содержал теги резервного буфера трансляции (BTB), теги кэша и внутренние регистры процессора. Чип M также содержал функции ввода-вывода, определенные архитектурой VAX, и генерировал тактовый сигнал для набора микросхем.

Резервный буфер трансляции по существу представлял собой резервный буфер трансляции (TLB), который обрабатывал промахи в MTB. BTB содержал 512 записей таблицы страниц (PTE), из которых 256 относились к страницам системного пространства и 256 — к страницам пространства процесса. В чипе M имеется 128 тегов BTB, по одному на каждые четыре PTE. БТБ был реализован с внешним ОЗУ.

Имеется 26 внутренних регистров процессора, которые используются микрокодом для временного хранения при выполнении сложных инструкций, требующих нескольких циклов.

Чип М состоял из 54 000 транзисторов на кристалле размером 339 на 332 мил (8,61 на 8,43 мм) и площадью 112 548 мил. 2 (72,61 мм 2 ). Он рассеивал 3 Вт.

F-чип

[ редактировать ]Микросхема F (DC330) содержала блок операций с плавающей запятой (FPU). Он поддерживал большинство инструкций VAX с плавающей запятой и е_плавающий , d_плавающий и g_floating Типы данных определены в архитектуре VAX и также отвечают за выполнение инструкций целочисленного деления и умножения. Чип F получал коды операций от чипа I/E и микроинструкции из хранилища управления по шине MIB. Операнды были получены из памяти или регистров общего назначения по шине DAL, которая также используется для обратной записи результатов. Он состоял из 29 600 транзисторов на кристалле размером 341 на 288 мил (8,66 на 7,32 мм) на площади 98 208 мил. 2 (63,36 мм 2 ). Он рассеивал 2,5 Вт.

Чип F был производным от FPA, который принадлежал набору микропроцессоров J-11 , реализации PDP -11 . Предполагалось, что чип F будет совершенно новой конструкцией, разработанной для V-11, но от него отказались в пользу производной версии в рамках усилий по упрощению V-11, чтобы его можно было завершить быстрее, поскольку разработка 78032 MicroVAX началось.

Кэш

[ редактировать ]V-11 имеет внешний основной кэш объемом 8 КБ . Кэш был физически адресован и имеет блок кэша размером 64 байта .

Физический

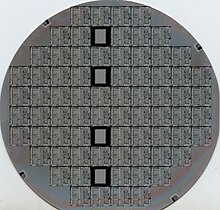

[ редактировать ]Чипсет V-11 содержал в общей сложности 1 183 600 транзисторов, распределенных по девяти кристаллам, изготовленным по технологии ZMOS компании Digital, 3,0-мкм NMOS- процессу с двумя уровнями межсоединения. (Буква Z в названии была выбрана потому, что она выглядела как цифра 2 — наличие двух слоев металла было примечательно.)

Ссылки

[ редактировать ]- « Техническое руководство по процессорам KA820/KA825 , третье издание, апрель 1987 г.». ЕК-КА820-ТМ-003. Корпорация цифрового оборудования.

Дальнейшее чтение

[ редактировать ]- Джонсон, Западная Нью; Херрик, Западная Вирджиния; Грундманн, WJ (октябрь 1984 г.). «Набор микросхем СБИС VAX» . Журнал IEEE твердотельных схем 19 (5): 663–674.

- Джонсон, В. (февраль 1984 г.). «ЦП суперминикомпьютера СБИС» . Сборник технических документов ISSCC : 174–175.