логика И-НЕ

обладает Булева функция И-НЕ свойством функциональной полноты . Это означает, что любое логическое выражение может быть перевыражено эквивалентным выражением , использующим только операции NAND . Например, функция НЕ(x) может быть эквивалентно выражена как NAND(x,x). В области цифровых электронных схем это означает, что можно реализовать любую булеву функцию, используя только вентили И-НЕ .

Математическое доказательство этого было опубликовано Генри М. Шеффером в 1913 году в « Трудах Американского математического общества» (Шеффер, 1913). Аналогичный случай применим к функции ИЛИ-НЕ , и это называется логикой ИЛИ-НЕ .

NAND

[ редактировать ]Вентиль И-НЕ представляет собой инвертированный И. вентиль Он имеет следующую таблицу истинности:

| ||||||||||||||||

Q = И -НЕ B

| ||||||||||||||||

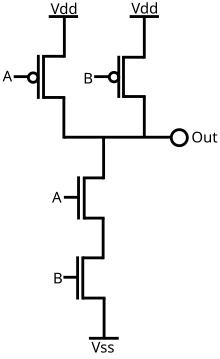

В логике КМОП , если на обоих входах A и B высокий уровень, то оба NMOS -транзистора (нижняя половина диаграммы) будут проводить ток, ни один из PMOS- транзисторов (верхняя половина) не будет проводить ток, и между ними будет установлен проводящий путь. выход и Vss (земля), что приводит к низкому уровню выходного сигнала. Если на обоих входах A и B низкий уровень, то ни один из NMOS-транзисторов не будет проводить ток, в то время как оба PMOS-транзистора будут проводить ток, создавая проводящий путь между выходом и Vdd (источником напряжения), повышая выходной сигнал. Если на любом из входов A или B низкий уровень, один из NMOS-транзисторов не будет проводить ток, один из PMOS-транзисторов будет проводить ток, и между выходом и Vdd (источником напряжения) будет установлен проводящий путь, в результате чего выходной сигнал станет высоким. Поскольку единственная конфигурация двух входов, которая приводит к низкому выходному сигналу, — это когда оба имеют высокий уровень, эта схема реализует логический вентиль И-НЕ (НЕ И).

Создание других вентилей с использованием вентилей И-НЕ.

[ редактировать ]Вентиль И-НЕ является универсальным вентилем , то есть любой другой вентиль может быть представлен как комбинация вентилей И-НЕ.

НЕТ

[ редактировать ]Логический элемент НЕ создается путем объединения входов логического элемента И-НЕ. Поскольку вентиль И-НЕ эквивалентен вентилю И, за которым следует вентиль НЕ, при объединении входов вентиля И-НЕ остается только вентиль НЕ.

| Желаемые НЕ ворота | NAND Строительство | ||||||

|---|---|---|---|---|---|---|---|

|  | ||||||

| Q = НЕ( А ) | = НЕ -И А | ||||||

| |||||||

И

[ редактировать ]Логический элемент И создается путем инвертирования выхода логического элемента И-НЕ, как показано ниже.

| Желаемый И Ворота | NAND Строительство | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А И Б | = ( А НЕ- Б ) И-НЕ ( А НЕ- Б ) | |||||||||||||||

| ||||||||||||||||

ИЛИ

[ редактировать ]Если изучить таблицу истинности для вентиля И-НЕ или применить законы Де Моргана , можно увидеть, что если какой-либо из входных данных равен 0, то на выходе будет 1. Однако, чтобы быть вентилем ИЛИ, выход должен быть 1. если какой-либо вход равен 1. Следовательно, если входы инвертированы, любой высокий входной сигнал вызовет высокий выходной сигнал.

| Желаемый ИЛИ Ворота | NAND Строительство | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А ИЛИ Б | = ( А НЕ- А ) И-НЕ ( B И-НЕ B ) | |||||||||||||||

| ||||||||||||||||

НИ

[ редактировать ]Вентиль ИЛИ — это вентиль ИЛИ с инвертированным выходом. Выходной сигнал имеет высокий уровень, когда ни вход A, ни вход B не имеют высокого уровня.

| Желаемый ворота NOR | NAND Строительство | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А НО B | = [ ( A NAND A ) NAND ( B NAND B ) ] NAND [ ( A NAND A ) NAND ( B NAND B ) ] | |||||||||||||||

| ||||||||||||||||

БЕСПЛАТНО

[ редактировать ]Вентиль «ИСКЛЮЧАЮЩЕЕ ИЛИ» создается путем соединения четырех вентилей И-НЕ, как показано ниже. Эта конструкция влечет за собой задержку распространения в три раза больше, чем у одного вентиля И-НЕ.

| Желаемый элемент XOR | NAND Строительство | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А исключающее ИЛИ B | = [ А NAND ( A NAND B ) ] NAND [ Б И-НЕ ( А- И-НЕ Б ) ] | |||||||||||||||

| ||||||||||||||||

Альтернативно, логический элемент XOR создается с учетом дизъюнктивной нормальной формы. , отмечая из закона де Моргана , что вентиль И-НЕ представляет собой вентиль ИЛИ с инвертированным входом. В этой конструкции используется пять ворот вместо четырех.

| Желаемые ворота | NAND Строительство |

|---|---|

|  |

| Q = А исключающее ИЛИ B | = [ B NAND ( A NAND A ) ] NAND [ А И-НЕ ( Б- И -НЕ Б ) ] |

ИСНО-ИЛИ

[ редактировать ]Вентиль XNOR создается с учетом дизъюнктивной нормальной формы. , отмечая из закона де Моргана , что вентиль И-НЕ представляет собой вентиль ИЛИ с инвертированным входом. Эта конструкция влечет за собой задержку распространения в три раза больше, чем у одного вентиля И-НЕ, и использует пять вентилей.

| Желаемый элемент XNOR | NAND Строительство | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = А ИСКЛЮЧАЮЩЕЕ ИЛИ B | = [ ( A NAND A ) NAND ( B NAND B ) ] NAND ( А И Б ) | |||||||||||||||

| ||||||||||||||||

В качестве альтернативы с инвертором можно использовать 4-вентильную версию вентиля XOR. Эта конструкция имеет задержку распространения в четыре раза (вместо трех) по сравнению с одиночным вентилем И-НЕ.

| Желаемые ворота | NAND Строительство |

|---|---|

|  |

| Q = А ИСКЛЮЧАЮЩЕЕ ИЛИ B | = { [ А И-НЕ ( А И-НЕ B ) ] И-НЕ [ B NAND ( A NAND B ) ] } NAND { [ А И-НЕ ( А И-НЕ B ) ] NAND [ B NAND ( A NAND B ) ] } |

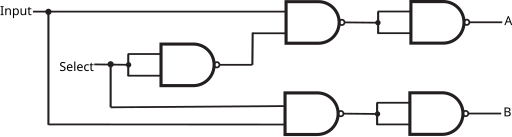

мультиплексор

[ редактировать ]Мультиплексор или вентиль MUX — это вентиль с тремя входами, который использует один из входов, называемый битом селектора, для выбора одного из двух других входов, называемых битами данных , и выводит только выбранный бит данных. [1]

ДЕМУКС

[ редактировать ]Демультиплексор выполняет функцию, противоположную мультиплексору: он принимает один входной сигнал и направляет его на один из двух возможных выходов в соответствии с битом селектора, который определяет, какой выход выбрать. [1] [ нарушение авторских прав? ]

| Желаемый шлюз DEMUX | NAND Строительство | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

См. также

[ редактировать ]- Структуры КМОП- транзисторов и геометрия нанесения кристаллов, из которых производятся логические элементы NAND.

- Sheffer stroke – other name

- НИ-логика . Как и вентили И-НЕ, вентили НИ-НЕ также являются универсальными вентилями.

- Функциональная полнота

Ссылки

[ редактировать ]- ^ Перейти обратно: а б Нисан, Ноам ; Шокен, Шимон (2005). «1. Булева логика». От NAND до тетриса: создание современного компьютера на основе первых принципов (PDF) . Массачусетский технологический институт Пресс. Архивировано из оригинала (PDF) 10 января 2017 г.

- Ланкастер, Дон (1974). Поваренная книга TTL (1-е изд.). Индианаполис, Индиана: Говард В. Сэмс. стр. 126–135 . ISBN 0-672-21035-5 .

- Шеффер, Х.М. (1913), «Набор из пяти независимых постулатов для булевых алгебр с применением к логическим константам», Transactions of the American Mathematical Society , 14 (4): 481–488, doi : 10.2307/1988701 , JSTOR 1988701

Внешние ссылки

[ редактировать ]- TTL NAND и вентили И — Все о схемах

- Действия по получению XOR из вентиля NAND.

- NandGame — игра о сборке компьютера с использованием только вентилей NAND.