исключающее ИЛИ-вентиль

| Вход | Выход | |

| А | Б | Исключающее ИЛИ Б |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Вентиль XOR (иногда EOR или EXOR и произносится как Исключающее ИЛИ ) — это цифровой логический вентиль , который дает истинный (1 или HIGH) выходной сигнал, когда количество истинных входов нечетное. Вентиль XOR реализует исключающее или ( ) из математической логики ; то есть истинный выходной сигнал получается, если один и только один из входных данных вентиля является истинным. Если оба входа ложны (0/LOW) или оба верны, результат будет ложным. XOR представляет собой функцию неравенства, т. е. выходное значение истинно, если входные данные не одинаковы, в противном случае выходное значение является ложным. Способ запомнить XOR: «должен быть один или другой, но не оба».

Вентиль XOR может служить «программируемым инвертором», в котором один вход определяет, инвертировать ли другой вход или просто передать его без изменений. Следовательно, он функционирует как инвертор (вентиль НЕ), который можно активировать или деактивировать с помощью переключателя. [1] [2]

XOR также можно рассматривать как сложение по модулю 2. В результате вентили XOR используются для реализации двоичного сложения в компьютерах. Полусумматор вентиля « состоит из вентиля «ИСКЛЮЧАЮЩЕЕ ИЛИ» и И» . Вентиль также используется в вычитателях и компараторах . [3]

Алгебраические выражения или или или все представляют собой вентиль XOR со A и B. входами Поведение XOR суммировано в таблице истинности, показанной справа.

Символы [ править ]

Существует три схематических обозначения вентилей XOR: традиционные символы ANSI и DIN и символ IEC . В некоторых случаях символ DIN используется с ⊕ вместо ≢. Для получения дополнительной информации см. Символы логических вентилей .

«=1» на символе IEC указывает, что выход активируется только одним активным входом.

|

|

| ||

| Схематическое обозначение ANSI XOR | Схематическое обозначение IEC XOR | Схематическое обозначение DIN XOR |

Логические символы ⊕, J pq и ⊻ могут использоваться для обозначения операции XOR в алгебраических выражениях.

C-подобные языки используют каретки символ ^ для обозначения побитового XOR. (Обратите внимание, что в этих языках каретка не обозначает логическое соединение (И), несмотря на сходство символов.)

Реализация [ править ]

Вентиль XOR чаще всего реализуется с использованием схем МОП-транзисторов . Некоторые из этих реализаций включают в себя:

И-ИЛИ-Инвертировать [ править ]

Вентиль XOR может быть реализован с использованием логики AOI . [4]

-

Вентиль XOR, использующий вентиль 2-2 ИЛИ-И-Инверт и инвертированные входы.

-

Вентиль «ИСКЛЮЧАЮЩЕЕ ИЛИ» с использованием вентиля И-ИЛИ-Инверт 2-1.

КМОП [ править ]

металл-оксид-полупроводник ( КМОП Реализация вентиля XOR ), соответствующая приведенной выше логике AOI. показаны ниже.

Слева nMOS и pMOS транзисторы расположены так, что входные пары и активируйте 2 pMOS-транзистора вверху слева или 2 pMOS-транзистора вверху справа соответственно, подключив Vdd к выходу для получения высокого логического уровня. Остальные входные пары и активируйте каждый из двух путей nMOS внизу к Vss для получения низкого логического уровня. [5]

инвертированные входы (например, от триггера Если доступны ), этот вентиль можно использовать напрямую. В противном случае для генерации потребуются два дополнительных инвертора по два транзистора каждый. и , доведя общее количество транзисторов до двенадцати.

Реализация AOI без инвертированного входа использовалась, например, в процессоре Intel 386 . [6]

-

Пример КМОП-вентиля XOR

-

КМОП-вентиль XOR с использованием AOI-Logic

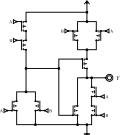

Трансмиссионные ворота [ править ]

Вентиль XOR также может быть реализован с использованием вентилей передачи с логикой проходного транзистора .

В этой реализации для генерации используются два вентиля передачи и два инвертора, не показанных на схеме. и всего восемь транзисторов, что на четыре меньше, чем в предыдущей конструкции. Функция XOR реализуется путем передачи на выход инвертированного значения A, когда B имеет высокий логический уровень, и передачи значения A, когда B имеет низкий логический уровень. поэтому, когда на обоих входах низкий уровень, передающий вентиль внизу выключен, а верхний включен и пропускает A, через который низкий уровень, поэтому выходной сигнал низкий. Когда оба имеют высокий уровень, только тот, который находится внизу, активен и пропускает инвертированное значение A, и, поскольку A высокий, выход снова будет низким. Аналогично, если B остается высоким, а A низким, выход будет равен который высокий, как и ожидалось, и если B низкий, а A высокий, значение A проходит, и на выходе получается высокий уровень, завершая таблицу истинности для вентиля XOR. [7]

Компромисс с предыдущей реализацией заключается в том, что, поскольку вентили передачи не являются идеальными переключателями, с ними связано сопротивление, поэтому в зависимости от уровня входного сигнала их каскадирование может ухудшить выходные уровни. [8]

Оптимизированная логика проходных ворот [ править ]

Предыдущую реализацию передающего вентиля можно дополнительно оптимизировать с восьми до шести транзисторов, реализовав функциональность инвертора, который генерирует и нижний проходной затвор всего с двумя транзисторами, расположенными как инвертор, но с истоком pMOS, подключенным к вместо Vdd и источник nMOS, подключенный к вместо земли. [8]

Два крайних левых транзистора, упомянутых выше, выполняют оптимизированную условную инверсию A, когда B находится на высоком логическом уровне, используя логику проходного транзистора для уменьшения количества транзисторов, а когда B находится на низком логическом уровне, их выход находится в состоянии с высоким импедансом. Два в середине представляют собой передающий вентиль , который переводит выходной сигнал в значение A, когда B находится на низком логическом уровне, а два крайних правых транзистора образуют инвертор, необходимый для генерации используется передающим затвором и логической схемой проходного транзистора. [9]

Как и в предыдущей реализации, следует учитывать прямое соединение входов с выходами через транзисторы затвора или через два крайних левых транзистора, особенно при их каскадировании. [8]

Альтернативы [ править ]

Если элемент определенного типа недоступен, схема, реализующая ту же функцию, может быть построена из других доступных элементов. Схема, реализующая функцию исключающее ИЛИ, может быть тривиально построена из вентиля исключающее ИЛИ, за которым следует вентиль НЕ . Если мы рассмотрим выражение мы можем построить схему вентиля XOR напрямую, используя вентили AND, OR и NOT . Однако для этого подхода требуется пять ворот трех разных типов.

В качестве альтернативы, если доступны разные элементы, мы можем применить булеву алгебру для преобразования как указано выше, и примените закон де Моргана к последнему члену, чтобы получить который можно реализовать, используя только четыре вентиля, как показано справа. интуитивно понятно, что XOR эквивалентно OR, за исключением случаев, когда оба A и B имеют высокий уровень. Таким образом, И для ИЛИ с последующим И-НЕ, которое дает низкий уровень только тогда, когда оба A и B имеют высокий уровень, эквивалентно исключающему ИЛИ.

Схема вентиля «ИСКЛЮЧАЮЩЕЕ ИЛИ» может быть составлена из четырех вентилей И-НЕ . Фактически, вентили И-НЕ и ИЛИ-НЕ являются так называемыми «универсальными вентилями», и любая логическая функция может быть построена либо из логики И-НЕ , либо только из логики ИЛИ-НЕ . Если четыре вентиля И-НЕ заменить вентилями ИЛИ-НЕ , в результате образуется вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ , который можно преобразовать в вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ путем инвертирования выхода или одного из входов (например, с помощью пятого вентиля ИЛИ-НЕ ).

| Желаемые ворота | NAND-конструкция | НОР строительство |

|---|---|---|

|

|

|

Альтернативное расположение состоит из пяти вентилей ИЛИ-НЕ в топологии, которая подчеркивает построение функции из , отмечая из закона де Моргана , что вентиль ИЛИ-НЕ с инвертированным входом является вентилем И . Другое альтернативное расположение — пять вентилей И-НЕ в топологии, которая подчеркивает построение функции из , отмечая из закона де Моргана , что вентиль И-НЕ с инвертированным входом представляет собой вентиль ИЛИ .

| Желаемые ворота | NAND-конструкция | НОР строительство |

|---|---|---|

|

|

|

Для конструкций NAND верхняя компоновка требует меньшего количества вентилей. Для конструкций NOR нижнее расположение обеспечивает преимущество более короткой задержки распространения (временной задержки между изменением входа и изменением выхода).

Стандартные пакеты чипов [ править ]

Чипы XOR легко доступны. Наиболее распространенными стандартными кодами чипов являются:

- 4070: КМОП-вентили XOR с четырьмя входами и двойным входом. [10]

- 4030: КМОП-вентили XOR с четырьмя входами и двойным входом. [11]

- 7486: TTL- клапаны XOR с четырьмя входами и двойным входом. [10]

Более двух входов [ править ]

Буквальная интерпретация имени «исключающее или» или соблюдение прямоугольного символа IEC поднимает вопрос о правильном поведении с дополнительными входами. [12] Если бы логический вентиль должен был принимать три или более входных сигнала и выдавать истинный выходной сигнал, если только один из этих входных данных был истинным, то это, по сути, был бы детектор с одним горячим входом (и действительно, это справедливо только для двух входов). Однако на практике это редко реализуется таким образом.

Чаще всего последующие входные данные применяются через каскад двоичных операций «исключающее ИЛИ»: первые два сигнала подаются на логический элемент «исключающее ИЛИ», затем выход этого элемента подается на второй логический элемент «исключающее ИЛИ» вместе с третьим сигналом. и так далее для всех оставшихся сигналов. В результате получается схема, которая выводит 1, когда количество единиц на ее входах нечетное, и 0, когда количество входящих единиц четное. Это делает его практически полезным в качестве генератора четности по модулю 2 или сумматора .

Например, микросхема 74LVC1G386 рекламируется как логический вентиль с тремя входами и реализует генератор четности. [13]

Приложения [ править ]

Вентиляторы «ИСКЛЮЧАЮЩЕЕ ИЛИ» и «И» — две наиболее часто используемые структуры в приложениях СБИС . [14]

Дополнение [ править ]

Логический вентиль XOR можно использовать как однобитовый сумматор , который складывает любые два бита для получения одного бита. Например, если мы добавим 1 плюс 1 в двоичном формате мы ожидаем двухбитный ответ, 10 (т.е. 2 в десятичном формате). Поскольку конечный бит суммы в этом выводе получается с помощью XOR, предыдущий бит переноса вычисляется с помощью логического элемента AND . Это основной принцип в Half Adders . немного большего размера Схема полного сумматора может быть объединена в цепочку для сложения более длинных двоичных чисел.

В определенных ситуациях входы вентиля ИЛИ (например, в полном сумматоре) или вентиля Исключающее ИЛИ никогда не могут одновременно быть единицами. Поскольку это единственная комбинация, в которой выходные сигналы вентилей ИЛИ и Исключающее ИЛИ различаются, вентиль ИЛИ можно заменить вентилем Исключающее ИЛИ (или наоборот) без изменения результирующей логики. Это удобно, если схема реализуется с использованием простых интегральных микросхем, которые содержат только один тип вентиля на микросхему.

Генератор псевдослучайных чисел [ править ]

Генераторы псевдослучайных чисел (PRN) , в частности регистры сдвига с линейной обратной связью (LFSR), определяются в терминах операции «исключающее или». Следовательно, подходящая установка элементов XOR может моделировать регистр сдвига с линейной обратной связью для генерации случайных чисел.

Фазовые детекторы [ править ]

Элементы XOR могут использоваться в простейших фазовых детекторах . [15] : 425

Буферизировать или инвертировать сигнал [ править ]

Вентиль XOR может использоваться для легкого переключения между буферизацией и инвертированием сигнала. Например, к выходу семисегментного дисплея схемы декодера можно добавить вентили XOR , чтобы позволить пользователю выбирать между выходным сигналом с активным низким или активным высоким уровнем.

Корреляция и обнаружение последовательности [ править ]

Ворота XOR создают 0 когда оба входа совпадают. При поиске определенного битового шаблона или последовательности PRN в очень длинной последовательности данных можно использовать серию логических элементов XOR для параллельного сравнения строки битов из последовательности данных с целевой последовательностью. Количество 0 Затем выходные данные можно подсчитать, чтобы определить, насколько хорошо последовательность данных соответствует целевой последовательности. Корреляторы используются во многих устройствах связи, таких как приемники и декодеры CDMA , для исправления ошибок и кодирования каналов. В приемнике CDMA корреляторы используются для извлечения полярности конкретной последовательности PRN из объединенного набора последовательностей PRN.

Коррелятор ищет 11010 в последовательности данных 1110100101 будет сравнивать входящие биты данных с целевой последовательностью при каждом возможном смещении, подсчитывая количество совпадений (нулей):

1110100101 (data)

11010 (target)

00111 (XOR) 2 zero bits

1110100101

11010

00000 5 zero bits

1110100101

11010

01110 2 zero bits

1110100101

11010

10011 2 zero bits

1110100101

11010

01000 4 zero bits

1110100101

11010

11111 0 zero bits

Matches by offset:

.

: :

: : : : :

-----------

0 1 2 3 4 5

В этом примере наилучшее совпадение происходит, когда целевая последовательность смещена на 1 бит и все пять битов совпадают. При смещении на 5 бит последовательность точно соответствует своей обратной. Глядя на разницу между количеством единиц и нулей, выходящих из банка элементов XOR, легко увидеть, где возникает последовательность и инвертирована она или нет. Более длинные последовательности легче обнаружить, чем короткие.

Аналитическое представление [ править ]

является аналитическим представлением вентиля XOR:

является альтернативным аналитическим представлением.

См. также [ править ]

Ссылки [ править ]

- ^ Брош, Джеймс Д. (2012). Практические программируемые схемы: Руководство по ПЛИС, конечным автоматам и микроконтроллерам . Эльзевир Наука. п. 20. ISBN 978-0323139267 .

- ^ Ван Хаутвен, Лоуренс (2017). Крипто 101 (PDF) . п. 17.

- ^ Флетчер, Уильям (1980). Инженерный подход к цифровому дизайну . Прентис-Холл. п. 98 . ISBN 0-13-277699-5 .

- ^ Фишер, П. «Пропозициональная логика и вентили» (PDF) . Гейдельбергский университет . Проверено 21 января 2024 г.

- ^ Педрони, Волней А. (25 января 2008 г.). Цифровая электроника и дизайн с использованием VHDL . Морган Кауфманн. ISBN 978-0-08-055755-7 . Проверено 8 ноября 2022 г.

- ^ Шириф, Кен. «Две интересные схемы XOR внутри процессора Intel 386» . Проверено 14 января 2024 г.

- ^ Оклобдзия, Вожин Г. (26 декабря 2001 г.). Справочник по компьютерной инженерии . ЦРК Пресс. ISBN 978-0-8493-0885-7 . Проверено 8 ноября 2022 г.

- ↑ Перейти обратно: Перейти обратно: а б с Проектирование комбинационных логических элементов в КМОП (PDF) . п. 233 . Проверено 9 ноября 2022 г.

- ^ Аннаратоне, Сильвия (6 декабря 2012 г.). Проектирование цифровой КМОП-схемы . Springer Science & Business Media. ISBN 978-1-4613-2285-6 . Проверено 8 ноября 2022 г.

- ↑ Перейти обратно: Перейти обратно: а б Ферджалла, Мохаммед (15 июня 2011 г.). Введение в цифровые системы: моделирование, синтез и симуляция с использованием VHDL . Джон Уайли и сыновья. п. 38. ISBN 978-1-118-00770-9 . Проверено 9 ноября 2022 г.

- ^ Росс, Дикон; Лоу, Дуг (24 сентября 2013 г.). Электроника «Все в одном» для чайников — Великобритания . Джон Уайли и сыновья. п. 647. ИСБН 978-1-118-58971-7 . Проверено 9 ноября 2022 г.

- ^ https://www.edn.com/the-xor-versus-sum-modulo-2

- ^ 74LVC1G386. Архивировано 29 декабря 2009 г. в Wayback Machine . техническом описании

- ^ «Сравнение различных методов проектирования вентилей XOR и AND с использованием инструмента моделирования EDA» .

Элементы XOR и AND являются наиболее важными базовыми строительными блоками любых приложений СБИС.

- ^ Рабай, Ян М. (1996). Цифровые интегральные схемы: взгляд на проектирование . Река Аппер-Сэддл, Нью-Джерси: Прентис-Холл. ISBN 978-0-13-178609-7 .

Для этой статьи необходимы дополнительные или более конкретные категории . ( май 2021 г. ) |