МОЩНОСТЬ5

POWER5 МСМ | |

| Общая информация | |

|---|---|

| Запущен | 2004 |

| Разработано | ИБМ |

| Производительность | |

| Макс. процессора Тактовая частота | от 1,5 ГГц до 2,3 ГГц |

| Кэш | |

| L1 Кэш | 32+32 КБ/ядро |

| Кэш L2 | 1875 МБ/чип |

| Кэш L3 | 36 МБ/чип (вне чипа) |

| Архитектура и классификация | |

| Технологический узел | от 130 до 90 нм |

| Набор инструкций | PowerPC 2.02 |

| Физические характеристики | |

| Ядра |

|

| История | |

| Предшественник | МОЩНОСТЬ4 |

| Преемник | МОЩНОСТЬ6 |

| POWER , PowerPC и Power ISA. Архитектуры |

|---|

| NXP (ранее Freescale и Motorola) |

| ИБМ |

|

| IBM/Нинтендо |

| Другой |

| Ссылки по теме |

| Отменено выделено серым цветом , историческое — курсивом |

POWER5 разработанный — микропроцессор, и изготовленный IBM . Это улучшенная версия POWER4 . Основными улучшениями являются поддержка одновременной многопоточности (SMT) и встроенный контроллер памяти . POWER5 — это двухъядерный микропроцессор, каждое ядро которого поддерживает один физический поток и два логических потока, всего два физических потока и четыре логических потока.

История [ править ]

Технические детали микропроцессора были впервые представлены на конференции Hot Chips 2003 года . Более полное описание было дано на Microprocessor Forum 2003 14 октября 2003 г. POWER5 не продавался открыто и использовался исключительно IBM и их партнерами. Системы, использующие микропроцессор, были представлены в 2004 году. POWER5 конкурировал на рынке высокопроизводительных корпоративных серверов, в основном с Intel Itanium 2 и, в меньшей степени, с Sun Microsystems UltraSPARC IV и Fujitsu SPARC64 V. В 2005 году на смену ему пришла улучшенная версия POWER5+.

Описание [ править ]

POWER5 является дальнейшим развитием POWER4 . Добавление двусторонней многопоточности потребовало дублирования стека возврата, счетчика программ , буфера инструкций, модуля группового завершения и очереди сохранения, чтобы каждый поток мог иметь свой собственный. Большинство ресурсов, таких как файлы регистров и исполнительные блоки, являются общими, хотя каждый поток видит свой собственный набор регистров. POWER5 реализует одновременную многопоточность (SMT), при которой два потока выполняются одновременно. POWER5 может отключить SMT для оптимизации текущей рабочей нагрузки.

Поскольку многие ресурсы, такие как файлы регистров, совместно используются двумя потоками, во многих случаях их емкость увеличивается, чтобы компенсировать потерю производительности. Количество целочисленных регистров и регистров с плавающей запятой увеличено до 120 каждый с 80 целочисленных и 72 регистров с плавающей запятой в POWER4. Емкость очереди выдачи с плавающей запятой также увеличена до 24 записей с 20. Емкость единого кэша L2 увеличена до 1,875 МБ, а ассоциативность набора - до 10-сторонней. Унифицированный кэш L3 был встроен в корпус, а не располагался снаружи в отдельных чипах. Его емкость была увеличена до 36 МБ. Как и в POWER4, кэш используется двумя ядрами совместно. Доступ к кэшу осуществляется через две однонаправленные 128-битные шины, работающие на половине частоты ядра.

Встроенный контроллер памяти поддерживает до 64 ГБ памяти DDR и DDR2 . Он использует высокочастотные последовательные шины для связи с внешними буферами, которые соединяют модули памяти с двойным расположением выводов (DIMM) с микропроцессором.

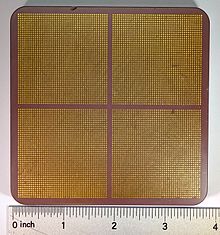

POWER5 содержит 276 миллионов транзисторов и имеет площадь 389 мм. 2 . Он изготовлен IBM по (КМОП) кремний на изоляторе (SOI) технологии комплементарного металл-оксид-полупроводник толщиной 0,13 мкм с восемью слоями медных межсоединений . Кристалл POWER5 упакован либо в двухчиповый модуль (DCM), либо в многочиповый модуль (MCM). DCM содержит один кристалл POWER5 и связанный с ним кристалл кэша L3. MCM содержит четыре кристалла POWER5 и четыре кристалла кэша L3, по одному на каждый кристалл POWER5, и имеет размеры 95 на 95 мм. [1] [2]

Несколько процессоров POWER5 в высокопроизводительных системах можно объединить в один векторный процессор с помощью технологии ViVA (виртуальная векторная архитектура).

POWER5+ [ править ]

POWER5+ представляет собой улучшенную версию POWER5, представленную 4 октября 2005 года. Первоначально улучшения заключались в более низком энергопотреблении из-за нового процесса, по которому он был изготовлен. В чипе POWER5+ используется техпроцесс 90 нм. Это привело к уменьшению размера матрицы с 389 мм. 2 до 243 мм 2 .

Тактовая частота не повышалась при запуске и оставалась в диапазоне от 1,5 до 1,9 ГГц. 14 февраля 2006 г. в новых версиях тактовая частота была повышена до 2,2 ГГц, а затем до 2,3 ГГц 25 июля 2006 г.

POWER5+ был упакован в те же корпуса, что и предыдущие микропроцессоры POWER5, но также был доступен в четырехкристальном модуле (QCM), содержащем два кристалла POWER5+ и два кристалла кэша L3, по одному на каждый кристалл POWER5+. Эти чипы QCM работали на тактовой частоте от 1,5 до 1,8 ГГц.

Продукты [ править ]

IBM использует микропроцессоры DCM и MCM POWER5 в своих System p и System i семействах серверов , в своем сервере хранения DS8000 , а также в качестве встроенных микропроцессоров в своих высокопроизводительных принтерах Infoprint. Микропроцессоры DCM POWER5 используются IBM в своей высокопроизводительной рабочей станции IntelliStation POWER 285 . Сторонними пользователями микропроцессоров POWER5 являются Groupe Bull на своих серверах Escala и Hitachi на своих компьютерах SR11000 с до 128 микропроцессорами POWER5+, несколько установок которых включены в список TOP500 суперкомпьютеров 2007 года. IBM использует POWER5+ QCM в своих серверах System p5 510Q, 520Q, 550Q и 560Q. [3]

Примечания [ править ]

- ^ Глазковски, «IBM поднимает занавес над Power5».

- ^ Кревелл, «Power5 достигает максимума по пропускной способности».

- ^ Четырехъядерный модуль IBM System p5 на основе технологии POWER5+: технический обзор и введение

См. также [ править ]

Ссылки [ править ]

- «IBM анонсирует Power5». (8 сентября 2003 г.). Отчет микропроцессора .

- Клабес, Иоахим и др. (2004). «Проектирование и реализация микропроцессора POWER5». Материалы Международной конференции IEEE по твердотельным схемам 2004 г.

- Глазковски, Питер Н. (14 октября 2003 г.). «IBM поднимает занавес над Power5». Отчет микропроцессора .

- Калла, Рон; Синхарой, Баларам; Тендлер, Джоэл М. (2004). «Чип IBM Power5: двухъядерный многопоточный процессор». IEEE микро .

- Кревелл, Кевин (22 декабря 2003 г.). «Power5 превосходит пропускную способность» . Отчет микропроцессора .

- Синхарой, Баларам и др. (2005). «Микроархитектура системы POWER5». Журнал исследований и разработок IBM .

- Вэнс, Эшли (4 октября 2005 г.). «IBM наполняет линейку Unix Power5+» . Регистр .

Внешние ссылки [ править ]

- Оценка супертяжеловесов , сравнение и анализ POWER5 и Montecito, объясняющие основные изменения между POWER4 и POWER5, а также оценки производительности.

- Высокопроизводительный кластер IBM Power5+ p5-575 Cluster 1600 и система хранения данных DDN S2A9550 , Техасский университет A&M