Альфа 21064

Alpha 21064 — это микропроцессор , разработанный и изготовленный Digital Equipment Corporation , в котором реализована Alpha (представленная как Alpha AXP) архитектура набора команд (ISA). Он был представлен как DECchip 21064, прежде чем был переименован в 1994 году. 21064 также известен под своим кодовым названием EV4 . Об этом было объявлено в феврале 1992 года, а массовое поступление в продажу началось в сентябре 1992 года. 21064 был первой коммерческой реализацией Alpha ISA и первым микропроцессором Digital, доступным на коммерческой основе. На смену ей пришла производная Alpha 21064A в октябре 1993 года. Эта последняя версия была заменена Alpha 21164 в 1995 году.

История

[ редактировать ]Первым процессором Alpha был тестовый чип под кодовым названием EV3 . Этот тестовый чип был изготовлен с использованием 1,0- микрометровой (мкм) технологии CMOS-3 компании Digital. Тестовый чип не имел блока с плавающей запятой только 1 КБ и имел кэш . Тестовый чип использовался для подтверждения работы агрессивных методов проектирования схем . Тестовый чип вместе с симуляторами и эмуляторами также использовался для запуска прошивки и различных операционных систем , поддерживаемых компанией.

Производственный чип под кодовым названием EV4 был изготовлен с использованием технологии CMOS-4 0,75 мкм компании Digital. Дирк Мейер и Эдвард Маклеллан были микроархитекторами. Эд разработал логику задачи, а Дирк разработал другие основные блоки. Джим Монтанаро руководил реализацией схемы. EV3 использовался в демонстрационном блоке Alpha (ADU), многопроцессорной системе, используемой Digital для разработки программного обеспечения для платформы Alpha до того, как стали доступны детали EV4. [1]

Модель 21064 была представлена на 39-й Международной конференции по твердотельным схемам (ISSCC) в середине февраля 1992 года. Об этом было объявлено 25 февраля 1992 года, и в тот же день был представлен образец с частотой 150 МГц. Его цена составляла 3375 долларов за партию от 100 штук, 1650 долларов за партию от 100 до 1000 и 1560 долларов за партию более 1000 штук. Массовые поставки начались в сентябре 1992 года.

В начале февраля 1993 года цена версии 150 МГц была снижена до 1096 долларов с 1559 долларов в количествах более 1000 штук.

25 февраля 1993 года была представлена частота 200 МГц, доступны образцы комплектов по цене 3495 долларов. В объемах он стоил 1231 доллар за единицу в количестве более 10 000 штук. Объемные заказы были приняты в июне 1993 года, а поставки - в августе 1993 года. В ответ цена на версию 150 МГц была снижена. Стоимость образца комплекта была снижена с апреля 1993 года до 1690 долларов с 3375 долларов; а по объему с июля 1993 года она была снижена до 853 долларов США с 1355 долларов США за единицу в количествах более 10 000 штук.

С выпуском Alpha 21066 и Alpha 21068 10 сентября 1993 года компания Digital скорректировала позиционирование существующих 21064 и представила версию с частотой 166 МГц по цене 499 долларов за единицу в количестве 5000 штук. Цена версии 150 МГц была снижена до 455 долларов за единицу при партии 5000 штук.

6 июня 1994 года цена версии с частотой 200 МГц была снижена на 31% до 544 долларов, чтобы сравнить ее с Pentium с частотой 60 МГц; и версия 166 МГц на 19% до 404 долларов за единицу в количестве 5000 штук, начиная с 3 июля 1994 года.

Alpha 21064 был изготовлен на Digital в Гудзоне, штат Массачусетс , и в Южном Квинсферри, Шотландия заводах .

Пользователи

[ редактировать ]21064 в основном использовался в компьютерах высокого класса, таких как рабочие станции и серверы . Включены пользователи:

- Aspen Systems на своих рабочих станциях Alpine

- Carrera Computers на своих рабочих станциях Hercules 150, Hercules 200 и Pantera II

- Cray Research , которая использовала процессор 21064 с частотой 150 МГц в своих Cray T3D. суперкомпьютерах

- Digital: DECpc AXP 150 рабочие станции начального уровня DEC 2000 AXP , серверы начального уровня DEC 3000 AXP , рабочие станции и серверы начального уровня DEC 4000 AXP , серверы среднего уровня и серверы DEC 7000/10000 AXP высшего класса.

- Encore Computer в своем высокопроизводительном компьютере реального времени Infinity R/T.

Производительность

[ редактировать ]21064 был самым производительным микропроцессором с момента его появления до 1993 года, после того как компания International Business Machines (IBM) представила многокристальный процессор POWER2 . Впоследствии он стал самым производительным однокристальным микропроцессором и занимал эту позицию до тех пор, пока в октябре 1993 года не был представлен 21064A с частотой 275 МГц. [2]

Описание

[ редактировать ]Alpha 21064 представляет собой суперконвейерный микропроцессор двойного назначения суперскалярный , который выполняет инструкции в определенном порядке . Он способен выдавать до двух инструкций за каждый такт четырем функциональным блокам: целочисленному блоку , блоку с плавающей запятой (FPU), блоку адреса и блоку ветвления. Целочисленный конвейер состоит из семи этапов, а конвейер с плавающей запятой — из десяти этапов. Первые четыре этапа обоих конвейеров идентичны и реализуются I-Box.

Я-бокс

[ редактировать ]I-box — это блок управления ; он извлекает, декодирует и выдает инструкции, а также управляет конвейером. [3] На первом этапе из I-кэша извлекаются две инструкции. Прогнозирование ветвления выполняется логикой I-блока на втором этапе. Используется либо статическое прогнозирование, либо динамическое прогнозирование. Статическое предсказание проверяло знаковый бит поля смещения инструкции ветвления и предсказывало, что ветвь взята, если знаковый бит указывал на обратную ветвь (если знаковый бит содержал 1). Динамическое предсказание исследовало запись в таблице истории ветвей, состоящей из 2048 записей по 1 биту. Если запись содержала 1, ветвь считалась занятой. [4] Если использовалось динамическое прогнозирование, точность прогнозирования ветвей для большинства программ составляет примерно 80%. [5] Штраф за неправильное предсказание ветвления составляет четыре цикла. [6]

Эти инструкции декодируются на третьем этапе. Затем I-box проверяет, доступны ли ресурсы, необходимые для двух инструкций, на четвертом этапе. В этом случае инструкции выдаются при условии, что их можно объединить в пары. Какие инструкции можно было спарить, определялось количеством портов чтения и записи в файле целочисленных регистров. [7] 21064 может выдавать: целочисленную операцию с операцией с плавающей запятой, любую инструкцию загрузки/сохранения с любой инструкцией операции, целочисленную операцию с целочисленной ветвью или операцию с плавающей запятой с ветвью с плавающей запятой. Две комбинации не допускались: целочисленная операция и хранилище с плавающей запятой, а также операция с плавающей запятой и целочисленное хранилище. Если одна из двух инструкций не может быть выдана вместе, первые четыре этапа приостанавливаются до тех пор, пока не будет выдана оставшаяся команда. Первые четыре этапа также останавливаются в том случае, если инструкция не может быть выдана из-за недоступности ресурсов, зависимостей или подобных условий.

I-box содержит два резервных буфера трансляции (TLB) для трансляции виртуальных адресов в физические адреса . Эти TLB называются буферами трансляции инструкций (ITB). Кэш ITB недавно использовал записи таблицы страниц для потока инструкций. ITB с восемью входами используется для страниц размером 8 КБ , а ITB с четырьмя входами — для страниц размером 4 МБ. Оба ITB полностью ассоциативны и используют не последний использованный алгоритм замены. [8]

Исполнение

[ редактировать ]Выполнение всех инструкций начинается на пятом этапе. Файлы регистров считываются на четвертом этапе. Трубопроводы, начинающиеся на пятом этапе, не могут быть остановлены.

Целочисленная единица

[ редактировать ]Целочисленный модуль отвечает за выполнение целочисленных инструкций. Он состоит из файла целочисленных регистров (IRF) и электронного ящика. IRF содержит тридцать два 64-битных регистра и имеет четыре порта чтения и два порта записи, которые поровну разделены между целочисленным блоком и блоком ветвления. [9] Электронный блок содержит сумматор , логический блок, бочкообразный переключатель и умножитель . За исключением инструкций умножения, сдвига и манипуляции с байтами, большинство целочисленных инструкций завершаются к концу пятого этапа и, таким образом, имеют задержку в один цикл. Механизм сдвига ствола является конвейерным, но инструкции сдвига и манипуляции с байтами не завершаются к концу шестого этапа и, таким образом, имеют задержку в два цикла. Множитель не был конвейерным для экономии площади кристалла; [5] таким образом, команды умножения имеют переменную задержку от 19 до 23 циклов в зависимости от операндов. На седьмом этапе целочисленные инструкции записывают свои результаты в IRF.

Адресный блок

[ редактировать ]Адресный блок, также известный как «A-box», выполнял инструкции загрузки и сохранения. Чтобы позволить блоку адреса и целочисленному блоку работать параллельно, адресный блок имеет свой собственный сумматор смещения , который он использует для вычисления виртуальных адресов вместо использования сумматора в целочисленном блоке. [10] (TLB) с 32 записями Полностью ассоциативный буфер преобразования используется для преобразования виртуальных адресов в физические адреса . [10] Этот TLB называется буфером трансляции данных (DTB). В 21064 реализован 43-битный виртуальный адрес и 34-битный физический адрес, поэтому он способен адресовать 8 ТБ виртуальной памяти и 16 ГБ физической памяти .

Инструкции сохранения приводят к буферизации данных в буфере записи размером 4 по 32 байта. Буфер записи улучшил производительность за счет сокращения количества операций записи на системную шину за счет объединения данных из соседних хранилищ и временной задержки хранилищ, что позволяет быстрее обслуживать нагрузки, поскольку системная шина используется не так часто. [10]

Модуль с плавающей запятой

[ редактировать ]Модуль операций с плавающей запятой состоит из файла регистров с плавающей запятой (FRF) и F-блока. [7] FRF содержит тридцать два 64-битных регистра и имеет три порта чтения и два порта записи. F-блок содержал конвейер с плавающей запятой и неконвейерный блок деления, который удалял один бит за цикл.

На четвертом этапе считывается файл регистров с плавающей запятой, и данные форматируются в дробь, показатель степени и знак. При выполнении инструкций сложения сумматор вычисляет разность показателей и запускается предсказательный детектор лидирующей единицы или нуля с использованием входных операндов для нормализации результата. При выполнении инструкций умножения множимое генерируется 3 X.

На пятом и шестом этапах для сложения и вычитания выполняются выравнивание или сдвиг нормализации и вычисления липких битов. Инструкции умножения умножаются в конвейерном массиве с двусторонним чередованием, который использует алгоритм Бута с основанием 8 . [5] [11] На восьмом этапе окончательное сложение выполняется параллельно с округлением. Инструкции с плавающей запятой записывают свои результаты в FRF на десятом этапе. [11]

Инструкции, выполняемые в конвейере, имеют задержку в шесть циклов. [11] Деления одинарной точности (32 бита) и двойной точности (64 бита), которые выполняются в блоке неконвейерного деления, имеют задержку 31 и 61 цикл соответственно. [12]

Тайники

[ редактировать ]21064 имеет два основных встроенных кэша : кэш данных объемом 8 КБ (известный как D-кэш), использующий политику сквозной записи, и кэш инструкций объемом 8 КБ (известный как I-кэш). Оба кэша имеют прямое отображение для доступа за один цикл и имеют размер строки 32 байта. Кэши построены из шеститранзисторных ячеек статической оперативной памяти (SRAM) площадью 98 мкм. 2 . Кэши имеют ширину 1024 ячейки и высоту 66 ячеек, причем два верхних ряда используются для резервирования.

Поддерживался дополнительный внешний вторичный кэш, известный как B-кэш, емкостью от 128 КБ до 16 МБ. Кэш работал на частоте от одной трети до одной шестнадцатой внутренней тактовой частоты, или от 12,5 до 66,67 МГц при частоте 200 МГц. [13] B-кэш имеет прямое отображение и по умолчанию имеет размер строки 128 байт, который можно настроить для использования большего количества. Доступ к B-кэшу осуществляется через системную шину.

Внешний интерфейс

[ редактировать ]Внешний интерфейс представляет собой 128-битную шину данных , работающую на частоте от половины до одной восьмой внутренней тактовой частоты, или от 25 до 100 МГц при частоте 200 МГц. Ширину шины можно было настраивать, системы, использующие 21064, могли иметь 64-битный внешний интерфейс. Внешний интерфейс также состоял из 34-битной адресной шины .

Изготовление

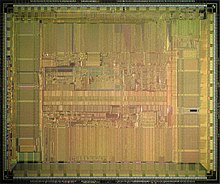

[ редактировать ]

21064 содержал 1,68 миллиона транзисторов. [14] Оригинальный EV4 был изготовлен компанией Digital по технологии CMOS-4, которая имеет размер элемента 0,75 мкм и три уровня алюминиевых межсоединений . [14] Размеры EV4 составляют 13,9 x 16,8 мм, площадь составляет 233,52 мм. 2 . Более поздний EV4S был изготовлен из CMOS-4S, оптической усадки CMOS-4 на 10% с размером элемента 0,675 мкм. Размеры этой версии 12,4 на 15,0 мм, площадь 186 мм. 2 . [15]

В 21064 использовался источник питания напряжением 3,3 В (В). [14] EV4 рассеивал максимум 30 Вт на частоте 200 МГц. EV4S рассеивает максимум 21,0 Вт на частоте 150 МГц, 22,5 Вт на частоте 166 МГц и 27,0 Вт на частоте 200 МГц. [16]

Упаковка

[ редактировать ]

21064 упакован в 431- контактную решетку из оксида алюминия и керамики (PGA) размером 61,72 мм на 61,72 мм. [17] Из 431 контакта 291 предназначался для сигналов, а 140 — для питания и земли. [14] [18] Радиатор вольфрамового крепится непосредственно к корпусу и фиксируется гайками, прикрепленными к двум шпилькам, выступающим из теплоотвода .

Производные

[ редактировать ]Альфа 21064А

[ редактировать ]

Alpha 21064A , представленный как DECchip 21064A под кодовым названием EV45 , представляет собой дальнейшее развитие Alpha 21064, представленного в октябре 1993 года. Он работал на тактовых частотах 200, 225, 233, 275 и 300 МГц. Модель 225 МГц была заменена моделью 233 МГц 6 июля 1994 года, которая на момент выпуска стоила 788 долларов США при партии 5000 штук, что на 10% меньше, чем модель 225 МГц, которую она заменила. В тот же день цены на 275 МГц также были снижены на 25% до 1083 долларов США в количестве 5000 штук. Модель с тактовой частотой 300 МГц была анонсирована и протестирована 2 октября 1995 года и была отправлена в декабре 1995 года. Была также одна модель, 21064A-275-PC, которая была ограничена запуском Windows NT или операционных систем , использующих управление памятью Windows NT. модель.

21064A пришел на смену оригинальному 21064 как высокопроизводительный микропроцессор Alpha. Впоследствии он нашел наибольшее применение в высокопроизводительных системах. Включены пользователи:

- Цифровой в некоторых моделях систем DEC 3000 AXP, DEC 4000 AXP и DEC 7000/10000 AXP.

- Aspen Systems на своей рабочей станции Alpine

- BTG, которая использовала модель с частотой 275 МГц в своем RISC-ПК Action AXP275.

- Carrera Computers на своей рабочей станции Cobra AXP 275

- NekoTech, которая использовала модель с частотой 275 МГц, разогнанную на 5% до 289 МГц, в своей рабочей станции Mach 2-289-T.

- Network Appliance (ныне NetApp), использовавшая в своих системах хранения модель 275 МГц.

21064A имел ряд микроархитектурных улучшений по сравнению с 21064. Первичные кэши были улучшены двумя способами: емкость I-кэша и D-кэша была увеличена вдвое с 8 КБ до 16 КБ, а к тегу кэша была добавлена защита по четности и кэшировать массивы данных. Деление с плавающей запятой имеет меньшую задержку благодаря улучшенному делителю, который удаляет в среднем два бита за цикл. Прогнозирование ветвей было улучшено за счет увеличения 4096 записей с помощью 2-битного BHT.

21064A содержит 2,8 миллиона транзисторов, имеет размеры 14,5 на 10,5 мм и площадь 152,25 мм. 2 . Он был изготовлен компанией Digital по КМОП-процессу пятого поколения, CMOS-5, процессу 0,5 мкм с четырьмя уровнями алюминиевых межсоединений . [19]

Альфа 21066

[ редактировать ]Alpha 21066 , представленный как DECchip 21066 под кодовым названием LCA4 ( Low Cost Alpha ), представляет собой недорогой вариант Alpha 21064. Образцы были представлены 10 сентября 1993 года, а массовые поставки начались в начале 1994 года. , Alpha 21066 с частотой 166 МГц стоил 385 долларов США при партии 5000 штук. Также существовала модель на 100 МГц, предназначенная для встраиваемых систем . Отбор образцов начался в конце 1994 года, а объемные поставки начались в третьем квартале 1995 года. В отчете о микропроцессорах Alpha 21066 был признан первым микропроцессором со встроенным контроллером PCI.

Alpha 21066 предназначался для использования в недорогих приложениях, в частности в персональных компьютерах под управлением Windows NT . Компания Digital использовала различные модели Alpha 21066 в своих Multia клиентах , материнских платах AXPpci 33 производителя оригинального оборудования (OEM) и одноплатных компьютерах AXPvme . Помимо Digital, среди пользователей были Aspen Systems в своей рабочей станции Alpine, Carrera Computers в своей рабочей станции Pantera I, NekoTech использовала модель с частотой 166 МГц в своем персональном компьютере со скоростью 1–166 Маха и Parsys в своих суперкомпьютерах серии TransAlpha TA9000.

Благодаря сокращению процесса он смог включить в себя функции, которые были желательны для недорогих встроенных систем . Эти функции включают встроенный B-кэш и контроллер памяти с поддержкой ECC , функционально ограниченный графический ускоритель, поддерживающий до 8 МБ видеопамяти для реализации кадрового буфера , контроллер PCI и тактовый генератор с фазовой автоподстройкой частоты (PLL) для умножения. внешний тактовый сигнал частотой 33 МГц на желаемую внутреннюю тактовую частоту.

Контроллер памяти поддерживал от 64 КБ до 2 МБ B-кэша и от 2 до 512 МБ памяти. Реализация ECC была способна обнаруживать 1-, 2- и 4-битные ошибки и исправлять 1-битные ошибки. Для снижения стоимости Alpha 21066 имеет 64-битную системную шину, что позволило уменьшить количество контактов и, следовательно, размер корпуса. Уменьшенная ширина системной шины также снизила пропускную способность и, следовательно, производительность на 20%, что считалось приемлемым.

21066 содержал 1,75 миллиона транзисторов и имел размеры 17,0 на 12,3 мм при площади 209,1 мм. 2 . Он был изготовлен по технологии CMOS-4S (0,675 мкм) с тремя уровнями межсоединений. 21066 был упакован в 287-контактный CPGA размером 57,404 на 57,404 мм.

Альфа 21066А

[ редактировать ]

Alpha 21066A под кодовым названием LCA45 представляет собой недорогой вариант Alpha 21064A. Об этом было объявлено 14 ноября 1994 года, и в тот же день были представлены образцы моделей с частотой 100 и 233 МГц. Обе модели были отправлены в марте 1995 года. На момент анонса модели с частотой 100 и 233 МГц стоили 175 и 360 долларов США соответственно в количестве 5000 штук. Позже была доступна модель с частотой 266 МГц.

Модель 21066A была вторым производителем Mitsubishi Electric под названием M36066A . Это был первый микропроцессор Alpha, произведенный компанией. Детали на 100 и 233 МГц были анонсированы в ноябре 1994 года. На момент объявления инженерные образцы были установлены на декабрь 1994 года, коммерческие образцы - на июль 1995 года, а оптовые партии - на сентябрь 1995 года. Деталь на 233 МГц стоила 490 долларов США при партии по 1000 штук. . [20]

Хотя он был основан на 21064A, 21066A не имел кэша инструкций и данных размером 16 КБ. Особенностью 21066A было управление питанием: внутреннюю тактовую частоту микропроцессора можно было регулировать с помощью программного обеспечения.

Компания Digital использовала различные модели 21066A в своих продуктах, в которых ранее использовалась 21066. Помимо Digital, компания Tadpole Technology использовала модель 233 МГц в своем ноутбуке ALPHAbook 1 .

21066А содержал 1,8 миллиона транзисторов на кристалле размером 14,8 на 10,9 мм и площадью 161,32 мм. 2 . Он был изготовлен по КМОП-процессу пятого поколения Digital, CMOS-5, 0,5 мкм техпроцессу с тремя уровнями межсоединений. Компания Mitsubishi Electric изготовила M36066A по собственному трехуровневому металлическому процессу толщиной 0,5 мкм.

Альфа 21068

[ редактировать ]Alpha 21068 , представленный как DECchip 21068 , представляет собой версию 21066, предназначенную для встраиваемых систем. Он был идентичен 21066, но имел более низкую тактовую частоту для снижения рассеиваемой мощности и стоимости. Образцы были представлены 10 сентября 1993 года, а массовые поставки начались в начале 1994 года. Они работали на частоте 66 МГц и имели максимальную рассеиваемую мощность 9 Вт. На момент выпуска модель 21068 стоила 221 доллар США за штуку при партии 5000 экземпляров. 6 июня 1994 года компания Digital объявила о снижении цены на 16% до 186 долларов США с 3 июля 1994 года.

Alpha 21068 использовалась компанией Digital в материнской плате AXPpci 33 и одноплатных компьютерах AXPvme 64 и 64LC .

Альфа 21068А

[ редактировать ]Alpha 21068A , представленный как DECchip 21068A , представляет собой вариант Alpha 21066A для встраиваемых систем. Он работал на тактовой частоте 100 МГц.

Чипсеты

[ редактировать ]не было Изначально стандартного чипсета для 21064 и 21064А . В компьютерах Digital использовались специализированные интегральные схемы (ASIC) для взаимодействия микропроцессора с системой. Поскольку это увеличило стоимость разработки для третьих сторон, желающих разрабатывать продукты на базе Alpha, компания Digital разработала стандартный набор микросхем DECchip 21070 ( Apecs ) для производителей оригинального оборудования (OEM).

Существовали две модели 21070: DECchip 21071 и DECchip 21072 . Модель 21071 предназначалась для рабочих станций, а модель 21072 — для высокопроизводительных рабочих станций или недорогих однопроцессорных серверов. Две модели различались характеристиками подсистемы памяти: 21071 имеет 64-битную шину памяти и поддерживает от 8 МБ до 2 ГБ памяти с защитой по четности , тогда как 21072 имеет 128-битную шину памяти и поддерживает от 16 МБ до 4 ГБ ECC . защищенная память.

Чипсет состоял из трех микросхем: контроллера B-кэша и памяти COMANCHE , среза данных DECADE и контроллера EPIC PCI. Чипы DECADE реализовали пути данных в 32-битных срезах, поэтому у 21071 таких чипов два, а у 21072 — четыре. Чип EPIC имеет 32-битный путь к чипам DECADE.

Модель 21070 была представлена 10 января 1994 года. [21] с имеющимися образцами. Массовые поставки начались в середине 1994 года. В количестве 5000 экземпляров модель 21071 стоила 90 долларов, а модель 21072 — 120 долларов.

21 070 пользователей включали Carrera Computers для своих рабочих станций Pantera и Digital в некоторые модели AlphaStation и однопроцессорные AlphaServers .

См. также

[ редактировать ]- AlphaVM : полный эмулятор системы DEC Alpha , работающий в Windows или Linux. Он содержит высокопроизводительный эмулятор процессора Alpha.

Примечания

[ редактировать ]- ^ Чарльз П. Такер; Дэвид Дж. Конрой; Лоуренс К. Стюарт (1992). «Демонстрационный блок Alpha: высокопроизводительный мультипроцессор для разработки программного обеспечения и микросхем» (PDF) . Цифровой технический журнал . 4 (4).

- ^ Райан 1994

- ^ Digital Equipment Corporation 1996, с. 2-3–2-4

- ^ Digital Equipment Corporation 1996, с. 2-5

- ^ Jump up to: а б с Маклеллан 1993 , с. 42

- ^ Добберпуль 1992, с. 37

- ^ Jump up to: а б Добберпуль 1992, с. 36

- ^ Digital Equipment Corporation 1996, с. 2-6

- ^ Добберпуль 1992 , стр. 35–36

- ^ Jump up to: а б с Маклеллан 1993 , с. 43

- ^ Jump up to: а б с Добберпуль 1992, с. 38

- ↑ август 1994 г.

- ^ Маклеллан 1993 , с. 44

- ^ Jump up to: а б с д Добберпуль 1992, с. 35

- ^ Бхандаркар 1995, с. 2–4

- ^ Digital Equipment Corporation 1996, с. 8-3

- ^ Digital Equipment Corporation 1996, с. 8-2

- ^ Бхандаркар 1995, с. 2

- ^ Бхандаркар 1995 , с. 3

- ^ Краузе 1994 г.

- ^ Корпорация цифрового оборудования, 1994 г.

Ссылки

[ редактировать ]- Справочное руководство по аппаратному обеспечению микропроцессоров Alpha 21064 и 21064A , июнь 1996 г. Номер заказа: EC-Q92UC-TE. Корпорация цифрового оборудования.

- Апики, Стив; Грехан, Рик (март 1995 г.). «Самые быстрые рабочие станции NT» . Байт .

- Бхандаркар, Дилип. «Альфа-реализации». Архивировано 24 мая 2011 г. в Wayback Machine , Информационный бюллетень Технического комитета компьютерного общества IEEE по компьютерной архитектуре , декабрь 1995 г.

- Computergram International (25 февраля 1992 г.). «DEC раскрывает больше об Alpha и бросает вызов прецизионной архитектуре RISC Hewlett-Packard» . Обзор компьютерного бизнеса .

- Computergram International (26 февраля 1992 г.). «DEC описывает свой альфа-RISC, Кубота раскрывает свои планы» . Обзор компьютерного бизнеса .

- Computergram International (7 июня 1994 г.). «DEC снижает цены на чипы Alpha AXP почти на 31%» . Обзор компьютерного бизнеса .

- Computergram International (13 сентября 1993 г.). «DEC добавляет Alpha для персональных компьютеров и управления» . Обзор компьютерного бизнеса .

- Computergram International (11 января 1994 г.). «Ежегодная награда за чипы Microprocessor Report объявляет Motorola 88110 деталью, которая наименее вероятно...» . Обзор компьютерного бизнеса .

- Computergram International (11 ноября 1994 г.). «Mitsubishi Electric наконец-то готова представить свою первую альфу» . Обзор компьютерного бизнеса .

- Computergram International (25 ноября 1994 г.). «Первая альфа-версия Mitsubishi обеспечивает ту же функциональность, что и 21066A от DEC». Обзор компьютерного бизнеса .

- Корпорация цифрового оборудования (10 января 1994 г.). «Digital представляет наборы микросхем системной логики на базе PCI для микропроцессоров Alpha AXP 21064 и анонсирует первый в отрасли чип моста PCI-PCI» . Пресс-релиз.

- Добберпуль, Дэниел В., Витек, Ричард Т. и др. «64-битный КМОП-микропроцессор двойного назначения с частотой 200 МГц», Digital Tech Journal , том 4, номер 4, специальный выпуск 1992 г., стр. 35–50.

- Гвеннап, Линли (12 сентября 1994 г.). «Цифровые технологии лидируют с 21164», Отчет о микропроцессоре , том 8, номер 12.

- Краузе, Рейнхардт (13 сентября 1993 г.). «DEC представляет два встроенных накопителя Alpha со встроенным накопителем PCI» . Электронные новости .

- Краузе, Рейнхардт (18 октября 1993 г.). «DEC готовит Alpha 225/275 МГц». Электронные новости .

- Краузе, Рейнхардт (21 ноября 1994 г.). «Партнеры Альфа катят 233МГц 21066А». Электронные новости .

- МакКинни, Дина Л. и др. «DECchip 21066 компании Digital: первый экономичный чип Alpha AXP». Цифровой технический журнал , том 6, номер 1, зима 1994 г., стр. 66–77.

- Маклеллан, Эдвард (июнь 1993 г.). «Архитектура Alpha AXP и процессор 21064». IEEE микро . стр. 36–47.

- Райан, Боб; Томпсон, Том (январь 1994 г.). «РИСК взрослеет» . Байт .

Дальнейшее чтение

[ редактировать ]- «DEC вместе с Alpha выходит на рынок микропроцессоров». (4 марта 1992 г.). Отчет о микропроцессоре , Том 6, Номер 3.

- «Премьеры Альфа-архитектуры DEC». (4 марта 1992 г.). Отчет о микропроцессоре , Том 6, Номер 3.

- "Цифровые планы широкого семейства процессоров Alpha" (18 ноября 1992 г.). Отчет о микропроцессоре , Том 6, Номер 3.

- «Digital представляет наборы микросхем PCI для Alpha» . (12 июля 1993 г.). Отчет о микропроцессоре , Том 7, Номер 9.

- «Альфа достигает нижнего уровня с 21066 от Digital». (13 сентября 1993 г.). Отчет о микропроцессоре , Том 7, Номер 12.

- Бхандаркар, Дилип П. (1995). Альфа-архитектура и реализации . Цифровая пресса.

- Фокс, Томас Ф. (1994). «Проектирование высокопроизводительных микропроцессоров в Digital». Материалы 31-й ежегодной конференции ACM-IEEE по автоматизации проектирования . стр. 586–591.

- Гроновски, Пол Э. и др. (май 1998 г.). «Проектирование высокопроизводительного микропроцессора». Журнал IEEE твердотельных схем 33 (5): стр. 676–686.