Триггер (электроника)

В электронике , имеющие два стабильных состояния , триггеры и защелки — это схемы способные хранить информацию о состоянии — бистабильный мультивибратор . Схема может изменять состояние с помощью сигналов, подаваемых на один или несколько управляющих входов, и выводить свое состояние (часто вместе с его логическим дополнением ). Это основной элемент хранения в последовательной логике . Триггеры и защелки являются фундаментальными строительными блоками цифровых электронных систем, используемых в компьютерах, средствах связи и многих других типах систем.

Триггеры и защелки используются в качестве элементов хранения данных для хранения одного бита (двоичной цифры) данных; одно из двух его состояний представляет собой «единицу», а другое — «ноль». Такое хранилище данных можно использовать для хранения состояния , и такая схема описывается как последовательная логика в электронике. При использовании в конечном автомате выходное и следующее состояние зависят не только от текущего входного сигнала, но также от его текущего состояния (и, следовательно, от предыдущих входных данных). Его также можно использовать для подсчета импульсов и для синхронизации входных сигналов с переменной синхронизацией с некоторым опорным сигналом синхронизации.

Термин «триггер» исторически в целом относился как к схемам, запускаемым по уровню (асинхронным, прозрачным или непрозрачным), так и к схемам, запускаемым по фронту ( синхронным или тактовым ), которые хранят один бит данных с использованием вентилей . [1] Современные авторы оставляют термин «триггер» исключительно для элементов хранения, запускаемых по фронту, и защелки для элементов, запускаемых по уровню. [2] [3] Термины «запуск по фронту» и «запуск по уровню» могут использоваться во избежание двусмысленности. [4]

Когда включена защелка, запускаемая по уровню, она становится прозрачной, но выходной сигнал триггера, запускаемого по фронту, изменяется только по фронту тактового сигнала (либо положительный, либо отрицательный).

Различные типы триггеров и защелок доступны в виде интегральных схем , обычно с несколькими элементами на кристалл. Например, 74HC75 — это четырехстворчатая прозрачная защелка серии 7400 .

История

[ редактировать ]

Первая электронная защелка была изобретена в 1918 году британскими физиками Уильямом Экклсом и Ф.В. Джорданом . [5] [6] Первоначально она называлась триггерной схемой Эклса-Джордана и состояла из двух активных элементов ( вакуумных ламп ). [7] Эта конструкция использовалась в британском компьютере для взлома кодов Colossus 1943 года. [8] и такие схемы и их транзисторные версии были распространены в компьютерах даже после появления интегральных схем , хотя защелки и триггеры, сделанные из логических элементов, также распространены и сейчас. [9] [10] Ранние защелки были известны по-разному как триггерные схемы или мультивибраторы .

По словам П. Л. Линдли, инженера Лаборатории реактивного движения США , подробно описанные ниже типы триггеров (SR, D, T, JK) впервые обсуждались в 1954 году в курсе компьютерного проектирования Калифорнийского университета в Лос-Анджелесе Монтгомери Фистером, а затем появились в его книге книга Логическое проектирование цифровых компьютеров. [11] [12] Линдли в то время работал в Hughes Aircraft под руководством Элдреда Нельсона, который придумал термин JK для триггера, который менял состояния, когда оба входа были включены (логическая «единица»). Остальные имена были придуманы Фистером. Они немного отличаются от некоторых определений, приведенных ниже. Линдли объясняет, что он услышал историю о шлепанцах JK от Элдреда Нельсона, который придумал этот термин во время работы в Hughes Aircraft. В то время в Хьюзе использовались шлепанцы того типа, который стал известен как JK. При разработке логической системы Нельсон назначил буквы входам триггера следующим образом: № 1: A и B, № 2: C и D, № 3: E и F, № 4: G и H, № 5: J & К. Нельсон использовал обозначения « j -вход» и « k -вход» в патентной заявке, поданной в 1953 году. [13]

Выполнение

[ редактировать ]

Прозрачные или асинхронные защелки могут быть построены вокруг одной пары инвертирующих элементов с перекрестной связью: электронные лампы , биполярные транзисторы , полевые транзисторы , инверторы и инвертирующие логические элементы — все они использовались в практических схемах.

Тактируемые триггеры специально разработаны для синхронных систем; такие устройства игнорируют свои входы, за исключением перехода специального тактового сигнала (известного как тактовый, импульсный или стробирующий). Тактирование заставляет триггер либо изменять, либо сохранять свой выходной сигнал в зависимости от значений входных сигналов при переходе. Некоторые триггеры изменяют выходной сигнал по нарастающему фронту тактового сигнала, другие — по спадающему.

Поскольку элементарные усилительные каскады являются инвертирующими, два каскада можно соединить последовательно (каскадом), чтобы сформировать необходимый неинвертирующий усилитель. В этой конфигурации каждый усилитель можно рассматривать как активную инвертирующую цепь обратной связи для другого инвертирующего усилителя. Таким образом, два каскада соединяются в неинвертирующий контур, хотя принципиальная схема обычно изображается как симметричная перекрестно-связанная пара (оба рисунка изначально представлены в патенте Экклса-Джордана).

Типы

[ редактировать ]Триггеры и защелки можно разделить на распространенные типы: SR («установка-сброс»), D («данные»), T («переключатель») и JK (см. раздел «История» выше). Поведение определенного типа может быть описано характеристическим уравнением, которое выводит «следующий» выходной сигнал ( Q next ) через входной сигнал(ы) и/или текущий выходной сигнал. .

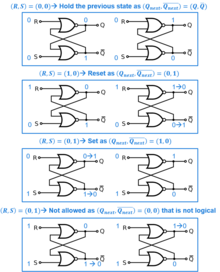

Асинхронные защелки установки-сброса

[ редактировать ]При использовании статических вентилей в качестве строительных блоков наиболее фундаментальной защелкой является асинхронная защелка Set-Reset (SR) .

Два его входа S и R могут устанавливать внутреннее состояние на 1, используя комбинацию S=1 и R=0, и могут сбрасывать внутреннее состояние на 0, используя комбинацию S=0 и R=1. [примечание 1]

Защелка SR может быть построена из пары NOR или NAND логических элементов с перекрестной связью . Сохраненный бит присутствует на выходе, отмеченном Q.

Удобно думать о NAND, NOR, AND и OR как об управляемых операциях, где один вход выбирается в качестве набора управляющих входов, а другой бит — в качестве входного сигнала, который будет обработан в зависимости от состояния элемента управления. Затем все эти элементы имеют одно управляющее значение, которое игнорирует входной сигнал (x) и выводит постоянное значение, в то время как другое управляющее значение пропускает входной сигнал (возможно, дополненный):

По сути, все они могут использоваться в качестве переключателей, которые либо устанавливают определенное значение, либо пропускают входное значение.

Защелка SR NOR

[ редактировать ]

- S = 1, R = 0: Установить

- S = 0, R = 0: Удерживать

- S = 0, R = 1: Сброс

- S = 1, R = 1: Не разрешено

Защелка SR NOR состоит из двух параллельных вентилей NOR, где выход каждого NOR также распределяется на один вход другого NOR, как показано на рисунке.Мы называем обратной связи входами или просто обратными связями эти соединения выхода со входом.Остальные входы мы будем использовать в качестве входов управления, как описано выше.Обратите внимание: на этом этапе, поскольку все симметрично, не имеет значения, к каким входам подключены выходы.Теперь мы нарушаем симметрию, выбирая, какой из оставшихся управляющих входов будет для нас установлен и сброшен, и мы можем вызвать «установить НЕ-ИЛИ» вентиль ИЛИ-НЕ с помощью элемента управления установкой и «сбросить НЕ-ИЛИ» с помощью элемента управления сбросом; на рисунках установленное NOR — нижнее, а сбросное NOR — верхнее.Выходом сброса NOR будет наш сохраненный бит Q, при этом мы увидим, что выход набора NOR сохраняет свое Q. дополнение

Чтобы определить поведение защелки SR NOR, рассмотрите S и R как управляющие входы и помните, что из приведенных выше уравнений установка и сброс NOR с элементом управления 1 фиксирует их выходы на 0, а установка и сброс NOR с элементом управления 0 будет действовать. как ворота НЕ.Благодаря этому теперь можно определить поведение фиксации SR как простые условия (вместо того, чтобы, например, присваивать значения каждой строке, посмотрите, как они распространяются):

- Хотя R и S оба равны нулю, и R NOR, и S NOR просто налагают обратную связь, являющуюся дополнением выходного сигнала, и это выполняется до тех пор, пока выходные данные дополняют друг друга. Таким образом, выходы Q и Q поддерживаются в постоянном состоянии, независимо от того, Q=0 или Q=1.

- Если S=1, а R=0, то установленное NOR зафиксирует Q =0, а сбросное NOR адаптируется и установит Q=1. Как только S устанавливается обратно на ноль, значения сохраняются, как описано выше.

- Аналогично, если R=1 при S=0, то сброс NOR фиксирует Q=0, в то время как установка NOR с адаптацией Q =1. И снова состояние сохраняется, если R снова установлен на 0.

- Если R=S=1, NOR фиксирует оба выхода на 0, что не является допустимым состоянием для хранения дополнительных значений.

Операция фиксации SR [4] Таблица характеристик Стол возбуждения С Р Вопрос следующий Действие вопрос Вопрос следующий С Р 0 0 вопрос Удержание состояния 0 0 0 Х 0 1 0 Перезагрузить 0 1 1 0 1 0 1 Набор 1 0 0 1 1 1 Х Не разрешено 1 1 Х 0

Примечание. X означает «все равно» , то есть допустимым значением является либо 0, либо 1.

Комбинация R = S = 1 называется ограниченной комбинацией или запрещенным состоянием , поскольку, поскольку оба вентиля ИЛИ затем выводят нули, это нарушает логическое уравнение Q = not Q . Такая комбинация также не подходит в схемах, где оба входа могут перейти в низкий уровень одновременно (т.е. происходит переход от ограничения к удержанию ). Выход может оставаться в метастабильном состоянии и в конечном итоге может зафиксироваться либо на 1, либо на 0 в зависимости от соотношения времени распространения между вентилями ( состояние гонки ).

Чтобы преодолеть ограниченную комбинацию, можно добавить к входам элементы, которые будут преобразовывать (S, R) = (1, 1) к одной из неограниченных комбинаций. Это может быть:

- Q = 1 (1, 0) – называется S (доминируемой)-защелкой

- Q = 0 (0, 1) – называется R (доминируемой)-защелкой

Это делается почти в каждом программируемом логическом контроллере .

- Состояние удержания (0, 0) – называется электронной защелкой.

В качестве альтернативы можно создать ограниченную комбинацию для переключения вывода. В результате получается защелка JK .

Характеристическое уравнение защелки SR:

- или [14]

где A + B означает (A или B), AB означает (A и B)

Другое выражение:

- с [15]

SR NAND Защелка

[ редактировать ]

Схема, показанная ниже, представляет собой базовую защелку NAND. Входы также обычно обозначаются S и R для установки и сброса соответственно. Поскольку входы И-НЕ обычно должны иметь логическую 1, чтобы не влиять на действие фиксации, входы в этой схеме считаются инвертированными (или активными с низким уровнем).

Схема использует ту же обратную связь, что и SR NOR, просто заменяя элементы NOR на элементы NAND, чтобы «запомнить» и сохранить свое логическое состояние даже после изменения управляющих входных сигналов.Опять же, вспомните, что И-НЕ, управляемое 1, всегда выводит 0, тогда как И-НЕ, управляемое 0, действует как вентиль НЕ.Когда на входах S и R высокий уровень, обратная связь поддерживает выходы Q в предыдущем состоянии.Когда один из них равен нулю, они фиксируют свои выходные биты на 0, а остальные адаптируются к дополнению.S=R=0 создает недопустимое состояние.

|  |

Защелка SR И-ИЛИ

[ редактировать ]

С точки зрения обучения, защелки SR, нарисованные как пара компонентов с перекрестной связью (транзисторы, затворы, лампы и т. д.), часто сложны для понимания новичкам. Дидактически более простое объяснение — изобразить защелку как единую петлю обратной связи, а не как перекрестную связь. Ниже приведена защелка SR, построенная на основе логического элемента И с одним инвертированным входом и логического элемента ИЛИ . Обратите внимание, что инвертор необходим не для функции фиксации, а для того, чтобы сделать оба входа активными.

Операция фиксации SR И-ИЛИ С Р Действие 0 0 Никаких изменений; случайный начальный 1 0 К = 1 Х 1 К = 0

Обратите внимание, что защелка SR AND-OR имеет то преимущество, что S = 1, R = 1 четко определены. В приведенной выше версии защелки SR AND-OR приоритет отдается сигналу R над сигналом S. Если необходим приоритет S над R, этого можно добиться, подключив выход Q к выходу логического элемента ИЛИ вместо выхода логического элемента И.

Защелку SR AND-OR легче понять, поскольку оба вентиля можно объяснить изолированно, опять же с точки зрения управления AND и OR сверху. Когда ни S, ни R не установлены, то и логический элемент ИЛИ, и логический элемент И находятся в «режиме удержания», т. е. они пропускают входной сигнал, их выходной сигнал является входным сигналом из контура обратной связи. Когда вход S = 1, логический элемент ИЛИ выдает 1 независимо от другого входа контура обратной связи («режим установки»). Когда вход R = 1, логический элемент И выдает 0, независимо от другого входа контура обратной связи («режим сброса»). А поскольку вентиль И принимает выходной сигнал вентиля ИЛИ в качестве входных данных, R имеет приоритет над S. Защелки, нарисованные как перекрестно связанные вентили, могут выглядеть менее интуитивно понятными, поскольку поведение одного вентиля кажется переплетенным с поведением другого вентиля. Стандартные защелки NOR или NAND также могут быть перерисованы с помощью контура обратной связи, но в их случае контур обратной связи не показывает одно и то же значение сигнала на протяжении всего контура обратной связи. Однако защелка SR AND-OR имеет тот недостаток, что для получения инвертированного Q-выхода потребуется дополнительный инвертор.

Обратите внимание, что защелка SR И-ИЛИ может быть преобразована в защелку SR NOR с помощью логических преобразований: инвертирования выхода логического элемента ИЛИ, а также второго входа логического элемента И и подключения инвертированного выхода Q между этими двумя добавленными инверторами; причем вентиль И с обоими инвертированными входами эквивалентен вентилю ИЛИ-НЕ в соответствии с законами Де Моргана .

JK-защелка

[ редактировать ]Защелка JK используется гораздо реже, чем триггер JK. Защелка JK соответствует следующей таблице состояний:

Таблица истинности JK-защелки Дж К Вопрос следующий Комментарий 0 0 вопрос Без изменений 0 1 0 Перезагрузить 1 0 1 Набор 1 1 вопрос Переключать

Следовательно, защелка JK представляет собой защелку SR, которая предназначена для переключения ее выхода (колебания между 0 и 1) при передаче входной комбинации 11. [16] В отличие от триггера JK, комбинация из 11 входов для защелки JK не очень полезна, поскольку нет тактового сигнала, управляющего переключением. [17]

Закрытые задвижки и условная прозрачность

[ редактировать ]Защелки спроектированы прозрачными. То есть изменения входного сигнала вызывают немедленные изменения выходного сигнала. К прозрачной защелке можно добавить дополнительную логику, чтобы сделать ее непрозрачной или непрозрачной, когда другой вход («включающий» вход) не подтвержден. Когда несколько прозрачных защелок следуют друг за другом, если они все прозрачны одновременно, сигналы будут распространяться через них всех. Однако следование за с прозрачным высоким уровнем защелкой защелкой с прозрачным низким уровнем (или наоборот) приводит к тому, что состояние и выход изменяются только на фронтах тактового сигнала, образуя так называемый триггер «главный-подчиненный» .

Запираемая защелка SR

[ редактировать ]

Запираемую защелку SR можно создать, добавив второй уровень вентилей И-НЕ к инвертированной защелке SR . Дополнительные логические элементы И-НЕ дополнительно инвертируют входы, так что SR защелка становится закрытой защелкой SR ( защелка SR преобразуется в закрытую SR защелку с инвертированным разрешением).

Альтернативно, вентильную защелку SR (с неинвертирующим разрешением) можно создать путем добавления второго уровня логических элементов И к защелке SR .

При высоком уровне E ( enable true) сигналы могут проходить через входные вентили к инкапсулированной защелке; все комбинации сигналов, кроме (0, 0) = удержание , то сразу воспроизводятся на выходе (Q, Q ), т.е. защелка прозрачна .

При низком уровне E ( enable false) защелка закрывается (непрозрачна) и остается в том состоянии, в котором она находилась в последний раз, когда E был высоким.

Периодический входной сигнал разрешения можно назвать стробом записи . Когда вход разрешения представляет собой тактовый сигнал , говорят, что защелка чувствительна к уровню (к уровню тактового сигнала), в отличие от чувствительной к фронту, как триггеры ниже.

|  |

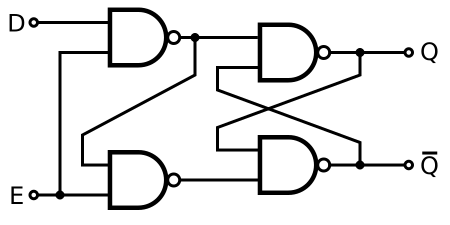

Запираемая D-защелка

[ редактировать ]Эта защелка использует тот факт, что в двух активных входных комбинациях (01 и 10) закрытой защелки SR R является дополнением S. Входной каскад NAND преобразует два входных состояния D (0 и 1) в эти два входных состояния. комбинации для следующей фиксации SR путем инвертирования входного сигнала данных. Низкое состояние разрешающего сигнала создает неактивную комбинацию «11». Таким образом, вентильную D-защелку можно рассматривать как синхронную SR-защелку с одним входом . Эта конфигурация предотвращает применение ограниченной комбинации входов. Он также известен как прозрачная защелка , защелка данных или просто закрытая защелка . Он имеет вход данных и сигнал включения (иногда называемый тактовым сигналом или контролем ). Слово «прозрачный» происходит от того факта, что, когда вход разрешения включен, сигнал распространяется непосредственно через схему, от входа D к выходу Q. Стробируемые D-защелки также чувствительны к уровню по отношению к уровню тактового сигнала. или включить сигнал.

Прозрачные защелки обычно используются в качестве портов ввода-вывода или в асинхронных системах, или в синхронных двухфазных системах ( синхронных системах , использующих двухфазный тактовый сигнал ), где две защелки, работающие на разных фазах тактового сигнала, предотвращают прозрачность данных, как в мастер-системе. рабский шлепанец.

Таблица истинности ниже показывает, что когда вход включения / блокировки равен 0, вход D не оказывает никакого влияния на выход. Когда E/C высокий, выходной сигнал равен D.

|  |

- Запираемая D-защелка на основе защелки SR NAND.

- Запираемая D-защелка на основе защелки SR NOR.

- Анимированная D-защелка. Черный и белый означают логические «1» и «0» соответственно.

- D = 1, E = 1: установить

- D = 1, E = 0: удерживать

- D = 0, E = 0: удерживать

- D = 0, E = 1: сброс

- Запираемая D-защелка в проходной транзисторной логике , аналогичная той, что используется в интегральных схемах CD4042 или CD74HC75.

Эрл защелка

[ редактировать ]Классические конструкции задвижек имеют некоторые нежелательные характеристики. [18] Для них требуется двухрельсовая логика или инвертор. Распространение сигнала от входа к выходу может занять до трех задержек. Распространение сигнала от входа к выходу не является постоянным: на некоторых выходах требуется две задержки, а на других — три.

Дизайнеры искали альтернативу. [19] Удачной альтернативой является защелка Earle. Для него требуется только один ввод данных, а на выходе требуется постоянная задержка в два вентиля. Кроме того, два уровня затвора защелки Эрла в некоторых случаях могут быть объединены с двумя последними уровнями затвора схем, управляющих защелкой, поскольку многие распространенные вычислительные схемы имеют уровень ИЛИ, за которым следует слой И в качестве последних двух уровней. . Объединение функции защелки может реализовать защелку без дополнительных задержек на воротах. [18] Слияние обычно используется при проектировании конвейерных компьютеров и фактически было первоначально разработано Джоном Г. Эрлом для использования в IBM System/360 Model 91 для этой цели. [20]

Защелка Earle безопасна. [21] Если средний вентиль И-НЕ опущен, то получается защелка удержания полярности , которая обычно используется, поскольку требует меньше логики. [21] [22] Однако он подвержен логической опасности . Преднамеренное искажение тактового сигнала позволяет избежать опасности. [22]

- Защелка Earle использует дополнительные входы включения: включение активного низкого уровня (E_L) и включение активного высокого уровня (E_H).

- Анимированная защелка Эрла. Черный и белый означают логические «1» и «0» соответственно.

- D = 1, E_H = 1: установить

- D = 0, E_H = 1: сброс

- D = 1, E_H = 0: удерживать

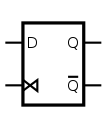

D-триггер

[ редактировать ]

D-триггер широко используется и известен как триггер «данных». D-триггер фиксирует значение D-входа в определенную часть тактового цикла (например, нарастающий фронт тактового сигнала). Это захваченное значение становится выходом Q. В других случаях выходной сигнал Q не меняется. [23] [24] D-триггер можно рассматривать как ячейку памяти, удержание нулевого порядка или линию задержки . [25]

Таблица истинности:

Часы Д Вопрос следующий Восходящий край 0 0 Восходящий край 1 1 Невосходящий Х вопрос

( X обозначает состояние безразличия , то есть сигнал не имеет значения)

Большинство триггеров D-типа в микросхемах имеют возможность принудительного перевода в состояние установки или сброса (при этом игнорируются входы D и тактовый сигнал), что очень похоже на триггер SR. Обычно недопустимое условие S = R = 1 разрешается в триггерах D-типа. Установка S = R = 0 заставляет триггер вести себя, как описано выше. Вот таблица истинности для других возможных конфигураций S и R:

Входы Выходы С Р Д > вопрос вопрос 0 1 Х Х 0 1 1 0 Х Х 1 0 1 1 Х Х 1 1

Эти триггеры очень полезны, поскольку они составляют основу сдвиговых регистров , которые являются неотъемлемой частью многих электронных устройств. Преимущество триггера D перед «прозрачной защелкой» типа D заключается в том, что сигнал на входном выводе D захватывается в момент тактирования триггера, и последующие изменения на входе D будут игнорироваться до следующего событие часов. Исключением является то, что некоторые триггеры имеют входной сигнал «сброса», который сбрасывает Q (в ноль) и может быть асинхронным или синхронным с тактовой частотой.

Приведенная выше схема сдвигает содержимое регистра вправо на одну битовую позицию при каждом активном переходе тактового сигнала. Вход X сдвигается в крайнюю левую битовую позицию.

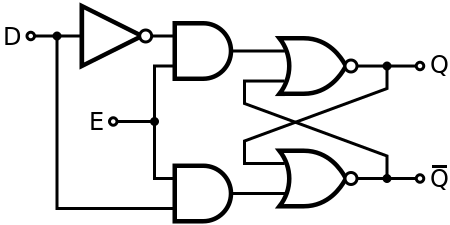

Классический D-триггер, запускаемый положительным фронтом

[ редактировать ]Эта схема [26] состоит из двух этапов, реализованных защелками SR NAND . Входной каскад (две защелки слева) обрабатывает сигналы синхронизации и данных, чтобы обеспечить правильные входные сигналы для выходного каскада (одна защелка справа). Если тактовый сигнал низкий, оба выходных сигнала входного каскада имеют высокий уровень независимо от входных данных; выходная защелка не затрагивается и сохраняет предыдущее состояние. Когда тактовый сигнал меняется с низкого на высокий, только одно из выходных напряжений (в зависимости от сигнала данных) становится низким и устанавливает/сбрасывает выходную защелку: если D = 0, нижний выход становится низким; если D = 1, верхний выход становится низким. Если тактовый сигнал продолжает оставаться высоким, выходы сохраняют свое состояние независимо от входных данных и заставляют защелку выхода оставаться в соответствующем состоянии, поскольку входной логический ноль (выходного каскада) остается активным, пока тактовый сигнал высокий. Следовательно, роль выходной защелки заключается в сохранении данных только при низком тактовом сигнале.

Схема тесно связана с вентилируемой D-защелкой , поскольку обе схемы преобразуют два состояния входа D (0 и 1) в две входные комбинации (01 и 10) для выходной защелки SR путем инвертирования входного сигнала данных (обе схемы разделяют одиночный сигнал D в двух дополнительных сигналах S и R ). Разница в том, что логические элементы И-НЕ используются в закрытой D-защелке, а защелки SR -И-НЕ используются в D-триггере, запускаемом по положительному фронту. Роль этих защелок состоит в том, чтобы «заблокировать» активный выход, создающий низкое напряжение (логический ноль); таким образом, D-триггер, запускаемый по положительному фронту, также можно рассматривать как закрытую D-защелку с защелкивающимися входными вентилями.

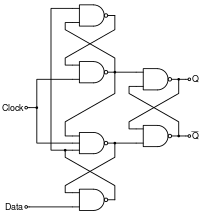

D-триггер с запуском по фронту ведущий-ведомый

[ редактировать ]

D-триггер «главный-подчиненный» создается путем соединения двух вентильных D-защелок последовательного и инвертирования разрешающего входа на один из них. Он называется главным-ведомым, потому что главная защелка контролирует выходное значение Q подчиненной защелки и заставляет подчиненную защелку удерживать свое значение всякий раз, когда включена подчиненная защелка, поскольку подчиненная защелка всегда копирует свое новое значение из главной защелки и меняет свое значение. только в ответ на изменение значения главной защелки и тактового сигнала.

Для D-триггера «главный-подчиненный», запускаемого по положительному фронту, когда тактовый сигнал низкий (логический 0), «разрешение», видимое первой или «главной» D-защелкой (инвертированный тактовый сигнал), имеет высокий уровень (логическая 1). . Это позволяет «главной» защелке сохранять входное значение, когда тактовый сигнал переходит от низкого к высокому. Когда тактовый сигнал становится высоким (от 0 до 1), инвертированное «разрешение» первой защелки становится низким (от 1 до 0), и значение, видимое на входе в главную защелку, «фиксируется». Почти одновременно дважды инвертированное «разрешение» второй или «ведомой» защелки D переходит с низкого уровня на высокий (0 на 1) вместе с тактовым сигналом. Это позволяет сигналу, захваченному на нарастающем фронте тактового сигнала теперь «заблокированной» главной защелкой, проходить через «ведомую» защелку. Когда тактовый сигнал возвращается в низкий уровень (от 1 до 0), выход «ведомой» защелки «блокируется», и значение, наблюдаемое на последнем нарастающем фронте тактового сигнала, удерживается, пока «главная» защелка начинает принимать новые значения в рамках подготовки к следующему нарастающему фронту тактовой частоты.

Удаление крайнего левого инвертора в схеме создает триггер D-типа, который стробирует по заднему фронту тактового сигнала. Это имеет следующую таблицу истинности:

Д вопрос > Вопрос следующий 0 Х Падение 0 1 Х Падение 1

D-триггер с двойным фронтом

[ редактировать ]

Триггеры, которые считывают новое значение по нарастающему и заднему фронту тактового сигнала, называются триггерами с двойным фронтом. Такой триггер может быть построен с использованием двух триггеров D-типа с однопереходным запуском и мультиплексора или с использованием двух триггеров D-типа с однопереходным запуском и трех вентилей исключающее ИЛИ.

Динамический элемент хранения D, запускаемый по фронту

[ редактировать ]

Эффективную функциональную альтернативу D-триггеру можно создать с помощью динамических схем (где информация хранится в емкости) при условии, что они тактируются достаточно часто; хотя это и не настоящий триггер, его все же называют триггером из-за его функциональной роли. Хотя элемент D «главный-подчиненный» запускается по фронту тактового сигнала, каждый из его компонентов запускается по уровням тактового сигнала. «D-триггер, запускаемый по фронту», как его называют, хотя он и не является настоящим триггером, не имеет свойств «ведущий-подчиненный».

D-триггеры, запускаемые по фронту, часто реализуются в интегрированных высокоскоростных операциях с использованием динамической логики . Это означает, что цифровой выходной сигнал сохраняется в паразитной емкости устройства, пока устройство не переходит в режим перехода. Эта конструкция обеспечивает сброс путем простого разряда одного или нескольких внутренних узлов. Распространенной разновидностью динамического триггера является тип настоящих однофазных часов (TSPC), который выполняет операцию триггера с небольшим энергопотреблением и на высоких скоростях. Однако динамические триггеры обычно не работают на статических или низких тактовых частотах: по прошествии достаточного времени пути утечки могут разрядить паразитную емкость настолько, что триггер перейдет в недопустимые состояния.

Т-триггер

[ редактировать ]

Если на входе T высокий уровень, T-триггер меняет состояние («переключается») всякий раз, когда тактовый вход срабатывает. Если на входе T низкий уровень, триггер сохраняет предыдущее значение. Такое поведение описывается характеристическим уравнением :

- (расширение оператора XOR )

и может быть описан в таблице истинности :

Т-триггер [27] Таблица характеристик Стол возбуждения Комментарий Комментарий 0 0 0 Состояние удержания (без часов) 0 0 0 Без изменений 0 1 1 Состояние удержания (без часов) 1 1 0 Без изменений 1 0 1 Переключать 0 1 1 Дополнить 1 1 0 Переключать 1 0 1 Дополнить

Когда T удерживается на высоком уровне, тумблер-триггер делит тактовую частоту на два; то есть, если тактовая частота равна 4 МГц, выходная частота, полученная от триггера, будет равна 2 МГц. Эта функция «разделения на» применяется в различных типах цифровых счетчиков . AT-триггер также может быть построен с использованием триггера JK (выводы J и K соединены вместе и действуют как T) или D-триггера (вход T XOR Q, предыдущий, управляет входом D).

JK шлепанцы

[ редактировать ]

Триггер JK дополняет поведение триггера SR (J: Set, K: Reset), интерпретируя условие J = K = 1 как команду «переворота» или переключения. В частности, комбинация J = 1, K = 0 представляет собой команду установки триггера; комбинация J=0, K=1 – команда сброса триггера; а комбинация J = K = 1 представляет собой команду переключения триггера, т. е. изменения его выхода на логическое дополнение его текущего значения. Установка J = K = 0 сохраняет текущее состояние. Чтобы синтезировать D-триггер, просто установите K равным дополнению J (вход J будет действовать как вход D). Аналогично, чтобы синтезировать T-триггер, установите K равным J. Таким образом, JK-триггер является универсальным триггером, поскольку его можно настроить для работы как SR-триггер, D-триггер или Т-триггер.

Характеристическое уравнение триггера JK:

и соответствующая таблица истинности:

JK-триггер [27] Таблица характеристик Стол возбуждения Дж К Комментарий Вопрос следующий вопрос Вопрос следующий Комментарий Дж К 0 0 Удержание состояния вопрос 0 0 Без изменений 0 Х 0 1 Перезагрузить 0 0 1 Набор 1 Х 1 0 Набор 1 1 0 Перезагрузить Х 1 1 1 Переключать вопрос 1 1 Без изменений Х 0

Вопросы выбора времени

[ редактировать ]Параметры времени

[ редактировать ]

Входной сигнал должен оставаться стабильным в течение периода вокруг нарастающего фронта тактового сигнала, известного как апертура. Представьте себе, что вы фотографируете лягушку на кувшинке. [28] Предположим, что лягушка затем прыгнула в воду. Если вы сфотографируете лягушку, прыгающую в воду, вы получите размытое изображение лягушки, прыгающей в воду — неясно, в каком состоянии находилась лягушка. Но если вы сфотографируете, когда лягушка устойчиво сидит на площадке (или устойчиво в воде) вы получите четкое изображение. Точно так же входной сигнал на триггер должен оставаться устойчивым во время открытия триггера.

Время настройки — это минимальное время, в течение которого входные данные должны оставаться стабильными перед событием часов, чтобы данные надежно считывались часами.

Время удержания — это минимальное время, в течение которого ввод данных должен оставаться стабильным после события часов, чтобы данные надежно считывались часами.

Диафрагма — это сумма времени установки и удержания. Ввод данных должен оставаться стабильным в течение этого периода времени. [28]

Время восстановления — это минимальное время, в течение которого асинхронный вход установки или сброса должен быть неактивен перед событием часов, чтобы данные надежно считывались часами. Таким образом, время восстановления для асинхронного входа установки или сброса аналогично времени настройки для входа данных.

Время удаления — это минимальное время, в течение которого асинхронный вход установки или сброса должен быть неактивен после события часов, чтобы данные надежно считывались часами. Таким образом, время удаления асинхронного входа установки или сброса аналогично времени удержания ввода данных.

Короткие импульсы, подаваемые на асинхронные входы (установка, сброс), не должны подаваться полностью в течение периода восстановления-снятия, иначе становится совершенно невозможно определить, перейдет ли триггер в соответствующее состояние. В другом случае, когда асинхронный сигнал просто совершает один переход, который приходится на время восстановления/удаления, в конечном итоге триггер перейдет в соответствующее состояние, но на выходе может появиться или не появиться очень короткий сбой, в зависимости от на синхронном входном сигнале. Эта вторая ситуация может иметь или не иметь значение для схемотехники.

Сигналы установки и сброса (и другие) могут быть синхронными или асинхронными и, следовательно, могут характеризоваться временем установки/удержания или восстановления/удаления, а синхронность очень зависит от конструкции триггера.

Различие между временем установки/удержания и восстановления/удаления часто необходимо при проверке синхронизации более крупных цепей, поскольку асинхронные сигналы могут оказаться менее критичными, чем синхронные сигналы. Эта дифференциация дает разработчикам схем возможность независимо определять условия проверки для этих типов сигналов.

Метастабильность

[ редактировать ]Триггеры подвержены проблеме, называемой метастабильностью , которая может возникнуть, когда два входа, такие как данные и часы или часы и сброс, изменяются примерно в одно и то же время. Когда порядок не ясен, в пределах соответствующих временных ограничений, в результате выходной сигнал может вести себя непредсказуемо, переход в одно или другое состояние занимает во много раз больше времени, чем обычно, или даже несколько раз колеблется перед стабилизацией. Теоретически время успокоения не ограничено. В компьютерной системе эта метастабильность может вызвать повреждение данных или сбой программы, если состояние не является стабильным до того, как другая схема использует его значение; в частности, если два разных логических пути используют выходные данные триггера, один путь может интерпретировать его как 0, а другой как 1, когда он не переходит в стабильное состояние, переводя машину в несогласованное состояние. [29]

Метастабильности в триггерах можно избежать, гарантируя, что входные данные и управляющие входы остаются действительными и постоянными в течение определенных периодов до и после тактового импульса, называемых временем установки (t su ) и временем удержания ( th ) соответственно. Это время указано в технических характеристиках устройства и обычно составляет от нескольких наносекунд до нескольких сотен пикосекунд для современных устройств. В зависимости от внутренней организации триггера можно создать устройство с нулевым (или даже отрицательным) требованием к настройке или времени удержания, но не с тем и другим одновременно.

К сожалению, не всегда возможно удовлетворить критериям установки и удержания, поскольку триггер может быть подключен к сигналу реального времени, который может измениться в любой момент вне контроля разработчика. В этом случае лучшее, что может сделать проектировщик, — это снизить вероятность ошибки до определенного уровня, зависящего от требуемой надежности схемы. Одним из методов подавления метастабильности является соединение двух или более триггеров в цепочку так, чтобы выход каждого из них подавал входные данные следующего, и все устройства использовали общий тактовый сигнал. С помощью этого метода вероятность метастабильного события можно снизить до незначительной величины, но никогда до нуля. Вероятность метастабильности становится все ближе и ближе к нулю по мере увеличения количества триггеров, соединенных последовательно. Количество каскадируемых триггеров называется «рейтингом»; «Двухранговые» шлепанцы (два шлепанца последовательно) — обычная ситуация.

Доступны так называемые триггеры с метастабильной закалкой, которые максимально сокращают время установки и удержания, но даже они не могут полностью устранить проблему. Это связано с тем, что метастабильность — это больше, чем просто вопрос конструкции схемы. Когда переходы в часах и данных близки по времени, триггер вынужден решать, какое событие произошло первым. Каким бы быстрым ни было устройство, всегда существует вероятность того, что входные события окажутся настолько близко друг к другу, что невозможно будет определить, какое из них произошло первым. Поэтому логически невозможно построить триггер с идеальной метастабильностью. Триггеры иногда характеризуются максимальным временем стабилизации (максимальное время, в течение которого они будут оставаться метастабильными при определенных условиях). В этом случае двухранговые триггеры, которые тактируются медленнее максимально допустимого времени метастабильности, обеспечат надлежащее согласование асинхронных (например, внешних) сигналов.

Задержка распространения

[ редактировать ]Еще одним важным значением времени для триггера является задержка тактового сигнала до выхода (общий символ в таблицах данных: t CO ) или задержка распространения (t P ), которая представляет собой время, необходимое триггеру для изменения своего выходного сигнала после край часов. Время перехода от высокого к низкому (t PHL ) иногда отличается от времени перехода от низкого к высокому (t PLH ).

При каскадном соединении триггеров, которые используют одни и те же часы (как в сдвиговом регистре ), важно гарантировать, что t CO предыдущего триггера больше, чем время удержания (th h ) следующего триггера. таким образом, данные, присутствующие на входе последующего триггера, правильно «смещаются» после активного фронта тактового сигнала. Эта связь между t CO и th обычно гарантируется, если триггеры физически идентичны. Более того, для корректной работы легко проверить, что период такта должен быть больше суммы t su + th h .

Обобщения

[ редактировать ]Триггеры можно обобщить как минимум двумя способами: сделав их 1 из N вместо 1 из 2 и адаптировав их к логике с более чем двумя состояниями. В особых случаях кодирования 1 из 3 или многозначной троичной логики такой элемент может называться триггером . [30]

В обычном триггере ровно один из двух дополнительных выходов имеет высокий уровень. Это можно обобщить на элемент памяти с N выходами, ровно один из которых имеет высокий уровень (альтернативно, когда ровно один из N имеет низкий уровень). Таким образом, выходные данные всегда представляют собой одно-горячее (соответственно одно-холодное ) представление. Конструкция аналогична обычному триггеру с перекрестной связью; каждый выход, когда он высокий, блокирует все остальные выходы. [31] В качестве альтернативы можно использовать более или менее традиционные триггеры, по одному на каждый выход, с дополнительной схемой, обеспечивающей работу только одного за раз. [32]

Еще одно обобщение обычного триггера — элемент памяти для многозначной логики . В этом случае элемент памяти сохраняет ровно одно из логических состояний до тех пор, пока управляющие входы не вызовут изменение. [33] Кроме того, можно использовать многозначные часы, что приводит к новым возможным переходам часов. [34]

Примечания

[ редактировать ]- ^ В качестве альтернативы два входа можно назвать набором 1 и набором 0, что может устранить путаницу для некоторых: термин «набор» сам по себе может быть неправильно понят как установка бита на вход, предназначенный для установки. Это наименование также делает интуитивно понятным в приведенном ниже объяснении, что попытка одновременно установить 0 и 1 должна привести к непредсказуемому поведению защелки SR.

См. также

[ редактировать ]- Реле с блокировкой

- Импульсный переходной детектор

- Выборка и хранение

- Триггер Шмитта

- Статическая оперативная память

Ссылки

[ редактировать ]- ^ Например, в издании 1969 года Logic Handfbook Flip Chip™ Modules компании Digital Equipment Corporation прозрачные защелки RS называются «триггерами R/S» ( http://www.bitsavers.org/pdf/dec/handbooks/Digital_Logic_Handbook_1969.pdf страница ). 44)

- ^ Педрони, Волней А. (2008). Цифровая электроника и дизайн с использованием VHDL . Морган Кауфманн. п. 329. ИСБН 978-0-12-374270-4 .

- ^ Защелки и шлепанцы (EE 42/100, лекция 24 из Беркли) «... Иногда термины «триггер» и «защелка» используются как синонимы...»

- ^ Jump up to: а б Рот, Чарльз Х. младший (1995). «Защелки и шлепанцы». Основы логического проектирования (4-е изд.). ПВС. ISBN 9780534954727 .

- ^ GB 148582 , Экклс, Уильям Генри и Джордан, Фрэнк Уилфред, «Усовершенствования в ионных реле», опубликовано 5 августа 1920 г.

- ^ См.:

- Экклс, Вашингтон; Джордан, ФРВ (19 сентября 1919 г.). «Триггерное реле на трехэлектродных термоэлектронных лампах» . Электрик . 83 : 298.

- Перепечатано в: Экклс, Вашингтон; Джордан, ФРГ (декабрь 1919 г.). «Триггерное реле на трехэлектродных термоэлектронных лампах» . Радиообзор . 1 (3): 143–6.

- Резюме в: Экклс, Вашингтон; Джордан, ФРВ (1919). «Триггерное реле с использованием трехэлектродных термоэмиссионных ламп» . Отчет восемьдесят седьмого собрания Британской ассоциации содействия развитию науки: Борнмут: 1919 г., 9–13 сентября . стр. 271–2.

- ^ Пью, Эмерсон В.; Джонсон, Лайл Р.; Палмер, Джон Х. (1991). Системы IBM 360 и ранние версии 370 . МТИ Пресс. п. 10 . ISBN 978-0-262-16123-7 .

- ^ Флауэрс, Томас Х. (1983), «Дизайн колосса» , Анналы истории вычислений , 5 (3): 249, doi : 10.1109/MAHC.1983.10079 , S2CID 39816473

- ^ Гейтс, Эрл Д. (2000). Введение в электронику (4-е изд.). Дельмар Томсон (Сенгейдж) Обучение. п. 299. ИСБН 978-0-7668-1698-5 .

- ^ Фогель, Макс; Гу, Ю-Лян (1998). Решение проблем с электроникой, Том 1 (переработанное издание). Ассоциация исследований и образования. п. 1223. ИСБН 978-0-87891-543-9 .

- ^ Линдли, Польша (август 1968 г.). «письмо от 13 июня 1968 г.». ЭДН .

- ^ Фистер, Монтгомери (1958). Логическое проектирование цифровых компьютеров . Уайли. п. 128. ИСБН 9780608102658 .

- ^ США 2850566 , Нельсон, Элдред К., «Высокоскоростная система печати», опубликован 2 сентября 1958 г., передан компании Hughes Aircraft Co.

- ^ Лангхольц, Гидеон; Кандель, Авраам; Мотт, Джо Л. (1998). Основы проектирования цифровой логики . Всемирная научная. п. 344. ИСБН 978-981-02-3110-1 .

- ^ «Краткое описание типов поведения шлепанцев» . Проверено 16 апреля 2018 г.

- ^ Хинрихсен, Дидерих; Причард, Энтони Дж. (2006). «Пример 1.5.6 (защелка R – S и защелка J – K)» . Теория математических систем I: моделирование, анализ пространства состояний, устойчивость и устойчивость . Спрингер. стр. 63–64. ISBN 9783540264101 .

- ^ Фархат, Хасан А. (2004). Цифровой дизайн и компьютерная организация . Том. 1. ЦРК Пресс. п. 274. ИСБН 978-0-8493-1191-8 .

- ^ Jump up to: а б Когге, Питер М. (1981). Архитектура конвейерных компьютеров . МакГроу-Хилл. стр. 25–27. ISBN 0-07-035237-2 .

- ^ Коттен, Л.В. (1965). «Схема реализации высокоскоростных трубопроводных систем». Материалы осенней совместной компьютерной конференции, состоявшейся 30 ноября — 1 декабря 1965 г., Часть I по XX — AFIPS '65 (Осень, часть I) . стр. 489–504. дои : 10.1145/1463891.1463945 . S2CID 15955626 .

{{cite book}}:|journal=игнорируется ( помогите ) - ^ Эрл, Джон Г. (март 1965 г.). «Зафиксированный сумматор переноса-сохранения». Бюллетень технической информации IBM . 7 (10): 909–910.

- ^ Jump up to: а б Омонди, Амос Р. (1999). Микроархитектура конвейерных и суперскалярных компьютеров . Спрингер. стр. 40–42. ISBN 978-0-7923-8463-2 .

- ^ Jump up to: а б Кункель, Стивен Р.; Смит, Джеймс Э. (май 1986 г.). «Оптимальная конвейеризация в суперкомпьютерах». Новости компьютерной архитектуры ACM SIGARCH . 14 (2). АКМ: 404–411 [406]. CiteSeerX 10.1.1.99.2773 . дои : 10.1145/17356.17403 . ISSN 0163-5964 . S2CID 2733845 .

- ^ «D-триггер» . Архивировано из оригинала 23 февраля 2014 г. Проверено 5 июня 2016 г.

- ^ «Шлепанцы с краевым триггером» . Архивировано из оригинала 8 сентября 2013 г. Проверено 15 декабря 2011 г.

- ^ Обзор систем цифровой компьютерной памяти

- ^ Техническое описание SN7474 TI

- ^ Jump up to: а б Мано, М. Моррис; Кайм, Чарльз Р. (2004). Основы логики и компьютерного проектирования, 3-е издание . Река Аппер-Сэддл, Нью-Джерси, США: Pearson Education International. п. 283. ИСБН 0-13-191165-1 .

- ^ Jump up to: а б Харрис, С; Харрис, Д. (2016). Цифровой дизайн и компьютерная архитектура — ARM Edition . Морган Кауфманн, Уолтем, Массачусетс. ISBN 978-0-12-800056-4 .

- ^ Чейни, Томас Дж.; Мольнар, Чарльз Э. (апрель 1973 г.). «Аномальное поведение схем синхронизатора и арбитра». Транзакции IEEE на компьютерах . С-22 (4): 421–422. дои : 10.1109/TC.1973.223730 . ISSN 0018-9340 . S2CID 12594672 .

- ^ Часто приписывают Дону Кнуту (1969) (см. Мидхат Дж. Газале (2000). Число: от Ахмеса до Кантора . Издательство Принстонского университета. п. 57. ИСБН 978-0-691-00515-7 . ), термин «трип-флап-флоп» на самом деле появился в компьютерной литературе гораздо раньше, например, Боудон, Эдвард К. (1960). Конструкция и применение «триггера-флапа-флопа» с использованием туннельных диодов (Магистерская диссертация) . Университет Северной Дакоты. и в Александр, В. (февраль 1964 г.). «Тричный компьютер» . Электроника и энергетика . 10 (2). ИЭПП: 36–39. дои : 10.1049/эп.1964.0037 .

- ^ «Тричный «кульп-флап-флоп» » . Архивировано из оригинала 5 января 2009 г. Проверено 17 октября 2009 г.

- ^ США 6975152 , Лапидус, Питер Д., «Триггер, поддерживающий бесперебойную работу на горячей шине и методе», опубликован 13 декабря 2005 г., передан компании Advanced Micro Devices Inc.

- ^ Ирвинг, Турман А.; Шива, Саджан Г.; Нэгл, Х. Трой (март 1976 г.). «Триггеры для многозначной логики». Транзакции IEEE на компьютерах . С-25 (3): 237–246. дои : 10.1109/TC.1976.5009250 . S2CID 34323423 .

- ^ У, Хаоминь; Чжуан Нань (июль 1991 г.). «Исследование троичного триггера JKL, запускаемого по фронту». Журнал электроники (Китай) . 8 (3): 268–275. дои : 10.1007/BF02778378 . S2CID 61275953 .

Внешние ссылки

[ редактировать ]- Иерархия триггеров. Архивировано 8 апреля 2015 г. на Wayback Machine . Здесь показаны интерактивные схемы триггеров.

- JK-триггер

- Ширрифф, Кен (август 2022 г.). «Реверс-инжиниринг гибридного триггерного модуля 1960-х годов с использованием рентгеновской компьютерной томографии» .