ИА-64

| Дизайнер | HP и Интел |

|---|---|

| Биты | 64-битная |

| Представлено | 2001 |

| Дизайн | ЭПИК |

| Тип | Загрузка-сохранение |

| Кодирование | Зафиксированный |

| Ветвление | Регистр условий |

| Порядок байтов | Выбираемый |

| Регистры | |

| общего назначения | 128 (64 бита плюс 1 бит ловушки ; 32 являются статическими, 96 используют окна регистров ); 64 1-битных регистра предикатов |

| Плавающая точка | 128 |

IA-64 ( архитектура Intel Itanium ) — архитектура набора команд (ISA) снятого с производства Itanium семейства 64-битных Intel микропроцессоров . Базовая спецификация ISA была разработана компанией Hewlett-Packard (HP) и впоследствии была реализована Intel в сотрудничестве с HP. Первый процессор Itanium под кодовым названием Merced был выпущен в 2001 году.

Архитектура Itanium основана на явном параллелизме на уровне инструкций , при котором компилятор решает, какие инструкции выполнять параллельно. Это контрастирует с суперскалярными архитектурами, которые зависят от процессора для управления зависимостями инструкций во время выполнения. Во всех моделях Itanium, вплоть до Tukwila включительно , ядра выполняют до шести инструкций за такт .

В 2008 году Itanium был четвертым по распространенности микропроцессорной архитектурой для систем корпоративного класса после x86-64 , Power ISA и SPARC . [1]

В 2019 году Intel объявила о прекращении выпуска последнего из процессоров, поддерживающих архитектуру IA-64.

История [ править ]

Развитие [ править ]

В 1989 году компания HP начала беспокоиться о том, что архитектуры вычислений с сокращенным набором команд (RISC) приближаются к пределу обработки, составляющему одну инструкцию за цикл . Исследователи Intel и HP изучали варианты компьютерной архитектуры для будущих проектов и отдельно начали исследовать новую концепцию, известную как очень длинное командное слово (VLIW). [2] который появился в результате исследования Йельского университета в начале 1980-х годов. [3]

VLIW — это концепция компьютерной архитектуры (например, RISC и CISC ), в которой одно командное слово содержит несколько инструкций, закодированных в одном очень длинном командном слове, чтобы облегчить процессору выполнение нескольких инструкций в каждом такте. Типичные реализации VLIW в значительной степени полагаются на сложные компиляторы, которые определяют во время компиляции, какие инструкции могут выполняться одновременно, и правильное планирование выполнения этих инструкций, а также помогают предсказать направление операций ветвления. Ценность этого подхода заключается в том, чтобы выполнить больше полезной работы за меньшее количество тактовых циклов и упростить требования к оборудованию для планирования инструкций процессора и прогнозирования ветвлений, с штрафом в виде увеличения сложности процессора, стоимости и энергопотребления в обмен на более быстрое выполнение.

Производство [ править ]

В это время в HP начали считать, что для отдельных компаний, занимающихся корпоративными системами, таких как она сама, разработка собственных микропроцессоров больше не является рентабельной. Intel также изучала несколько вариантов архитектуры, позволяющих выйти за рамки x86 ISA и удовлетворить требования к высокопроизводительным корпоративным серверам и высокопроизводительным вычислениям (HPC).

В 1994 году Intel и HP объединились для разработки IA-64 ISA, используя вариант концепции проектирования VLIW, которую Intel назвала явно параллельными вычислениями с командами (EPIC). Целью Intel было использовать опыт, накопленный HP в ходе ранней работы над VLIW, а также собственный опыт для разработки массовой линейки продуктов, ориентированной на вышеупомянутые высокопроизводительные системы, которые можно было бы продавать всем производителям оригинального оборудования (OEM), в то время как HP хотела иметь возможность приобретать готовые процессоры, созданные с использованием серийного производства Intel и современных технологических процессов, которые были лучше, чем их процессоры PA-RISC.

Intel взяла на себя руководство процессом проектирования и коммерциализации, а HP внесла свой вклад в определение ISA, микроархитектуру Merced/Itanium и Itanium 2. Первоначальным целевым годом для выпуска первого продукта семейства Itanium, Merced, был 1998 год. [2]

Маркетинг [ править ]

Усилия Intel по маркетингу продуктов и привлечению промышленности были значительными и позволили добиться победы в проектировании у большинства OEM-производителей корпоративных серверов, в том числе на базе RISC-процессоров того времени. Отраслевые аналитики предсказывали, что IA-64 будет доминировать на серверах, рабочих станциях и настольных компьютерах высокого класса и в конечном итоге вытеснит архитектуры RISC и CISC для всех приложений общего назначения. [4] [5] Compaq и Silicon Graphics решили отказаться от дальнейшего развития архитектур Alpha и MIPS соответственно в пользу перехода на IA-64. [6]

К 1997 году стало очевидно, что архитектуру IA-64 и компилятор реализовать гораздо сложнее, чем первоначально предполагалось, и поставки Itanium начали замедляться. [7] Поскольку Itanium был первым процессором EPIC, в ходе разработки возникло больше непредвиденных проблем, чем команда привыкла. Кроме того, концепция EPIC зависела от возможностей компилятора, которые никогда ранее не были реализованы, поэтому требовались дополнительные исследования. [8]

Несколько групп разработали операционные системы для этой архитектуры, включая Microsoft Windows , Unix и Unix-подобные системы, такие как Linux , HP-UX , FreeBSD , Solaris , [9] [10] [11] Тру64 UNIX , [6] и Монтерей/64 [12] (последние три были отменены до выхода на рынок). В 1999 году Intel возглавила формирование отраслевого консорциума с открытым исходным кодом для переноса Linux на IA-64, который они назвали «Trillium» (а позже переименовали в «Trillian» из-за проблемы с товарным знаком), который возглавлял Intel и включал Caldera Systems . CERN , Cygnus Solutions , Hewlett-Packard, IBM, Red Hat , SGI , SuSE , TurboLinux и VA Linux Systems . В результате рабочая версия IA-64 Linux была доставлена раньше запланированного срока и стала первой ОС, работающей на новых процессорах Itanium.

Intel объявила официальное название процессора Itanium 4 октября 1999 года. [13] В считанные часы название «Итаник» было придумано в группе новостей Usenet как игра слов от названия «Титаник» , «непотопляемого» океанского лайнера , затонувшего во время своего первого рейса в 1912 году. [14]

Уже на следующий день, 5 октября 1999 года, AMD объявила о своих планах расширить набор команд Intel x86, включив в него полностью совместимый 64-битный режим, а также представила новую 64-битную архитектуру AMD x86, над которой компания уже работала. будет включен в будущий микропроцессор AMD восьмого поколения под кодовым названием SledgeHammer . [15] AMD также сообщила о полном раскрытии спецификаций архитектуры и дополнительных подробностей, которые будут доступны в августе 2000 года. [16]

Поскольку AMD никогда не приглашалась участвовать в разработке архитектуры IA-64, а любое лицензирование казалось маловероятным, расширение архитектуры AMD64 с самого начала позиционировалось как эволюционный способ добавления 64-битных вычислительных возможностей к существующей архитектуре x86. , при этом по-прежнему поддерживая устаревший 32-битный код x86 , в отличие от подхода Intel по созданию совершенно новой, полностью несовместимой с x86 64-битной архитектуры с IA-64.

Конец жизни [ править ]

В январе 2019 года Intel объявила о прекращении производства Kittson: последняя дата заказа — январь 2020 года, а последняя дата поставки — июль 2021 года. [17] [18] В ноябре 2023 года из ядра Linux была удалена поддержка IA-64 . [19]

Архитектура [ править ]

Intel подробно задокументировала набор инструкций Itanium. [20] и техническая пресса предоставила обзоры. [4] [7]

За свою историю архитектура несколько раз переименовывалась. Первоначально HP называла его PA-WideWord . Позже Intel назвала его IA-64 , затем Itanium Processor Architecture (IPA), [21] прежде чем остановиться на архитектуре Intel Itanium , но ее до сих пор широко называют IA-64 .

Это 64-битная явно параллельная архитектура с большим количеством регистров. Базовое слово данных имеет длину 64 бита и имеет побайтовую адресацию. Логическое адресное пространство равно 2. 64 байты. Архитектура реализует предсказание , предположение и предсказание ветвей . Для передачи параметров он использует окно регистров переменного размера. Тот же механизм используется и для параллельного выполнения циклов. Спекуляция, предсказание, предсказание и переименование находятся под контролем компилятора: каждое командное слово включает для этого дополнительные биты. Такой подход является отличительной чертой архитектуры.

В архитектуре реализовано большое количество регистров: [22] [23] [24]

- общего назначения 128 целочисленных регистров , 64-битные плюс один бит ловушки («NaT», что означает «не вещь»), используемые для спекулятивного выполнения . 32 из них являются статическими, остальные 96 сложены с использованием окон регистров переменного размера или вращаются для конвейерных циклов.

gr0всегда читает 0. - 128 регистров с плавающей запятой . Регистры с плавающей запятой имеют длину 82 бита, чтобы сохранить точность промежуточных результатов. Вместо специального бита ловушки «NaT», как в целочисленных регистрах, регистры с плавающей запятой имеют значение ловушки, называемое «NaTVal» («Не значение вещи»), похожее на NaN (но отличное от него) . Они также имеют 32 статических регистра и 96 оконных или вращающихся регистров.

fr0всегда читается +0,0 иfr1всегда читается +1,0. - 64 однобитных регистра-предиката. Они имеют 16 статических регистров и 48 оконных или вращающихся регистров.

pr0всегда читается как 1 (истина). - 8 регистров ветвления, для адресов косвенных переходов.

br0устанавливается на обратный адрес, когда функция вызывается с помощьюbr.call. - 128 регистров специального назначения (или «приложений»), которые в основном представляют интерес для ядра, а не для обычных приложений. Например, один регистр под названием

bspуказывает на второй стек, в котором оборудование автоматически выгружает регистры при переворачивании окна регистров.

Каждое 128-битное командное слово называется пакетом и содержит три слота , каждый из которых содержит 41-битную инструкцию , а также 5-битный шаблон, указывающий, какой тип инструкции находится в каждом слоте. К этим типам относятся M-единица (инструкции памяти), I-единица (целочисленное ALU, целое число, не являющееся ALU, или длинные немедленные расширенные инструкции), F-единица (инструкции с плавающей запятой) или B-единица (расширенная ветвь или длинная ветвь). инструкции). Шаблон также кодирует остановки , которые указывают на наличие зависимости между данными до и после остановки. Все инструкции между парой остановок составляют группу инструкций , независимо от их объединения, и должны быть свободны от многих типов зависимостей данных; эти знания позволяют процессору выполнять инструкции параллельно без необходимости выполнять собственный сложный анализ данных, поскольку этот анализ уже был выполнен при написании инструкций.

В каждом слоте все инструкции, за исключением нескольких, являются предикативными, определяя регистр предикатов, значение которого (истина или ложь) будет определять, будет ли выполнена инструкция. Предикатные инструкции, которые должны выполняться всегда, основаны на pr0, что всегда читается как правда.

Язык ассемблера и формат инструкций IA-64 были специально разработаны для написания в основном компиляторами, а не людьми. Инструкции должны быть сгруппированы в группы по три, гарантируя, что эти три инструкции соответствуют разрешенному шаблону. Инструкции должны выдавать остановки между определенными типами зависимостей данных, а также остановки могут использоваться только в ограниченных местах согласно разрешенным шаблонам.

Выполнение инструкций [ править ]

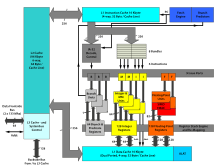

Механизм выборки может считывать до двух пакетов за такт из кэша L1 в конвейер. Когда компилятор сможет извлечь из этого максимальную выгоду, процессор сможет выполнить шесть инструкций за такт. Процессор имеет тридцать функциональных исполнительных блоков в одиннадцати группах. Каждый модуль может выполнять определенное подмножество набора команд , и каждый модуль выполняется со скоростью одна инструкция за цикл, если только выполнение не останавливается в ожидании данных. Хотя не все устройства в группе выполняют одинаковые подмножества набора команд, общие инструкции могут выполняться в нескольких модулях.

В группы исполнительных устройств входят:

- Шесть АЛУ общего назначения, два целочисленных блока, один блок сдвига.

- Четыре блока кэширования данных

- Шесть мультимедийных блоков, два параллельных блока смены, один параллельный умножитель, один счетчик населения

- с плавающей запятой Два 82-битных блока умножения-накопления , два блока SIMD с плавающей запятой умножения-накопления (по две 32-битные операции каждый) [25]

- Три филиала

В идеале компилятор часто может группировать инструкции в наборы по шесть команд, которые могут выполняться одновременно. Поскольку модули с плавающей запятой реализуют операцию умножения-накопления , одна инструкция с плавающей запятой может выполнять работу двух инструкций, когда приложению требуется умножение, за которым следует сложение: это очень часто встречается в научной обработке. Когда это происходит, процессор может выполнить четыре FLOP за цикл. Например, Itanium с частотой 800 МГц имел теоретическую производительность 3,2 GFLOPS , а самый быстрый Itanium 2 с частотой 1,67 ГГц имел оценку 6,67 GFLOPS.

На практике процессор часто может использоваться недостаточно, поскольку не все слоты заполнены полезными инструкциями, например, из-за зависимостей данных или ограничений в доступных шаблонах пакетов. Для максимально плотного кода требуется 42,6 бита на инструкцию по сравнению с 32 битами на инструкцию в традиционных RISC-процессорах того времени, а отсутствие операций из-за нерационального использования слотов еще больше снижает плотность кода. Дополнительные инструкции для спекулятивной загрузки и подсказки для ветвей и кеша непрактично генерировать оптимальным образом, поскольку компилятор не может предсказать содержимое различных уровней кеша в системе, выполняющей несколько процессов и принимающей прерывания.

Архитектура памяти [ править ]

С 2002 по 2006 год процессоры Itanium 2 имели общую иерархию кэша. У них было 16 КБ кэша инструкций уровня 1 и 16 КБ кэша данных уровня 1. Кэш L2 был унифицирован (как инструкций, так и данных) и составляет 256 КБ. Кэш 3-го уровня также был унифицирован и его размер варьировался от 1,5 МБ до 24 МБ. Кэш L2 объемом 256 КБ содержит достаточную логику для обработки операций с семафором, не нарушая работу основного арифметико-логического устройства (АЛУ).

Доступ к основной памяти осуществляется через шину к внешнему чипсету . Шина Itanium 2 первоначально называлась шиной McKinley, но теперь ее обычно называют шиной Itanium. Скорость шины постоянно увеличивалась с выходом новых выпусков процессоров. Шина передает 2×128 бит за такт, поэтому шина McKinley 200 МГц передает 6,4 ГБ/с, а шина Montecito 533 МГц передает 17,056 ГБ/с. [26]

Архитектурные изменения [ править ]

Процессоры Itanium, выпущенные до 2006 года, имели аппаратную поддержку архитектуры IA-32 , позволяющую поддерживать устаревшие серверные приложения, но производительность кода IA-32 была намного хуже, чем для собственного кода, а также хуже, чем производительность современных процессоров x86. В 2005 году Intel разработала уровень выполнения IA-32 (IA-32 EL), программный эмулятор, обеспечивающий лучшую производительность. Таким образом, с появлением Montecito Intel отказалась от аппаратной поддержки кода IA-32.

В 2006 году, с выпуском Montecito , Intel внесла ряд усовершенствований в базовую архитектуру процессора, в том числе: [27]

- Аппаратная многопоточность: каждое ядро процессора поддерживает контекст для двух потоков выполнения. Когда один поток останавливается во время доступа к памяти, другой поток может выполниться. Intel называет это «грубой многопоточностью», чтобы отличить ее от « технологии гиперпоточности », встроенной в некоторые микропроцессоры x86 и x86-64 .

- Аппаратная поддержка виртуализации : Intel добавила технологию виртуализации Intel (Intel VT-i), которая обеспечивает аппаратную поддержку основных функций виртуализации. Виртуализация позволяет программному « гипервизору » одновременно запускать на процессоре несколько экземпляров операционной системы.

- Улучшения кэша: в Montecito добавлен разделенный кэш L2, который включает выделенный кэш L2 объемом 1 МБ для инструкций. Исходный кеш L2 объемом 256 КБ был преобразован в выделенный кеш данных. Montecito также включал до 12 МБ встроенной кэш-памяти L3.

См. также [ править ]

Ссылки [ править ]

- ^ Морган, Тимоти (27 мая 2008 г.). «Серверный бизнес наслаждается циклом обновления X64 в первом квартале» . IT-джунгли . Архивировано из оригинала 3 марта 2016 г. Проверено 29 октября 2008 г.

- ↑ Перейти обратно: Перейти обратно: а б «Изобретение Itanium: как лаборатории HP помогли создать архитектуру микросхем следующего поколения» . HP Лаборатории . Июнь 2001 г. Архивировано из оригинала 4 марта 2012 г. Проверено 23 марта 2007 г.

- ^ Фишер, Джозеф А. (1983). «Архитектуры с очень длинными инструкциями и ELI-512». Материалы 10-го ежегодного международного симпозиума по архитектуре компьютеров . Международный симпозиум по компьютерной архитектуре. Нью-Йорк, штат Нью-Йорк, США: Ассоциация вычислительной техники (ACM). стр. 140–150. дои : 10.1145/800046.801649 . ISBN 0-89791-101-6 .

- ↑ Перейти обратно: Перейти обратно: а б Де Гелас, Йохан (9 ноября 2005 г.). «Итаниум, есть ли свет в конце туннеля?» . АнандТех . Архивировано из оригинала 3 мая 2012 г. Проверено 23 марта 2007 г.

- ^ Такахаши, Дин (08 мая 2009 г.). «Выходное интервью: уходящий в отставку председатель Intel Крейг Барретт о незавершенных делах отрасли» . ВенчурБит . Архивировано из оригинала 21 апреля 2018 г. Проверено 17 мая 2009 г.

- ↑ Перейти обратно: Перейти обратно: а б «Итаниум: поучительная история» . Технические новости на ZDNet . 07.12.2005. Архивировано из оригинала 9 февраля 2008 г. Проверено 1 ноября 2007 г.

- ↑ Перейти обратно: Перейти обратно: а б Шенкленд, Стивен (8 июля 1999 г.). «Чип Intel Merced может еще больше ускользнуть» . Новости CNET . Архивировано из оригинала 24 октября 2012 г. Проверено 16 октября 2008 г.

- ^ «Микропроцессоры — VLIW, прошлое» (PDF) . Нью-Йоркский университет . 18 апреля 2002 г. Архивировано (PDF) из оригинала 27 июня 2018 г. Проверено 26 июня 2018 г.

- ^ Виджаян, Джайкумар (1 сентября 1999 г.). «Solaris для IA-64 появится этой осенью» . Компьютерный мир . Архивировано из оригинала 15 января 2000 г.

- ^ Вулф, Александр (2 сентября 1999 г.). «В компании Merced предпринимаются усилия по базовой логике» . ЭЭ Таймс . Архивировано из оригинала 06 марта 2016 г. Проверено 27 февраля 2016 г.

- ^ «Sun представляет комплект разработчика Solaris для Intel для ускорения разработки приложений на Solaris; отмеченные наградами инструменты Sun помогают независимым поставщикам программного обеспечения с легкостью разрабатывать приложения для Solaris на Intel уже сегодня» . Деловой провод . 10 марта 1998 г. Архивировано из оригинала 20 сентября 2004 г. Проверено 16 октября 2008 г.

- ^ «Чип следующего поколения преодолел ключевой рубеж» . CNET News.com . 17 сентября 1999 г. Архивировано из оригинала 9 августа 2011 г. Проверено 1 ноября 2007 г.

- ^ Канеллос, Майкл (4 октября 1999 г.). «Intel называет чип Merced Itanium» . CNET News.com . Архивировано из оригинала 30 декабря 2015 г. Проверено 30 апреля 2007 г.

- ^ Финстад, Крейг (4 октября 1999 г.). «Ре:Итаниум» . Группа новостей : comp.sys.mac.advocacy . Проверено 19 декабря 2013 г.

- ^ «AMD раскрывает новые технологии на форуме Microporcessor» (пресс-релиз). АМД. 5 октября 1999 года. Архивировано из оригинала 8 марта 2012 года . Проверено 15 августа 2022 г.

- ^ «AMD выпускает архитектурную спецификацию x86-64; обеспечивает рыночный переход на 64-битные вычисления» (пресс-релиз). АМД. 10 августа 2000 года. Архивировано из оригинала 8 марта 2012 года . Проверено 15 августа 2022 г.

- ^ Антон Шилов (31 января 2019 г.). «Intel прекращает выпуск процессора Itanium 9700 «Kittson», последнего из процессоров Itanium» . АнандТех . Архивировано из оригинала 16 апреля 2019 года . Проверено 16 апреля 2019 г.

- ^ «Уведомление об изменении продукта» (PDF) . 30 января 2019 г. Архивировано (PDF) из оригинала 1 февраля 2019 г. . Проверено 9 мая 2019 г.

- ^ Ларабель, Майкл (2 ноября 2023 г.). «Поддержка Intel Itanium IA-64 удалена из ядра Linux 6.7» . www.phoronix.com . Фороникс . Проверено 4 ноября 2023 г.

- ^ «Руководство разработчика программного обеспечения для архитектуры Intel Itanium» . Архивировано из оригинала 08 апреля 2019 г. Проверено 08 апреля 2019 г.

- ^ «Информационный бюллетень HPWorks» . Сентябрь 2001 г. Архивировано из оригинала 20 ноября 2008 г. Проверено 24 января 2008 г.

- ^ Чен, Рэймонд (27 июля 2015 г.). «Процессор Itanium, часть 1: Прогрев» . Архивировано из оригинала 1 ноября 2018 г. Проверено 31 октября 2018 г.

- ^ Чен, Рэймонд (28 июля 2015 г.). «Процессор Itanium, часть 2: Кодировка инструкций, шаблоны и остановки» . Архивировано из оригинала 1 ноября 2018 г. Проверено 31 октября 2018 г.

- ^ Чен, Рэймонд (29 июля 2015 г.). «Процессор Itanium, часть 3: Соглашение о вызовах Windows, способ передачи параметров» . Архивировано из оригинала 1 ноября 2018 г. Проверено 31 октября 2018 г.

- ^ Шарангпани, Суровый; Арора, Кен (2000). «Микроархитектура процессора Itanium». IEEE микро . стр. 38–39.

- ^ Катальдо, Энтони (30 августа 2001 г.). «Intel оснащает процессор Itanium более быстрой работой» . ЭЭ Таймс . Архивировано из оригинала 01 августа 2020 г. Проверено 19 января 2020 г.

- ^ «Анонс продукта Intel» . Интел Веб-сайт . Архивировано из оригинала 7 ноября 2007 года . Проверено 16 мая 2007 г.

Внешние ссылки [ править ]

- Домашняя страница Intel Itanium

- Домашняя страница серверов Hewlett Packard Enterprise Integrity

- Технические характеристики Intel Itanium

- Некоторая недокументированная информация о микроархитектуре Itanium 2 на Wayback Machine (архивировано 23 февраля 2007 г.)

- Учебное пособие по IA-64, включая примеры кода.

- Документация по Itanium в HP