Пентиум (оригинал)

| |

| Общая информация | |

|---|---|

| Запущен | 22 марта 1993 г. |

| Снято с производства | 15 июля 1999 г. [1] [ нужен лучший источник ] |

| Продается через | Интел |

| Разработано | Интел |

| Общий производитель |

|

| Код продукта | 80501 (П5) 80502 (P45C, P54CQS, P54CS) 80503 (P55C, Тилламук) |

| Производительность | |

| Макс. процессора Тактовая частота | 60-300 МГц |

| ФСБ скорости | от 50 МГц до 66 МГц |

| Кэш | |

| L1 Кэш | 16–32 КиБ |

| Кэш L2 | До 512 КиБ [2] |

| Архитектура и классификация | |

| Технологический узел | от 800 до 250 нм |

| Микроархитектура | П5 |

| Набор инструкций | х86-16 , ИА-32 |

| Расширения | |

| Физические характеристики | |

| Транзисторы | |

| Ядра |

|

| Розетки | |

| Продукты, модели, варианты | |

| Основные имена |

|

| Модели |

|

| История | |

| Предшественник | я486 |

| Преемники | P6 , Pentium II , Pentium III (преемник SSE) |

| Статус поддержки | |

| Не поддерживается | |

Pentium 22 марта 1993 года . (также называемый i586 x86, ) — микропроцессор представленный Intel Это первый процессор, использующий бренд Pentium . [3] [4] Считается пятым поколением процессоров, совместимых с 8086. [5] его реализация и микроархитектура назывались P5 .

Как и Intel i486 , Pentium имеет набор инструкций, совместимый с 32-битным i386 . Он использует микроархитектуру, очень похожую на i486, но был достаточно расширен для реализации конструкции двойного целочисленного конвейера , а также более совершенного модуля с плавающей запятой . утверждали, что первое невозможно реализовать для набора инструкций CISC . Некоторые ученые и конкуренты RISC [ ВОЗ? ]

P5 Pentium — первый суперскалярный процессор x86 , то есть он часто мог выполнять две инструкции одновременно. Некоторые методы, использованные для реализации этого, были основаны на более раннем суперскаляре Intel i960 CA (1989 г.), тогда как другие детали были изобретены исключительно для конструкции P5. Большие части также были скопированы из i386 или i486, особенно стратегии, используемые для конвейерной обработки сложных кодировок x86. [6] Как и i486, Pentium использовал как оптимизированную систему микрокода, так и RISC-подобные методы, в зависимости от конкретной инструкции или части инструкции.

Другие основные функции включают переработанный и значительно более быстрый модуль вычислений с плавающей запятой, широкую 64-битную шину данных (внешнюю и внутреннюю), отдельные кэши кода и данных , а также множество других методов и функций для повышения производительности.

P5 также имеет лучшую поддержку многопроцессорной обработки по сравнению с i486 и является первым процессором x86 с аппаратной поддержкой, аналогичной мейнфреймам IBM. Intel работала с IBM, чтобы определить эту возможность, а также внедрила ее в микроархитектуру P5. Эта возможность отсутствовала в предыдущих поколениях x86 и процессорах x86 конкурентов.

Чтобы полностью использовать потенциал двойных конвейеров, некоторые компиляторы были оптимизированы для лучшего использования параллелизма на уровне инструкций, хотя не все приложения существенно выиграют от перекомпиляции. Однако более быстрый FPU всегда значительно улучшал производительность с плавающей запятой по сравнению с i486 или i387. Intel потратила ресурсы на работу с поставщиками средств разработки, независимыми поставщиками программного обеспечения и компаниями, производящими операционные системы (ОС), для оптимизации их продуктов.

В октябре 1996 года аналогичный Pentium MMX [7] был представлен, дополнив ту же базовую микроархитектуру набором инструкций MMX , кэшами большего размера и некоторыми другими улучшениями.

Среди конкурентов были суперскаляры PowerPC 601 (1993 г.), SuperSPARC (1992 г.), DEC Alpha 21064 (1992 г.), AMD 29050 (1990 г.), Motorola MC88110 (1991 г.) и Motorola 68060 (1994 г.), большинство из которых также использовали суперскаляры по порядку. конфигурация с двойным конвейером инструкций, а также несуперскалярные Motorola 68040 (1990 г.) и MIPS R4000 (1991 г.).

Intel прекратила выпуск процессоров Pentium P5 (продававшихся как более дешевый продукт с момента выпуска Pentium II в 1997 году) в начале 2000 года в пользу процессора Celeron , который также заменил бренд 80486 . [1]

Развитие [ править ]

Микроархитектура P5 была разработана той же командой Санта-Клары, которая разработала 386 и 486. [8] Проектные работы начались в 1989 году; [9] : 88 команда решила использовать суперскалярную RISC-архитектуру, которая позволит объединить технологии RISC и CISC, [10] со встроенным кэшем, операциями с плавающей запятой и прогнозированием ветвей. Предварительный проект был впервые успешно смоделирован в 1990 году, после чего была выполнена компоновка проекта. К этому времени в команде было несколько десятков инженеров. Проект был записан на пленку или перенесен на кремний в апреле 1992 года, после чего началось бета-тестирование. [11] К середине 1992 года в команде P5 было 200 инженеров. [9] : 89 Intel сначала планировала продемонстрировать P5 в июне 1992 года на выставке PC Expo , а официально анонсировать процессор в сентябре 1992 года. [12] но проблемы с конструкцией вынудили отменить демо-версию, а официальное представление чипа было отложено до весны 1993 года. [13] [14]

Джон Х. Кроуфорд , главный архитектор оригинального 386, участвовал в разработке P5. [15] вместе с Дональдом Альпертом, который руководил архитектурной командой. Дрор Авнон руководил разработкой FPU. [16] Винод К. Дхам был генеральным менеджером группы P5. [9] : 90

В проекте многоядерной архитектуры Intel Larrabee используется ядро процессора, полученное из ядра P5 (P54C), дополненное многопоточностью , 64-битными инструкциями и блоком векторной обработки шириной 16 пикселей . [17] Маломощная микроархитектура Bonnell от Intel , использованная в ранних процессорных ядрах Atom, также использует двойной упорядоченный конвейер, аналогичный P5. [18]

Intel использовала название Pentium вместо 586, поскольку в 1991 году она проиграла спор по поводу товарного знака «386», когда судья постановил, что этот номер является общим . Компания наняла Lexicon Branding , чтобы придумать новое нечисловое название. [19]

Улучшения по сравнению с i486 [ править ]

Микроархитектура P5 имеет несколько важных преимуществ по сравнению с предыдущей архитектурой i486.

- Производительность :

- Суперскалярная архитектура. Pentium имеет два канала данных (конвейеров), которые во многих случаях позволяют ему выполнять две инструкции за такт. Главный канал (U) может обрабатывать любые инструкции, а другой (V) — самые распространенные простые инструкции. Некоторый [ ВОЗ? ] Сторонники компьютера с сокращенным набором команд (RISC) утверждали, что «сложный» набор команд x86, вероятно, никогда не будет реализован с помощью жестко конвейерной микроархитектуры , а тем более с помощью двухконвейерной конструкции. 486 и Pentium продемонстрировали, что это действительно возможно и осуществимо.

- 64-битная внешняя шина данных удваивает объем информации, которую можно прочитать или записать при каждом доступе к памяти, и, следовательно, позволяет Pentium загружать свой кэш кода быстрее, чем 80486; он также обеспечивает более быстрый доступ и хранение данных 64-битного и 80-битного x87 процессора .

- Разделение кешей кода и данных уменьшает конфликты выборки и чтения/записи операндов по сравнению с 486. Чтобы сократить время доступа и стоимость реализации, оба они являются двухсторонними ассоциативными вместо одного 4-стороннего кеша, как у 486. Соответствующим усовершенствованием в Pentium является возможность читать непрерывный блок из кэша кода, даже если он разделен между двумя строками кэша (в худшем случае не менее 17 байт).

- Гораздо более быстрый модуль с плавающей запятой . Некоторые инструкции продемонстрировали огромное улучшение, особенно FMUL: пропускная способность в 15 раз выше, чем у 80486 FPU. Pentium также может выполнять инструкцию FXCH ST(x) параллельно с обычной (арифметической или загрузкой/сохранением) инструкцией FPU.

- Сумматоры адресов с четырьмя входами позволяют Pentium еще больше сократить задержку вычисления адреса по сравнению с 80486. Pentium может рассчитывать полные режимы адресации с базой сегмента + базовым регистром + масштабируемым регистром + немедленным смещением за один цикл; Модель 486 имеет только адресный сумматор с тремя входами и поэтому должна делить такие вычисления на два цикла.

- Микрокод 80486 может использовать оба конвейера, чтобы позволить автоповторяющимся инструкциям, таким как REP MOVSW, выполнять одну итерацию за каждый такт, в то время как требовалось три такта на итерацию (а самые ранние чипы x86 значительно больше, чем 486). Кроме того, оптимизация доступа к первым словам микрокода на этапах декодирования помогает значительно ускорить выполнение нескольких часто встречающихся инструкций, особенно в их наиболее распространенных формах и в типичных случаях. Некоторые примеры: (486 → Pentium, в тактах): CALL (3 → 1), RET (5 → 2), сдвиг/поворот (2–3 → 1).

- Более быстрый, полностью аппаратный умножитель делает такие инструкции, как MUL и IMUL, в несколько раз быстрее (и более предсказуемыми), чем в 80486; время выполнения сокращается с 13 до 42 тактов до 10–11 для 32-битных операндов.

- Виртуализированные прерывания для ускорения виртуального режима 8086 .

- Прогнозирование ветвей

- Другие особенности :

- Расширенные функции отладки благодаря введению порта отладки на базе процессора (см. « Отладка процессора Pentium» в Руководстве разработчика, том 1).

- Расширенные функции самотестирования, такие как проверка четности кэша L1 (см. «Структура кэша» в Руководстве разработчика, том 1).

- Новые инструкции: CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM.

- Были исключены тестовые регистры TR0–TR7 и инструкции MOV для доступа к ним.

- В более поздний Pentium MMX также был добавлен набор инструкций MMX основной целочисленной одной инструкции и нескольких данных ( SIMD , расширение набора команд ), предназначенное для использования в мультимедийных приложениях. MMX нельзя было использовать одновременно с инструкциями FPU x87 , поскольку регистры использовались повторно (чтобы обеспечить быстрое переключение контекста). Более важными улучшениями были удвоение размеров кэша инструкций и данных, а также несколько микроархитектурных изменений для повышения производительности.

Pentium был разработан для выполнения более 100 миллионов инструкций в секунду (MIPS). [20] а модель с частотой 75 МГц смогла достичь скорости 126,5 MIPS в некоторых тестах. [21] Архитектура Pentium обычно обеспечивала чуть менее чем вдвое большую производительность, чем процессор 486 за такт в обычных тестах. Самые быстрые детали 80486 (с несколько улучшенной микроархитектурой и работой на частоте 100 МГц) были почти такими же мощными, как и Pentium первого поколения, а AMD Am5x86 , который, несмотря на свое название, на самом деле является процессором класса 486, был примерно равен Pentium 75 по показателям производительности. чистая производительность ALU.

Ошибки [ править ]

В ранних версиях Pentiums P5 с частотой 60–100 МГц была проблема с модулем операций с плавающей запятой, которая приводила к неверным (но предсказуемым) результатам некоторых операций деления. Этот недостаток, обнаруженный в 1994 году профессором Томасом Найсли из Линчберг-колледжа, штат Вирджиния, стал широко известен как ошибка Pentium FDIV и вызвал затруднения у Intel, которая создала программу обмена для замены неисправных процессоров.

В 1997 году была обнаружена еще одна ошибка, которая могла позволить вредоносной программе привести к сбою системы без каких-либо специальных привилегий, — « ошибка F00F ». Это затронуло все процессоры серии P5, и фиксированные степпинги так и не были выпущены, однако в современные операционные системы были внесены обходные пути для предотвращения сбоев.

Ядра и степпинги [ править ]

Pentium был основным микропроцессором Intel для персональных компьютеров в середине 1990-х годов. Первоначальный дизайн был переработан в более новых процессах и добавлены новые функции для поддержания конкурентоспособности и для удовлетворения конкретных рынков, таких как портативные компьютеры. В результате появилось несколько вариантов микроархитектуры P5.

P5 [ править ]

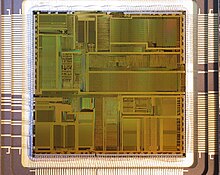

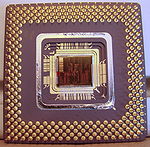

Первое ядро микропроцессора Pentium имело кодовое название «P5». Его код продукта был 80501 (80500 для самых ранних версий Q0399). Существовали две версии, предназначенные для работы на частоте 60 МГц и 66 МГц соответственно с использованием Socket 4 . Эта первая реализация Pentium была выпущена в форм-факторе PGA с 273 выводами и работала от источника питания 5 В. (произошло от обычных требований совместимости транзисторно-транзисторной логики (TTL)). Он содержал 3,1 миллиона транзисторов , имел размеры 16,7 на 17,6 мм и площадь 293,92 мм. 2 . [22] Он был изготовлен с использованием с длиной волны 800 нм . биполярного комплементарного процесса металл-оксид-полупроводник ( BiCMOS ) [23] Конструкция с напряжением 5 В привела к относительно высокому энергопотреблению для своей рабочей частоты по сравнению с последующими моделями.

P54C [ править ]

За P5 в 1994 году последовал P54C (80502), версии которого работали на частоте 75, 90 или 100 МГц с использованием источника питания 3,3 В. Отмечая переход на Socket 5 , это был первый процессор Pentium, работавший при напряжении 3,3 В, что снижало энергопотребление, но требовало регулирования напряжения на материнских платах. Как и в случае с процессорами 486 с более высокой тактовой частотой, с этого момента использовался внутренний умножитель тактовой частоты, чтобы позволить внутренней схеме работать на более высокой частоте, чем внешние шины адреса и данных, поскольку увеличить внешнюю частоту сложнее и громоздко из-за физические ограничения. Он также допускал двустороннюю многопроцессорную обработку, имел встроенный локальный APIC и новые функции управления питанием. Он содержал 3,3 миллиона транзисторов и имел размер 163 мм. 2 . [24] была описана как 500 нм и 600 нм . Он был изготовлен по технологии BiCMOS, которая из-за разных определений [24]

P54CQS [ править ]

За P54C в начале 1995 года последовал P54CQS, который работал на частоте 120 МГц. Он был изготовлен по 350-нм техпроцессу BiCMOS и стал первым коммерческим микропроцессором, изготовленным по 350-нм техпроцессу. [24] Количество транзисторов в нем идентично P54C, и, несмотря на более новый процесс, он также имел идентичную площадь кристалла. Чип был подключен к корпусу с помощью проводного соединения , которое допускает соединения только по краям чипа. Меньший чип потребовал бы изменения конструкции корпуса, поскольку существует ограничение на длину проводов, а края чипа будут находиться дальше от контактных площадок на корпусе. Решение заключалось в том, чтобы сохранить чип того же размера, сохранить существующее кольцо-площадку и уменьшить размер логической схемы Pentium только для того, чтобы он мог достичь более высоких тактовых частот. [24]

P54CS [ править ]

За P54CQS вскоре последовал P54CS, который работал на частотах 133, 150, 166 и 200 МГц, и представил Socket 7 . Он содержал 3,3 миллиона транзисторов диаметром 90 мм. 2 и был изготовлен по 350-нм техпроцессу BiCMOS с четырьмя уровнями межсоединений.

P24T [ править ]

P24T Pentium OverDrive для систем 486 был выпущен в 1995 году и основывался на версиях с напряжением 3,3 В, 600 нм и частотой 63 или 83 МГц. Поскольку они использовали Socket 2/3 , пришлось внести некоторые изменения , чтобы компенсировать 32-битную шину данных и более медленный встроенный кэш L2 материнских плат 486. Поэтому они были оснащены кэшем L1 объемом 32 КБ (вдвое больше, чем у процессоров Pentium до P55C).

P55C [ править ]

P55C (или 80503) был разработан Центром исследований и разработок Intel в Хайфе, Израиль . Он продавался как Pentium с MMX технологией (обычно называемый просто Pentium MMX ); хотя он был основан на ядре P5, он содержал новый набор из 57 инструкций «MMX», предназначенных для повышения производительности при выполнении мультимедийных задач, таких как кодирование и декодирование цифровых мультимедийных данных. Линейка Pentium MMX была представлена 22 октября 1996 года и выпущена в январе 1997 года. [25]

Новые инструкции работали с новыми типами данных: 64-битные упакованные векторы из восьми 8-битных целых чисел, четырех 16-битных целых чисел, двух 32-битных целых чисел или одного 64-битного целого числа. Так, например, инструкция PADDUSB (упакованный ADD беззнаковый насыщенный байт) складывает два вектора, каждый из которых содержит восемь 8-битных целых чисел без знака, поэлементно; каждое добавление, которое может привести к переполнению , насыщает , что дает 255 — максимальное значение без знака, которое может быть представлено в байте. Эти довольно специализированные инструкции обычно требуют специального написания программистом для их использования. [ нужна ссылка ]

Другие изменения в ядре включают 6-этапный конвейер (по сравнению с 5 на P5) со стеком возврата (впервые реализованный в Cyrix 6x86) и улучшенный параллелизм, улучшенный декодер инструкций, кэш данных L1 объемом 16 КБ + кэш инструкций L1 объемом 16 КБ с обоими 4 -сторонняя ассоциативность (по сравнению с 8 КБ данных/инструкций L1 с 2-сторонними на P5), 4 буфера записи, которые теперь могут использоваться любым конвейером (по сравнению с одним, соответствующим каждому конвейеру на P5), и улучшенный предсказатель ветвления, взятый из Pentium Про, [26] [27] с буфером на 512 записей (против 256 на P5). [28]

Он содержал 4,5 миллиона транзисторов и имел площадь 140 мм. 2 . Он был изготовлен по КМОП-процессу 280 нм с тем же шагом металла, что и предыдущий процесс BiCMOS 350 нм, поэтому Intel описала его как «350 нм» из-за аналогичной плотности транзисторов. [29] Процесс имеет четыре уровня взаимосвязи. [29]

Хотя P55C остался совместимым с Socket 7 , требования к напряжению для питания чипа отличаются от стандартных спецификаций Socket 7. Большинство материнских плат, изготовленных для Socket 7 до установления стандарта P55C, не соответствуют требованиям двойной шины напряжения, необходимой для правильной работы этого ЦП (напряжение ядра 2,8 В, напряжение ввода/вывода (I/O) 3,3 В). Intel решила эту проблему с помощью комплектов обновления OverDrive, в которых был промежуточный преобразователь с собственной регулировкой напряжения.

Тилламук [ править ]

В процессорах ноутбуков Pentium MMX использовался мобильный модуль , в котором находился процессор. Этот модуль представлял собой печатную плату (PCB) с непосредственно прикрепленным к ней процессором меньшего форм-фактора. Модуль прикреплялся к материнской плате ноутбука, и обычно был установлен распределитель тепла , который контактировал с модулем. Однако с 250-нм Tillamook Mobile Pentium MMX (названным в честь города в Орегоне ) модуль также содержал набор микросхем 430TX вместе с системной статической оперативной памяти кэш-памятью (SRAM) емкостью 512 КБ.

Модели и варианты [ править ]

|    |    |    |  | ||||||||||||||||||

| Кодовое имя | П5 | P54C | P54C/P54CQS | P54CS | P55C | Тилламук | ||||||||||||||||

| Код продукта | 80501 | 80502 | 80503 | |||||||||||||||||||

| Размер процесса | 800 нм | 600 нм или 350 нм* | 350 нм | 350 нм (позже 280 нм) | 250 нм | |||||||||||||||||

| Площадь матрицы ( мм 2 ) | 293,92 (16,7 х 17,6 мм) | 148 при 600 нм / 91 (позже 83) при 350 нм | 91 (позже 83) | 141 @ 350 нм / 128 @ 280 нм | 94,47 (9,06272 х 10,42416 мм) | |||||||||||||||||

| Количество транзисторов (миллионов) | 3.10 | 3.20 | 3.30 | 4.50 | ||||||||||||||||||

| Розетка | Розетка 4 | Розетка 5/7 | Розетка 7 | |||||||||||||||||||

| Упаковка | CPGA /CPGA+IHS | CPGA/CPGA+IHS/ TCP * | CPGA/TCP* | CPGA/TCP* | КПГА/ ППГА | ППГА | TCP* | CPGA/PPGA/TCP* | ППГА/TCP* | TCP/TCP на MMC-1 | ||||||||||||

| Тактовая частота ( МГц ) | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 120* | 133* | 150* | 166 | 200 | 233 | 166 | 200 | 233 | 266 | 300 | |

| Скорость шины ( МГц ) | 60 | 66 | 50 | 60 | 50 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | ||||||||

| Размер кэша уровня 1 | Кэш ассоциативного кода с двусторонним набором 8 КБ. 8 КБ двусторонний набор ассоциативной кэш-памяти с обратной записью | Кэш ассоциативного кода с 4-канальным набором 16 КБ. 16 КБ 4-канальный набор ассоциативной кэш-памяти данных с обратной записью | ||||||||||||||||||||

| Напряжение ядра | 5.0 | 5.15 | 3.3 2,9* | 3.3 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 | 3.3 | 2.2* | 2.45* | 2.45* | 2.8 2.45* | 2.8 | 2.8 | 1.9 1.8* | 1.8* | 1.8* | 1.9 2.0* | 2.0* | |

| Напряжение ввода/вывода | 5.0 | 5.15 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 2.5 | 2.5 | 2.5 | 2.5 | 2.5 | |

| TDP (макс. Вт) | 14.6 (15.3) | 16.0 (17.3) | 8.0 (9.5) 6.0* (7.3*) | 9.0 (10.6) 7.3* (8.8*) | 10,1 (11,7) 8,0 при 600 нм* (9,8 при 600 нм*) 5,9 при 35 Ом* (7,6 при 350 нм*) | 12.8 (13.4) 7.1* (8.8*) | 11.2 (12.2) 7.9* (9.8*) | 11.6 (13.9) 10.0* (12.0*) | 14.5 (15.3) | 15.5 (16.6) | 4.2* | 7.8* (11.8*) | 8.6* (12.7*) | 13.1 (15.7) 9.0* (13.7*) | 15.7 (18.9) | 17.0 (21.5) | 4.5 (7.4) 4.1* (5.4*) | 5.0* (6.1*) | 5.5* (7.0*) | 7.6 (9.2) 7.6* (9.6*) | 8.0* | |

| Представлено | 1993-03-22 | 1994-10-10 | 1994-03-07 | 1995-03-27 | 1995-06-12 | 1996-01-04 | 1996-06-10 | 1996-10-20 | 1997-05-19 | 1997-01-08 | 1997-06-02 | 1997-08 | 1998-01 | 1999-01 | ||||||||

| *Звездочка указывает на то, что они были доступны только в виде чипов Mobile Pentium или Mobile Pentium MMX для ноутбуков . | ||||||||||||||||||||||

| |||||||

| Кодовое имя | P54CTB | ||||||

| Код продукта | ПОДПМТ60X150 | ПОДПМТ66X166 | ПОДПМТ60X180 | ПОДПМТ66X200 | |||

| Размер процесса (нм) | 350 | ||||||

| Розетка | Розетка 5/7 | ||||||

| Упаковка | CPGA с радиатором, вентилятором и регулятором напряжения | ||||||

| Тактовая частота (МГц) | 125 | 150 | 166 | 150 | 180 | 200 | |

| Скорость шины (МГц) | 50 | 60 | 66 | 50 | 60 | 66 | |

| Обновление для | Пентиум 75 | Пентиум 90 | Пентиум 100 и 133 | Пентиум 75 | Пентиум 90, 120 и 150 | Пентиум 100, 133 и 166 | |

| TDP (макс. Вт) | 15.6 | 15.6 | 15.6 | 18 | |||

| Напряжение | 3.3 | 3.3 | 3.3 | 3.3 | |||

|  | ||||||

| Кодовое имя | P55C | Тилламук | |||||

| Код продукта | ФВ8050366200 | ФВ8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT | FV80503CSM66266 | GC80503CSM66266 |

| Размер процесса ( нм ) | 350 | 250 | |||||

| Тактовая частота ( МГц ) | 200 | 233 | 166 | 166 | 166 | 266 | 266 |

| Скорость шины ( МГц ) | 66 | 66 | 66 | 66 | 66 | 66 | 66 |

| Упаковка | ППГА | ППГА | ППГА | БГА | БГА | ППГА | БГА |

| TDP (макс. Вт) | 15.7 | 17 | 4.5 | 4.1 | 4.1 | 7.6 | 7.6 |

| Напряжение | 2.8 | 2.8 | 1.9 | 1.8 | 1.8 | 1.9 | 2.0 |

Конкуренты [ править ]

После появления Pentium такие конкуренты, как NexGen , [30] AMD, Cyrix и Texas Instruments анонсировали процессоры, совместимые с Pentium, в 1994 году. [31] Журнал CIO назвал Nx586 компании NexGen первым процессором, совместимым с Pentium. [32] а журнал PC Magazine назвал Cyrix 6x86 первым. За ними последовал AMD K5 , выпуск которого был отложен из-за трудностей проектирования. Позже AMD купила NexGen, чтобы помочь в разработке AMD K6 , а Cyrix была куплена National Semiconductor . [33] Более поздние процессоры AMD и Intel сохраняют совместимость с оригинальным Pentium.

Список [ править ]

См. также [ править ]

- Список микроархитектур процессоров Intel

- Список процессоров Intel Pentium

- Кэш на флешке (COASt), модули кэша L2 для Pentium

- IA-32 Архитектура набора команд (ISA)

- Intel 82497 Контроллер кэша

Ссылки [ править ]

- ^ Jump up to: Перейти обратно: а б «Уведомление об изменении продукта № 777» (PDF) . Интел. 9 февраля 1999 г. Архивировано из оригинала (PDF) 27 января 2000 г. . Проверено 14 октября 2019 г.

- ^ https://www.intel.com/content/www/us/en/products/sku/49966/intel-pentium-processor-with-mmx-technology-200-mhz-66-mhz-fsb/specifications.html

- ^ Просмотр процессоров в хронологическом порядке по дате выпуска , Intel , получено 14 августа 2007 г.

- ^ Семейство процессоров Intel Pentium , Intel , получено 14 августа 2007 г.

- ^ Т.е. 8086/88, 186/286, 386, 486, П5

- ^ по сравнению с простым процессором RISC, таким как i960.

- ^ официально известный как Pentium с технологией MMX

- ^ Колвелл, Роберт П. (2006). Хроники Pentium: люди, страсть и политика, стоящие за знаковыми чипами Intel . Уайли. п. 1. ISBN 978-0-471-73617-2 .

- ^ Jump up to: Перейти обратно: а б с «Внутри Интел». Деловая неделя . № 3268. 1 июня 1992 г.

- ^ Хаус, Дэйв, «Прекращение дебатов о RISC и CISC», Intel Corporation, Microcomputer Solutions, ноябрь/декабрь 1991 г., стр. 18

- ^ Хортен, Моника (1 мая 1993 г.). «Новая горячая звезда микрочипов» . Новый учёный . № 1871. С. 31 и след. Архивировано из оригинала 27 июля 2011 года . Проверено 9 июня 2009 г.

- ^ Куинлан, Том (16 марта 1992 г.). «Intel предложит взглянуть на свой чип «586»» . Инфомир . п. 8.

- ^ Куинлан, Том; Коркоран, Кейт (15 июня 1992 г.). «Проблемы с дизайном вынудили Intel отменить демонстрацию чипа 586» . Инфомир . Том. 14, нет. 24. с. 1.

- ^ Куинлан, Том; Коркоран, Кейт (27 июля 1992 г.). «Задержка чипа P5 не изменит планы конкурентов» . Инфомир . Том. 14, нет. 30. С. 1, 103.

- ^ Маргулиус, Дэвид Л. (21 июля 2003 г.). «Интелу исполняется 35 лет: что теперь?» . Инфомир . Том. 25, нет. 28. С. 51–55. ISSN 0199-6649 .

- ^ Альперт, Д.; Авнон, Д. (июнь 1993 г.). «Архитектура микропроцессора Pentium]» . IEEE микро . Том. 13, нет. 3. п. 21. дои : 10.1109/40.216745 .

- ^ §3 из Зайлер, Л.; Кэвин, Д.; Эспаса, Э.; Гроховский, Т.; Хуан, М.; Ханрахан, П.; Кармин, С.; Спрэнгл, А.; Форсайт, Дж.; Абраш Р.; Дубей, Р.; Джанкинс, Э.; Лейк, Т.; Шугерман, П. (август 2008 г.). «Larrabee: многоядерная архитектура x86 для визуальных вычислений» (PDF) . Транзакции ACM с графикой . Труды ACM SIGGRAPH 2008. 27 (3): 18:11. дои : 10.1145/1360612.1360617 . ISSN 0730-0301 . S2CID 52799248 . Проверено 18 августа 2023 г.

- ^ Шимпи, Ананд Лал (27 января 2010 г.), Почему Pine Trail не намного быстрее, чем первый атом , получено 4 августа 2010 г.

- ^ Смит, Эрни (14 июня 2017 г.). «Почему Intel больше не может использовать номера товарных знаков» . Порок . Проверено 13 июля 2023 г.

- ^ «Руководство пользователя ПК: Общая информация о компьютере» . Архивировано из оригинала 28 июля 2007 года . Проверено 14 сентября 2007 г.

- ^ Полссон, Кен. «Хронология микропроцессоров» .

- ^ Кейс, Брайан (29 марта 1993 г.). «Intel раскрывает детали реализации Pentium». Отчет микропроцессора .

- ^ «Процессор Intel Pentium (510\60, 567\66). Ноябрь 1994 г.» (PDF) .

- ^ Jump up to: Перейти обратно: а б с д Гвеннап, Линли (27 марта 1995 г.). «Pentium — первый процессор, достигший 0,35 микрона». Отчет микропроцессора .

- ^ Новый чип порождает новые вопросы , CNet , получено 6 февраля 2009 г.

- ^ «Руководство по оптимизации архитектуры Intel» (PDF) . 1997. стр. 2–16. Архивировано из оригинала (PDF) 5 июля 2017 года . Проверено 1 сентября 2017 г.

- ^ «Книга Фила Сторра по аппаратному обеспечению ПК» . Архивировано из оригинала 20 января 2020 года . Проверено 1 сентября 2017 г.

- ^ «Процессор Pentium с технологией MMX» (PDF) . 1997. Архивировано из оригинала (PDF) 5 июля 2010 года . Проверено 1 сентября 2017 г.

- ^ Jump up to: Перейти обратно: а б Слейтер, Майкл (5 марта 1996 г.). «Раскрыт долгожданный P55C от Intel». Отчет микропроцессора .

- ^ Коркоран, Кейт; Кротерс, Брук (11 июля 1994 г.). «NexGen обгонит цены на чипы Intel» . Инфомир . ИДГ : 5.

- ^ Барр, Кристофер (11 января 1994 г.). «Убийцы Пентиумов» . Журнал ПК . 13 (1). Зифф Дэвис : 29.

- ^ Эдвардс, Джон (15 июня 1995 г.). «В чипсах» . Журнал ИТ-директоров . 8 (17). ИДГ : 72–76.

- ^ Слейтер, Майкл (23 сентября 1997 г.). «Процессор для вашего следующего ПК» . Журнал ПК . 16 (16). Зифф Дэвис : 130–133.

Внешние ссылки [ править ]

- CPU-Collection.de - изображения и описания Intel Pentium

- Идентификация процессора Intel Plasma Online

- Проект Pentium Timeline. Архивировано 23 декабря 2021 года в Wayback Machine . В проекте Pentium Timeline показаны самые старые и самые молодые чипы, известные из всех созданных s-спецификаций. Данные отображаются на интерактивной временной шкале.

Таблицы данных Intel [ править ]

- Пентиум (Р5)

- Пентиум (Р54)

- Пентиум ММХ (P55C)

- Мобильный Pentium MMX (P55C)

- Мобильный Pentium MMX (Тилламук)

Руководства Intel [ править ]

В этих официальных руководствах представлен обзор процессора Pentium и его функций:

- Руководство разработчика семейства процессоров Pentium Процессор Pentium (том 1) (номер заказа Intel 241428)

- Руководство разработчика семейства процессоров Pentium, том 2: Справочник по набору инструкций. Архивировано 13 марта 2012 г. на Wayback Machine (номер заказа Intel 243191).

- Руководство разработчика семейства процессоров Pentium , том 3: Руководство по архитектуре и программированию [ постоянная мертвая ссылка ] (номер заказа Intel 241430)