Поперечный рычаг (компьютерный автобус)

| Создано | Силикор Корпорейшн |

|---|---|

| Ширина в битах | 8, 16, 32, 64 |

| Стиль | Параллельно |

| Интерфейс горячего подключения | Нет (чиповая шина) |

| Внешний интерфейс | Нет |

Wishbone Bus — это с открытым исходным кодом аппаратная компьютерная шина , предназначенная для обеспечения связи частей интегральной схемы друг с другом. Цель состоит в том, чтобы обеспечить соединение разных ядер друг с другом внутри чипа. Шина Wishbone используется во многих проектах проекта OpenCores .

Wishbone задуман как «логическая шина». Он не определяет электрическую информацию или топологию шины. Вместо этого спецификация написана с точки зрения «сигналов», тактовых циклов, а также высокого и низкого уровней.

Эта двусмысленность намеренна. Wishbone создан для того, чтобы дизайнеры могли комбинировать несколько проектов, написанных на Verilog , VHDL или каком-либо другом языке логического описания для автоматизации электронного проектирования (EDA). Wishbone предоставляет разработчикам стандартный способ объединения этих аппаратных логических конструкций (называемых «ядрами»).Wishbone имеет 8, 16, 32 и 64-битные шины. Все сигналы синхронизированы с одним тактовым сигналом, но некоторые ответы ведомого устройства должны генерироваться комбинаторно для достижения максимальной производительности. Wishbone позволяет добавлять «шину тегов» для описания данных. Но сброс, простое адресное чтение и запись, перемещение блоков данных и неделимые циклы шины — все работает без тегов.

Wishbone имеет открытый исходный код . Чтобы предотвратить вытеснение своих технологий путем агрессивного патентования, спецификация Wishbone включает примеры предшествующего уровня техники , чтобы доказать, что ее концепции находятся в общественном достоянии.

Устройство не соответствует спецификации Wishbone, если к нему не прилагается таблица данных , в которой описывается, что оно делает, ширина шины, использование и т. д. Для поощрения повторного использования конструкции требуется таблица данных. Создание возможности повторного использования дизайна, в свою очередь, облегчает обмен им с другими.

Простая архитектура шины — это упрощенная версия спецификации Wishbone. [1]

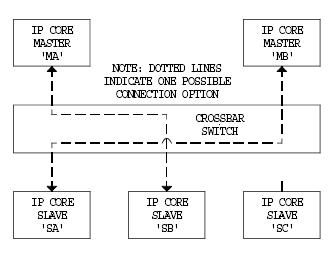

Поперечные топологии

[ редактировать ]Wishbone хорошо адаптируется к распространенным топологиям, таким как «точка-точка», «многие-ко-многим» (т. е. классическая шинная система), иерархическим или даже коммутируемым фабрикам, таким как перекрестные коммутаторы . В более экзотических топологиях Wishbone требуется контроллер или арбитр шины, но устройства по-прежнему поддерживают тот же интерфейс.

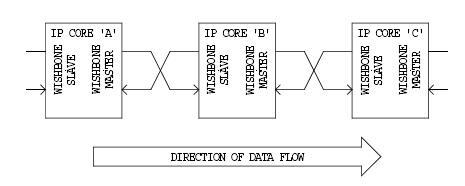

Общий автобус

[ редактировать ]Поток данных

[ редактировать ]Перекладной переключатель

[ редактировать ]Сравнения

[ редактировать ]Сигналы управления поперечными рычагами по сравнению с другими стандартами шины системы на кристалле (SoC):

| Поперечный рычаг | Автобус Авалон | Описание |

|---|---|---|

| циклический | = !write_n или !read_n | указывает, что выполняется действительный цикл шины |

| и т. д. | = выбор чипа | указывает на действительный цикл передачи данных |

| мы | = !write_n и read_n | указывает, является ли текущий цикл локальной шины циклом ЧТЕНИЕ или ЗАПИСЬ. Сигнал инвертируется во время циклов ЧТЕНИЯ и устанавливается во время циклов ЗАПИСИ. |

| подтверждение | = !waitrequest | указывает на прекращение нормального цикла шины подчиненным устройством. |

| Автобус Авалон | Поперечный рычаг | Описание |

|---|---|---|

| Выбор чипа | = и т. д. | указывает, что выбрано ведомое устройство. |

| write_n | = !(cyc и мы) | указывает, что ведущее устройство запрашивает запись на ведомое устройство. |

| read_n | = !(cyc и !we) | указывает, что ведущее устройство запрашивает чтение с ведомого устройства. |

| запрос на ожидание | = !ак | указывает, что ведомое устройство запрашивает ожидание ведущего. |

См. также

[ редактировать ]Ссылки

[ редактировать ]Внешние ссылки

[ редактировать ]- Поперечный рычаг версии B3 — спецификация в формате PDF

- Wishbone Version B4 — PDF-спецификация последней версии Wishbone.

- appnote_01 — Примечание по применению объединения сигналов интерфейса WISHBONE

- Сравнение с другими шинами SoC

- Поперечный рычаг@OpenCores

- [электронная почта защищена]