Интел и960

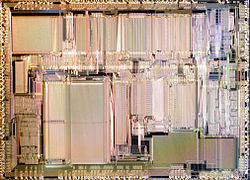

Микропроцессор Intel i960HA | |

| Общая информация | |

|---|---|

| Запущен | 6 апреля 1988 г. [2] |

| Снято с производства | 2007 [1] |

| Общий производитель |

|

| Производительность | |

| Макс. процессора Тактовая частота | от 10 МГц до 100 МГц |

| Ширина данных | 32 бита (33 бита в расширенной архитектуре) |

| Физические характеристики | |

| Ядра |

|

Intel i960 80960 (или RISC ) представлял , который стал на базе собой микропроцессор популярным в начале 1990-х годов как встроенный микроконтроллер . Он стал самым продаваемым процессором в этом сегменте наряду с конкурирующим процессором AMD 29000 . [3] Несмотря на успех, Intel прекратила продавать i960 в конце 1990-х годов в результате соглашения с DEC , согласно которому Intel получила права на производство процессоров StrongARM . Процессор продолжает использоваться в некоторых военных приложениях.

Источник

[ редактировать ]

Разработка i960 была начата в ответ на провал конструкции Intel iAPX 432 в начале 1980-х годов. iAPX 432 был предназначен для непосредственной поддержки языков высокого уровня, поддерживающих тегированную , защищенную , на аппаратном со сборкой мусора память , таких как Ada и Lisp уровне. Из-за сложности набора команд, многокристальной реализации и недостатков конструкции iAPX 432 был очень медленным по сравнению с другими процессорами своего времени.

В 1984 году Intel и Siemens начали совместный проект, получивший название BiiN , по созданию высокопроизводительной, отказоустойчивой объектно-ориентированной компьютерной системы, полностью запрограммированной на Ada. Многие из первоначальных членов команды i432 присоединились к этому проекту, хотя новый ведущий архитектор, Гленфорд Майерс был привлечен из IBM . Предполагаемым рынком для систем BiiN были пользователи компьютеров с высокой надежностью, такие как банки, промышленные системы и атомные электростанции.

Основным вкладом Intel в систему BiiN стал новый дизайн процессора, созданный под влиянием концепции защищенной памяти i432. Новый дизайн должен был включать ряд функций, позволяющих повысить производительность и избежать проблем, которые привели к провалу i432. Первые процессоры 960 вступили в заключительную стадию разработки, известную как «вывод на пленку» , в октябре 1985 года и в том же месяце были отправлены в производство, а первые работающие чипы поступили в конце 1985 — начале 1986 года.

Усилия BiiN в конечном итоге провалились из-за рыночных сил, и 960 остался без использования. Майерс попытался сохранить проект, извлекая несколько подмножеств полнофункциональной архитектуры, созданной для системы BiiN. Он пытался убедить руководство Intel продавать i960 (тогда еще известный как «P7») как процессор общего назначения вместо Intel 80286 и i386 (которые были сняты с производства в том же месяце, что и первый i960). а также развивающийся рынок RISC для систем Unix , включая предложение Стиву Джобсу использовать его в системе NeXT . Майерсу не удалось убедить руководство Intel поддержать i960 в качестве процессора общего назначения или Unix, но этот чип нашел готовый рынок для первых высокопроизводительных 32-битных встраиваемых систем.

Ведущим архитектором i960 был по суперскалярности специалист Фред Поллак , который также был ведущим инженером Intel iAPX 432 и ведущим разработчиком чипа i686, Pentium Pro . [4]

Архитектура

[ редактировать ]Семейство i960 включает четыре различные архитектуры, предназначенные для восходящей двоичной совместимости: [5]

- Базовая архитектура представляет собой RISC-подобное ядро.

- Числовая архитектура добавляет плавающую запятую

- Защищенная архитектура добавляет управление страничной памятью, защиту супервизора/пользователя, строковые инструкции, планирование процессов, межпроцессное взаимодействие для ОС и симметричную многопроцессорную обработку.

- Расширенная архитектура добавляет защиту объектов и межпроцессное взаимодействие для приложений.

В первоначальной версии 80960KA поддерживал архитектуру Core, 80960KB поддерживал числовую архитектуру, 80960MC поддерживал защищенную архитектуру, а 80960XA поддерживал расширенную архитектуру.

Чтобы избежать проблем с производительностью, от которых страдал i432, центральная архитектура набора команд i960 была построена на RISC. В расширенной архитектуре подсистема памяти имела ширину 33 бита — для размещения 32-битного слова и бита «тега» для реализации аппаратной защиты памяти. Во многих отношениях i960 следовал оригинальному дизайну RISC Беркли , особенно в использовании окон регистров - количества кэшей для каждой подпрограммы, зависящего от реализации, что позволяло выполнять быстрые вызовы подпрограмм. Конкурирующая разработка Стэнфордского университета , MIPS , не использовала эту систему, вместо этого полагаясь на компилятор для генерации оптимального вызова подпрограммы и кода возврата. Как и большинство 32-битных моделей, i960 имеет плоское 32-битное пространство памяти без сегментации памяти , за исключением архитектуры Extended, которая может поддерживать до 2 26 «объекты», каждый до 2 32 размер в байтах. [6] Архитектура i960 также предполагала суперскалярную реализацию, при которой инструкции одновременно отправлялись более чем в один блок процессора.

вариант i960

[ редактировать ]80960MC

[ редактировать ]i960MC включал в себя все функции оригинальной системы BiiN; но они просто не были упомянуты в спецификациях, что привело к некоторым [ ВОЗ? ] задаться вопросом, почему i960MC был таким большим и имел так много контактов — 53 из 132 [7] - с надписью «нет соединения». Более поздние версии i960, такие как серия 80960Jx, имеют более типичное количество «не подключаться», используют больше контактов питания и заземления и вместо этого имеют дополнительные контакты ввода-вывода. [8] Однако эти контакты «без подключения» на самом деле не подключены внутри и не связаны с набором функций BiiN — внутри кремниевого кристалла нет контактных площадок для них. [9]

80960MC содержит встроенный блок управления памятью и поддерживает отказоустойчивые системы в сочетании с модулем расширения шины Intel M82965. Оба чипа соответствуют стандарту MIL-STD-883C . Оба чипа стали доступны в первом квартале 1989 года по цене 2400 и 1700 долларов США соответственно. Образцы расширенных температур также стали доступны в августе 1988 года. [10]

Он содержит 32 32-битных регистра, 512-байтовый кэш инструкций, кэш кадров стека , высокоскоростную 32-битную мультиплексированную пакетную шину и контроллер прерываний. [11] Он также имеет 256 векторов прерываний и 32 уровня приоритета прерываний. [10]

80960ХА

[ редактировать ]80960XA — это военный представитель семейства i960, реализующий расширенную архитектуру, расширенную версию военного 80960MC. Он поддерживает объектно-ориентированное программирование с аппаратным 33-м битом тега Capability . Он поддерживает 32-битный стандарт ISA Объединенной промышленной рабочей группы по авионике (JIAWG). [5]

80960КА, 80960КБ

[ редактировать ]Версия ядра RISC без управления памятью или FPU стала i960KA, а ядро RISC с FPU — i960KB. Однако внутри версии были идентичны — отличалась только маркировка. Это означало, что процессоры были намного больше, чем необходимо для «фактически поддерживаемых» наборов функций, и, как следствие, их производство было дороже, чем нужно.

Эти процессоры содержат более 350 000 транзисторов. Эти процессоры могут выполнять около 7,5 VAX MIPS . Версия 80960 КБ совместима со стандартом IEEE 754 и может выполнять до 4 MegaWhetstones. Оба процессора доступны с частотой 16 и 20 МГц с использованием технологии CHMOS-III . Оба процессора упакованы в 132-PGA . Версия 80960KA доступна по цене 230 долларов США, а версия 80960KB — по 390 долларов США в количестве 100 штук соответственно. [11]

i960KA стал успешным как недорогой 32-битный процессор для рынка лазерных принтеров, а также для ранних графических терминалов и других встроенных приложений. Его успех окупился за будущие поколения, у которых не было сложной подсистемы памяти.

80960CA, 80960CF

[ редактировать ]The i960CA был анонсирован в июле 1989 года. Он имел недавно разработанное суперскалярное RISC-ядро и добавлял необычный адресуемый встроенный кэш, но не имел FPU и MMU, поскольку был предназначен для высокопроизводительных встроенных приложений. i960CA широко известен [12] Это была первая однокристальная суперскалярная реализация RISC. Серия C включала только одно АЛУ, но могла одновременно отправлять и выполнять арифметическую инструкцию, обращение к памяти и инструкцию ветвления, а также поддерживать две инструкции за цикл при определенных обстоятельствах. Первые выпущенные версии работали на частоте 33 МГц, и Intel рекламировала этот чип как способный 66 MIPS. Микроархитектура i960CA была разработана в 1987–1988 годах и официально анонсирована 12 сентября 1989 года.

Позже, в мае 1992 года, появился i960CF, который включал кэш инструкций большего размера (4 КБ вместо 1 КБ) и добавлял 1 КБ кэша данных, но все еще не имел FPU или MMU.

80960MX

[ редактировать ]80960MX — это суперскалярная реализация расширенной архитектуры, выполняющая до трех инструкций за такт для устойчивой производительности 25 VAX MIPS. [13] Он реализовал 32-битный стандарт ISA Объединенной промышленной рабочей группы по авионике (JIAWG). Первоначально он был упакован в керамическую решетку из 348 выводов, а затем поставлялся в виде голого кристалла. i960 MX поддерживает объектно-ориентированное программирование. 33-й бит тега различает 32-битное слово данных и 32-битный указатель на память. Это запрещало подделку указателей на защищенные области памяти.

80960Jx

[ редактировать ]80960Jx — процессор для встроенных приложений. Он имеет 32-битную мультиплексированную шину адреса/данных, кэш инструкций и данных, 1 КБ встроенной оперативной памяти, контроллер прерываний и два независимых 32-битных таймера. Функции тестирования 80960Jx включали режим ONCE (эмуляция внутри цепи) и граничное сканирование ( JTAG ).

80960HA, 80960HD, 80960HT

[ редактировать ]Процессоры 80960Hx обеспечивали повышенную производительность по сравнению с вариантами Cx за счет умножения тактовой частоты, большего кэша инструкций 16 КБ и кеша данных 4 КБ, а также GMU. (Защищенный блок памяти). Вариант HD имел внутреннее умножение тактовой частоты в 2 раза, а версия HT имел 3-кратное умножение тактовой частоты, что позволяло повысить производительность без изменения скорости внешней шины.

80960ВХ

[ редактировать ]Анонсированный в октябре 1998 года процессор i960VH Embedded-PCI имел 32-разрядную шину PCI с частотой 33 МГц и процессорное ядро i960JT с частотой 100 МГц. Ядро также имело 16 КБ кэша инструкций, 4 КБ кэша данных и 1 КБ встроенной оперативной памяти. Другие основные функции включали два 32-битных таймера, программируемый контроллер прерываний, интерфейс I²C и двухканальный контроллер DMA.

80960Rx

[ редактировать ]Процессоры 80960Rx были обозначены как процессоры ввода-вывода и включали реализацию шины PCI (2.1 или 2.2 в зависимости от варианта), а также ядро 80960Jx. Их можно использовать на материнских платах для реализации встроенного устройства PCI, а также на картах расширения PCI. В вариантах RM/RN/RS использовалось ядро JT с 3-кратным умножением шины на ядро для достижения внутренней тактовой частоты 100 МГц, тогда как в варианте RD использовалось ядро JF с 2-кратным умножением для достижения 66 МГц. Вариант RP имел ядро JF, работавшее на частоте шины 33 МГц.

Технические характеристики варианта

[ редактировать ]| Номер модели | Частота ядра | Частота автобуса | Множитель | iCache | dCache | Напряжение | Розетка |

|---|---|---|---|---|---|---|---|

| 80960MC | 20,25 МГц | 20,25 МГц | 1,0x | 0,5 Кбайт | никто | 5.0 V | ПГА-132 |

| 80960SA | 10,12,16,20 МГц | 10,12,16,20 МГц | 1,0x | 0,5 Кбайт | никто | 5.0 V | 80-PQFP, 84-PLCC |

| 80960СБ | 10,16 МГц | 10,16 МГц | 1,0x | 0,5 Кбайт | никто | 5.0 V | 80-PQFP, 84-PLCC |

| 80960КА | 10,20,25 МГц | 10,20,25 МГц | 1,0x | 0,5 Кбайт | никто | 5.0 V | 132-ПКФП, 132-ПГА |

| 80960 КБ | 16,20,25 МГц | 16,20,25 МГц | 1,0x | 0,5 Кбайт | никто | 5.0 V | 132-ПКФП, 132-ПГА |

| 80960CA | 16,25,33 МГц | 16,25,33 МГц | 1,0x | 1 Кбайт | никто | 5.0 V | 168-ПГА, 196-ПКФП |

| 80960CF | 25,33,40 МГц | 25,33,40 МГц | 1,0x | 4 Кбайт | 1 Кбайт | 5.0 V | 168-ПГА, 196-ПКФП |

| Номер модели | Частота ядра | Частота автобуса | Множитель | iCache | dCache | Напряжение | Розетка |

|---|---|---|---|---|---|---|---|

| 80960JA | 16,25,33 МГц | 16,25,33 МГц | 1,0x | 2 Кбайт | 1 Кбайт | 3.3 V | 132-ПКФП, 132-ПГА |

| 80960JF | 25,33 МГц | 25,33 МГц | 1,0x | 4 Кбайт | 2 Кбайт | 3.3 V | 132-ПКФП, 132-ПГА |

| 80960JD | 33,40,50,66 МГц | 16,20,25,33 МГц | 2,0x | 4 Кбайт | 2 Кбайт | 3.3 V | 132-ПКФП, 132-ПГА |

| 80960JS | 25,33 МГц | 25,33 МГц | 1,0x | 16 Кбайт | 4 Кбайт | 3.3 V | 132-PQFP, 132-PGA, 196-MPBGA |

| 80960JC | 50,66 МГц | 25,33 МГц | 2,0x | 16 Кбайт | 4 Кбайт | 3.3 V | 132-PQFP, 132-PGA, 196-MPBGA |

| 80960JT | 75100 МГц | 25,33 МГц | 3,0x | 16 Кбайт | 4 Кбайт | 3.3 V | 132-PQFP, 132-PGA, 196-MPBGA |

| 80960HA | 25,33,40 МГц | 25,33,40 МГц | 1,0x | 16 Кбайт | 8 Кбайт | 3.3 V | 168-ПГА, 208-PQ4 |

| 80960HD | 50,66,80 МГц | 25,33,40 МГц | 2,0x | 16 Кбайт | 8 Кбайт | 3.3 V | 168-ПГА, 208-PQ4 |

| 80960HT | 75 МГц | 25 МГц | 3,0x | 16 Кбайт | 8 Кбайт | 3.3 V | 168-ПГА, 208-PQ4 |

| Номер модели | Частота ядра | Частота автобуса | Множитель | iCache | dCache | Версия PCI | Напряжение | Розетка |

|---|---|---|---|---|---|---|---|---|

| 80960РП | 33 МГц | 33 МГц | 1,0x | 4 КБ | 2 КБ | PCI 2.1 | 3.3 V | 352-ПБГА |

| 80960РД | 66 МГц | 33 МГц | 2,0x | 4 КБ | 2 КБ | PCI 2.1 | 3.3 V | 352-ПБГА |

| 80960ВХ | 100 МГц | 33 МГц | 3,0x | 16 КБ | 4 КБ | PCI 2.1 | 3.3 V | 324-ПБГА |

| 80960РМ/Н | 100 МГц | 33 МГц | 3,0x | 16 КБ | 4 КБ | PCI 2.1 | 3.3 V | 540-ПБГА |

| 80960РС | 100 МГц | 33 МГц | 3,0x | 16 КБ | 4 КБ | PCI 2.2 | 3.3 V | 540-ПБГА |

| 80302/3 | 100 МГц | 66 МГц | 1,5x | 16 КБ | 4 КБ | PCI 2.2 | 3.3 V | 540-ПБГА |

- Выстрелы

-

Интел 80960MX

-

Интел 80960КА

-

Интел 80960СА

-

Интел 80960CA

-

Интел 80960CF

-

Интел 80960JA

-

Интел 80960HD

Конец разработки

[ редактировать ]Intel попыталась поддержать i960 на рынке контроллеров устройств ввода-вывода с помощью стандарта I2O , но это не принесло большого успеха, и работа по проектированию в конечном итоге была прекращена. К середине 1990-х годов соотношение цена/производительность отставало от конкурирующих чипов более поздних моделей, и Intel так и не выпустила версию с пониженным энергопотреблением, которую можно было бы использовать в системах с батарейным питанием.

В 1990 году команда i960 была переведена во «вторую команду», параллельно работавшую над будущими реализациями i386 , в частности над процессором P6, который позже стал Pentium Pro . Проект i960 был передан другой, меньшей команде разработчиков, что, по сути, обеспечило завершение его разработки.

Текущий статус

[ редактировать ]

Некоторые процессоры ввода-вывода i960, такие как 80303, включают встроенный аппаратный механизм XOR для алгоритмов RAID . [14] Они используются в качестве контроллеров для высокопроизводительных карт хост-адаптеров с поддержкой RAID , SCSI -дисковых массивов, а также высокопроизводительных SCSI и DSSI от Digital Equipment/Compaq/HP и, в конечном итоге, Fibre Channel автономных RAID-массивов серии HSx. контроллеры. [15] [16]

Чип i960RS также используется в контроллере Adaptec AAR-2400A, который использует четыре обычных параллельных диска ATA для создания доступной RAID-5 отказоустойчивой системы хранения данных с защитой для небольших ПК-серверов и рабочих станций.

i960 также использовался в некоторых коммутаторах Brocade Fibre Channel для запуска операционной системы Fabric .

Архитектура i960 также используется в игровых автоматах . В настоящее время они присутствуют в IGT семействе Stepper S2000 и видео i960 компании . Он также использовался в качестве основного процессора Sega знаменитой Model 2 серии аркадных плат .

i960 . Сообщается , что легкий боевой самолет HAL Tejas MMR (многорежимный радар) ВВС Индии использует HAL Tejas был принят на вооружение в 2015 году.

Сообщается, что Индийская организация космических исследований (ISRO) использует этот чип в бортовых компьютерах своих ракет-носителей.

Процессор i960 также используется в интерфейсных платах системы автоматической радиолокационной прокладки (ARPA) в радарах от Kelvin Hughes .

Чип использовался на некоторых HP X-Terminals .

Некоторые RAID-контроллеры SATA используют процессор Intel 80303 IOP (интеллектуальный процессор ввода-вывода), который объединяет мост PCI-PCI, контроллер памяти и ядро ЦП 80960JT-100.

Чип использовался в модеме Alcatel-Lucent 1000 ADSL- широкополосном . [17]

Ссылки

[ редактировать ]- ^ Смит, Тони (18 мая 2006 г.). «Intel обналичивает древние чипы» . Регистр . Проверено 24 января 2020 г.

- ^ «Новое семейство чипов Intel» . Нью-Йорк Таймс . 6 апреля 1988 года . Проверено 4 декабря 2023 г.

- ^ Терли, Джим (11 января 2002 г.). «Встроенные процессоры, часть первая» . PCMag.com . Проверено 8 сентября 2018 г.

- ^ Дворжак, Джон К. (2008). «Что бы ни случилось с iAPX432 — чипом мечты Intel» . Дворжак.org . Проверено 8 сентября 2018 г.

- ^ Перейти обратно: а б «80960XA Встроенный 32-битный микропроцессор с 33-м битом тега для поддержки объектно-ориентированного программирования и безопасности данных» (PDF) . Интел.

- ^ Справочное руководство по архитектуре ЦП BiiN (PDF) . БииН. Июль 1998 года.

- ^ «80960MC ВСТРОЕННЫЙ 32-БИТЫЙ МИКРОПРОЦЕССОР СО ВСТРОЕННЫМ БЛОКОМ С ПЛАВАЮЩЕЙ ТОЧКОЙ И БЛОКОМ УПРАВЛЕНИЯ ПАМЯТЬЮ» (PDF) . Интел . 1990. стр. 24–29 . Проверено 5 апреля 2023 г.

- ^ «80960JA/JF/JD/JT 3,3 В ВСТРОЕННЫЙ 32-БИТЫЙ МИКРОПРОЦЕССОР» (PDF) . Интел . Март 1998 г., стр. 22–25 . Проверено 5 апреля 2023 г.

- ^ Ширрифф, Кен (1 июля 2023 г.). «Сложная история RISC-процессора Intel i960» . Проверено 1 июля 2023 г.

Исходные чипы i960 (KA/KB/MC/XA) имеют большое количество несоединённых контактов (отмечено NC в таблице данных). [...] проверка таблиц данных показывает, что все четыре чипа имеют одинаковую распиновку; пины не подключены только в более продвинутых версиях. Во-вторых, взгляд на упакованный чип (ниже) объясняет, почему так много контактов не соединены: большая часть чипа не имеет контактных площадок, поэтому контакты не к чему подключать.

- ^ Перейти обратно: а б Льюнес, Энн, «Выдающиеся процессоры Intel 80960 и 80376 среди 32-битных систем», Intel Corporation, Microcomputer Solutions, июль/август 1988 г., стр. 2

- ^ Перейти обратно: а б Ормсби, Джон, редактор, «Новые продукты: компоненты: Intel входит в мир 32-битного встроенного управления», корпорация Intel, Microcomputer Solutions, май/июнь 1988 г., стр. 9

- ^ Шен, Джон Пол; Липасти, Микко Х. (2003). Современный дизайн процессоров: основы суперскалярных процессоров (бета-изд.). МакГроу Хилл. п. 328. ИСБН 0-07-282968-0 .

- ^ «Процессор i960 MX». Справочник по военной и специальной продукции . Интел. 1993. стр. с 11–40 по 11–89.

- ^ «Технические данные процессора ввода-вывода Intel 80960RM» (PDF) . .

- ^ «Заметки семинара по платформе Storageworks» . Архивировано из оригинала 25 апреля 2012 года.

- ^ «Intel расширяет семейство строительных блоков ввода-вывода, включив в него интегрированный комплект Intel для проектирования RAID, программное обеспечение и контроллер» (пресс-релиз). САНТА-КЛАРА, Калифорния: Intel . 19 января 2000 г. Архивировано из оригинала 29 августа 2020 г. Проверено 29 августа 2020 г.

- ^ «Изображение печатной платы ADSL-модема Alcatel 1000» . Security.sdsc.edu . Проверено 24 сентября 2018 г.