Разработка интегральных схем

Эта статья включает список общих ссылок , но в ней отсутствуют достаточные соответствующие встроенные цитаты . ( Март 2019 г. ) |

Проектирование интегральных схем , проектирование полупроводников , проектирование микросхем или проектирование ИС — это подобласть электроники , охватывающая конкретные методы логики и проектирования схем, необходимые для проектирования интегральных схем или ИС. ИС состоят из миниатюрных электронных компонентов, встроенных в электрическую сеть на монолитной полупроводниковой подложке методом фотолитографии .

Проектирование ИС можно разделить на широкие категории: проектирование цифровых и аналоговых ИС. Проектирование цифровых ИС направлено на производство таких компонентов, как микропроцессоры , FPGA , память ( ОЗУ , ПЗУ и флэш-память ) и цифровые ASIC . Цифровой дизайн фокусируется на логической правильности, максимальной плотности схем и размещении схем таким образом, чтобы сигналы синхронизации и синхронизации распределялись эффективно. Компания Analog IC Design также специализируется на проектировании силовых ИС и разработке радиочастотных ИС. Аналоговая конструкция ИС используется при проектировании операционных усилителей , линейных регуляторов , систем фазовой автоподстройки частоты , генераторов и активных фильтров . Аналоговый дизайн больше связан с физикой полупроводниковых устройств, такой как усиление, согласование, рассеиваемая мощность и сопротивление . Точность усиления и фильтрации аналогового сигнала обычно имеет решающее значение, и в результате аналоговые ИС используют активные устройства большей площади, чем цифровые конструкции, и обычно имеют меньшую плотность схемы.

Современные микросхемы чрезвычайно сложны. Средний чип настольного компьютера по состоянию на 2015 год содержит более 1 миллиарда транзисторов. Правила относительно того , что можно и что нельзя производить, также чрезвычайно сложны. Общие процессы ИК 2015 года насчитывают более 500 правил. Более того, поскольку сам производственный процесс не полностью предсказуем, конструкторам приходится учитывать его статистический характер. Сложность современного проектирования ИС, а также потребность рынка в быстром производстве проектов привели к широкому использованию инструментов автоматизированного проектирования в процессе проектирования ИС. Конструкция некоторых процессоров стала настолько сложной, что ее трудно полностью протестировать, и это вызвало проблемы у крупных поставщиков облачных услуг. [1] Короче говоря, проектирование ИС с использованием программного обеспечения EDA — это проектирование, тестирование и проверка инструкций, которые ИС должна выполнять. Искусственный интеллект был продемонстрирован при проектировании чипов для создания макетов чипов, которые представляют собой расположение стандартных ячеек и макроблоков в чипе. [2]

Основы

[ редактировать ]Проектирование интегральных схем включает в себя создание электронных компонентов, таких как транзисторы , резисторы , конденсаторы , и соединение этих компонентов на полупроводниковом элементе, обычно кремниевом . Необходим метод изоляции отдельных компонентов, образующихся в подложке, поскольку кремний подложки является проводящим и часто образует активную область отдельных компонентов. Двумя распространенными методами являются изоляция pn-перехода и диэлектрическая изоляция . Необходимо уделять внимание рассеянию мощности транзисторов и сопротивлению межсоединений, а также плотности тока межсоединений, контактов и переходных отверстий, поскольку микросхемы содержат очень маленькие устройства по сравнению с дискретными компонентами, где такие проблемы не являются проблемой. Электромиграция в металлических соединениях и электростатического разряда повреждение мелких компонентов от также вызывают беспокойство. Наконец, физическая компоновка определенных подблоков схемы обычно имеет решающее значение для достижения желаемой скорости работы, для отделения шумных частей ИС от тихих частей, для балансировки эффектов выделения тепла в ИС или для облегчения размещение соединений со схемами вне микросхемы.

Процесс проектирования

[ редактировать ]

Типичный цикл проектирования микросхем включает в себя несколько этапов:

- Спецификация системы

- Технико-экономическое обоснование и оценка размеров матрицы

- Функциональный анализ

- Архитектурное или системное проектирование

- Логический дизайн

- Аналоговый дизайн, моделирование и компоновка

- Цифровое проектирование и моделирование

- Системное моделирование, эмуляция и проверка

- Схемотехника

- Синтез цифрового дизайна

- Проектирование для тестирования и автоматического создания тестовых шаблонов

- Дизайн ради технологичности

- Физический дизайн

- Планировка этажа

- Место и маршрут

- Паразитарное извлечение

- Физическая проверка и подписание

- Статическое время

- Совместное моделирование и синхронизация

- Подготовка данных маски (постобработка макета)

- Отделка чипа с помощью ленты

- Расположение сетки

- Подготовка макета к маске

- Изготовление прицельной сетки

- Изготовление фотомаски

- Изготовление пластин

- Упаковка

- Тест

- Пост-кремниевая проверка и интеграция

- Характеристика устройства

- Подправить (при необходимости)

- Развертывание чипа

- Создание таблицы данных (обычно PDF- файла)

- Нарастить

- Производство

- Анализ доходности/гарантийный анализ надежности

- Анализ отказов по любым возвратам

- Планируйте создание чипа следующего поколения, используя, если возможно, производственную информацию.

Сфокусированные ионные пучки могут использоваться во время разработки чипов для установления новых связей в чипе. [3] [4]

Краткое содержание

[ редактировать ]Грубо говоря, проектирование цифровых микросхем можно разделить на три части.

- Проектирование на уровне электронной системы : на этом этапе создается функциональная спецификация пользователя. Пользователь может использовать различные языки и инструменты для создания этого описания. Примеры включают модель C / C++ , VHDL , SystemC , SystemVerilog модели уровня транзакций , Simulink и MATLAB .

- Проектирование RTL: на этом этапе пользовательская спецификация (то, что пользователь хочет от чипа) преобразуется в описание уровня передачи регистров (RTL). RTL описывает точное поведение цифровых схем на кристалле, а также соединения со входами и выходами.

- Проектирование физической схемы . На этом этапе используется RTL и библиотека доступных логических элементов ( стандартная библиотека ячеек ) и создается проект микросхемы. Этот шаг включает в себя использование редактора компоновки микросхем , планировку и планировку этажа, выяснение того, какие ворота использовать, определение мест для них и их соединение (синтез тактовой синхронизации, маршрутизация).

Обратите внимание, что второй этап — проектирование RTL — отвечает за правильную работу чипа. Третий шаг, физическое проектирование, вообще не влияет на функциональность (если все сделано правильно), но определяет, насколько быстро работает чип и сколько он стоит.

Стандартная ячейка обычно представляет собой один логический элемент , диод или простые логические компоненты, такие как триггеры или логические элементы с несколькими входами. [5] Использование стандартных ячеек позволяет разделить конструкцию чипа на логический и физический уровни. Компания, не имеющая собственных производственных мощностей, обычно работает только над логическим проектом чипа, определяя, как соединяются ячейки и функциональность чипа, при этом следуя правилам проектирования, установленным на литейном заводе, на котором будет изготовлен чип, в то время как физический дизайн чипа, Сами ячейки обычно изготавливаются на литейном заводе и включают в себя физику транзисторных устройств и то, как они соединяются для формирования логического элемента. Стандартные ячейки позволяют быстрее проектировать и модифицировать микросхемы в соответствии с требованиями рынка, но за это приходится платить меньшей плотностью транзисторов в чипе и, следовательно, увеличением размеров кристалла. [5]

Литейные заводы поставляют библиотеки стандартных ячеек компаниям, не имеющим собственных производственных мощностей, для целей проектирования и для обеспечения возможности изготовления их конструкций на мощностях литейного завода. Комплект проектирования процесса (PDK) может быть предоставлен литейным заводом и может включать в себя стандартную библиотеку ячеек, а также спецификации ячеек и инструменты для проверки конструкции компании, не имеющей собственных производственных мощностей, на соответствие правилам проектирования, установленным литейным заводом, а также для моделирования это с использованием литейных ячеек. PDK могут предоставляться по соглашениям о неразглашении. Макросы/Макроячейки/Макроблоки, [6] Массивы макроячеек и IP-блоки обладают большей функциональностью, чем стандартные ячейки, и используются аналогично. Существуют мягкие макросы и жесткие макросы. Стандартные ячейки обычно располагаются после рядов стандартных ячеек.

Жизненный цикл проекта

[ редактировать ]Процесс разработки интегральной схемы (ИС) начинается с определения требований к продукту, проходит этапы определения архитектуры, реализации, внедрения и, наконец, производства. Ниже описаны различные этапы процесса разработки интегральных схем. Хотя этапы представлены здесь в простой форме, на самом деле существуют итерации , и эти шаги могут повторяться несколько раз.

Требования

[ редактировать ]Прежде чем можно будет определить архитектуру , необходимо определить некоторые цели продукта высокого уровня. Требования , потребности обычно создаются межфункциональной командой, которая учитывает рыночные возможности клиентов, осуществимость и многое другое. Результатом этого этапа должен стать документ с требованиями к продукту .

Архитектура

[ редактировать ]Архитектура определяет фундаментальную структуру , цели и принципы продукта. Он определяет концепции высокого уровня и внутреннюю ценность продукта. Архитектурные команды принимают во внимание множество переменных и взаимодействуют со многими группами. Люди, создающие архитектуру, обычно имеют значительный опыт работы с системами в той области, для которой создается архитектура. Результатом этапа архитектуры является архитектурная спецификация .

Микроархитектура

[ редактировать ]Микроархитектура — это шаг ближе к аппаратному обеспечению. Он реализует архитектуру и определяет конкретные механизмы и структуры для достижения этой реализации. Результатом этапа микроархитектуры является спецификация микроархитектуры, описывающая методы, используемые для реализации архитектуры.

Выполнение

[ редактировать ]На этапе реализации создается сам проект с использованием микроархитектурной спецификации в качестве отправной точки. Это включает в себя определение и разделение низкого уровня, написание кода , ввод схем и проверку. Этот этап заканчивается проекта завершением разработки .

Грудь вверх

[ редактировать ]После того, как проект создан, записан на пленку и изготовлен, получают фактическое оборудование, «первый кремний», который отправляется в лабораторию, где он проходит доработку . Подготовка — это процесс включения, тестирования и определения характеристик конструкции в лаборатории. Выполняются многочисленные тесты , начиная с очень простых тестов, таких как проверка включения устройства, до гораздо более сложных тестов, которые пытаются подвергнуть деталь различным нагрузкам. Результатом этапа подготовки является документирование данных характеристик (насколько хорошо деталь работает в соответствии со спецификацией) и ошибок (неожиданное поведение).

Производство

[ редактировать ]Производство — это задача перевода дизайна из инженерного состояния в серийное производство. Несмотря на то, что конструкция может успешно соответствовать спецификациям продукта в лаборатории на этапе разработки, инженеры-разработчики сталкиваются со многими проблемами при попытке массового производства этих конструкций. ИК необходимо довести до объемов производства с приемлемым выходом. Целью этапа производства является достижение объемов массового производства при приемлемой стоимости.

Поддержание

[ редактировать ]Как только конструкция станет зрелой и достигнет массового производства, ее необходимо поддерживать. Процесс необходимо постоянно контролировать и быстро решать проблемы, чтобы избежать значительного влияния на объемы производства. Целью устойчивого развития является поддержание объемов производства и постоянное снижение затрат до тех пор, пока срок службы продукта не закончится .

Процесс проектирования

[ редактировать ]Микроархитектура и проектирование на уровне системы

[ редактировать ]Первоначальный процесс проектирования чипа начинается с проектирования на уровне системы и планирования микроархитектуры. В компаниях, занимающихся разработкой микросхем, руководство и часто аналитики составляют предложение для группы разработчиков, которая приступит к разработке нового чипа, подходящего для определенного отраслевого сегмента. На этом этапе дизайнеры верхнего уровня встретятся, чтобы решить, как чип будет работать функционально. На этом этапе определяются функциональность и дизайн микросхемы. Разработчики ИС наметят функциональные требования, стенды для проверки и методологии тестирования для всего проекта, а затем превратят предварительный проект в спецификацию системного уровня, которую можно будет моделировать с помощью простых моделей с использованием таких языков, как C++ и MATLAB, а также инструментов эмуляции. Для чистых и новых проектов на этапе проектирования системы планируются набор команд и операции, а в большинстве микросхем существующие наборы команд модифицируются для обеспечения новых функций. Проектирование на этом этапе часто представляет собой такие утверждения, как кодирование в MP3 формате или реализация IEEE арифметика с плавающей запятой . На более поздних стадиях процесса проектирования каждое из этих невинных на первый взгляд утверждений разрастается до сотен страниц текстовой документации.

РТЛ-дизайн

[ редактировать ]После согласования проекта системы проектировщики RTL затем реализуют функциональные модели на языке описания оборудования, таком как Verilog , SystemVerilog или VHDL . Используя компоненты цифрового проектирования, такие как сумматоры, сдвигатели и конечные автоматы, а также концепции компьютерной архитектуры, такие как конвейеризация, суперскалярное выполнение и предсказание ветвей , разработчики RTL разбивают функциональное описание на аппаратные модели компонентов на кристалле, работающих вместе. Каждое из простых утверждений, описанных в проекте системы, может легко превратиться в тысячи строк RTL -кода, поэтому крайне сложно проверить, что RTL будет поступать правильно во всех возможных случаях, которые может ему бросить пользователь. .

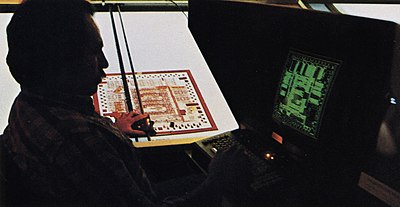

Чтобы уменьшить количество функциональных ошибок, отдельная группа проверки оборудования возьмет на себя RTL и спроектирует испытательные стенды и системы, чтобы проверить, что RTL действительно выполняет одни и те же шаги при множестве различных условий, классифицируемых как область функциональной проверки . Используется множество методов, ни один из них не идеален, но все они полезны — обширное логическое моделирование , формальные методы , аппаратная эмуляция , lint проверка кода в стиле , покрытие кода и так далее. Проверка, подобная той, что выполняется с помощью эмуляторов, может выполняться в FPGA или специальных процессорах. [7] [8] и эмуляция заменила симуляцию. Первоначально моделирование проводилось путем моделирования логических элементов в микросхемах, но позже вместо этого были смоделированы RTL в микросхемах. [9] Моделирование до сих пор используется при создании аналоговых микросхем. [10] Платформы прототипирования используются для запуска программного обеспечения на прототипах конструкции микросхемы, пока она находится в стадии разработки с использованием FPGA, но они медленнее повторяются или модифицируются и не могут использоваться для визуализации аппаратных сигналов в том виде, в каком они будут выглядеть в готовом проекте. [11]

Малейшая ошибка может сделать весь чип бесполезным или даже хуже. Знаменитая ошибка Pentium FDIV привела к тому, что результаты деления были неверными максимум на 61 часть на миллион, причем в случаях, которые происходили очень редко. Никто этого даже не заметил, пока чип не находился в производстве несколько месяцев. Тем не менее, Intel была вынуждена предложить бесплатную замену каждого проданного чипа до тех пор, пока они не исправят ошибку, за 475 миллионов долларов США. [ нужна ссылка ]

Физический дизайн

[ редактировать ]

RTL — это всего лишь поведенческая модель фактической функциональности того, с чем должен работать чип. Он не имеет никакой связи с физическим аспектом того, как чип будет работать в реальной жизни с точки зрения материалов, физики и электротехники. По этой причине следующим шагом в процессе проектирования микросхемы, этапом физического проектирования , является отображение RTL в реальных геометрических представлениях всех электронных устройств, таких как конденсаторы, резисторы, логические элементы и транзисторы, которые будут установлены на кристалле.

Основные этапы физического проектирования перечислены ниже. На практике не существует прямого прогресса: требуется значительное количество итераций, чтобы обеспечить одновременное достижение всех целей. Это сложная проблема сама по себе, называемая закрытием проекта .

- Логический синтез : RTL отображается в список соединений уровня вентиля в целевой технологии чипа.

- Планирование этажа : RTL чипа назначается общим областям чипа, назначаются контакты ввода/вывода (I/O) и размещаются крупные объекты (массивы, ядра и т. д.).

- Размещение : ворота в списке соединений назначаются непересекающимся местам на площади кристалла.

- Уточнение логики/размещения: итеративные логические преобразования и преобразования размещения для устранения ограничений производительности и мощности.

- Вставка тактового сигнала проводка тактового сигнала (обычно деревья тактового сигнала ). : в проект вводится

- Маршрутизация : добавляются провода, соединяющие ворота в списке соединений.

- Оптимизация после подключения: производительности ( закрытие таймингов ), шума ( целостность сигнала ) и выхода ( проектирование с учетом технологичности ). устраняются нарушения

- Проектирование с учетом технологичности : конструкция модифицируется, где это возможно, чтобы сделать ее производство максимально простым и эффективным. Это достигается путем добавления дополнительных переходных отверстий или добавления фиктивных металлических/диффузионных/полислоев, где это возможно, при соблюдении правил проектирования, установленных литейным производством.

- Заключительная проверка: поскольку ошибки обходятся дорого, отнимают много времени и их трудно обнаружить, правилом является тщательная проверка ошибок, обеспечивающая правильность сопоставления с логикой и проверяющая, что производственные правила соблюдаются точно .

- Обработка чипа с помощью Tapeout и создание маски: проектные данные превращаются в фотомаски при подготовке данных маски . [12]

Аналоговый дизайн

[ редактировать ]До появления микропроцессоров и программных средств проектирования аналоговые ИС проектировались с использованием ручных расчетов и деталей технологических наборов. Эти микросхемы представляли собой схемы низкой сложности, например, операционные усилители , обычно включающие не более десяти транзисторов и небольшое количество соединений. Для создания технологичной ИС часто требовался итерационный процесс проб и ошибок и «чрезмерное проектирование» размера устройства. Повторное использование проверенных конструкций позволило создавать все более сложные микросхемы на основе предварительных знаний. Когда в 1970-х годах стала доступна недорогая компьютерная обработка, были написаны компьютерные программы для моделирования схем с большей точностью, чем практический расчет вручную. Первый симулятор аналоговых микросхем назывался SPICE (Программа моделирования с акцентом на интегральные схемы). Инструменты компьютерного моделирования схем обеспечивают большую сложность проектирования микросхем, чем могут достичь ручные расчеты, что делает проектирование аналоговых ASIC практичным.

Поскольку при аналоговом проектировании необходимо учитывать множество функциональных ограничений, ручное проектирование по-прежнему широко распространено сегодня, в отличие от цифрового проектирования, которое в высокой степени автоматизировано, включая автоматическую маршрутизацию и синтез. [13] В результате современные процессы проектирования аналоговых схем характеризуются двумя разными стилями проектирования – сверху вниз и снизу вверх. [14] В нисходящем стиле проектирования используются инструменты оптимизации, аналогичные обычным цифровым потокам. Процедуры «снизу вверх» повторно используют «экспертные знания» с результатом решений, ранее задуманных и зафиксированных в процедурном описании, имитируя решение эксперта. [14] Примером являются генераторы ячеек, такие как PCells .

Борьба с изменчивостью

[ редактировать ]Проблема, наиболее критическая для проектирования аналоговых ИС, связана с вариативностью отдельных устройств, построенных на полупроводниковом кристалле. В отличие от проектирования схем на уровне платы, которое позволяет разработчику выбирать устройства, каждое из которых было протестировано и распределено по значениям, значения устройств на ИС могут варьироваться в широких пределах, что разработчик не контролирует. Например, некоторые резисторы IC могут варьироваться в пределах ±20%, а β встроенного биполярного транзистора может варьироваться от 20 до 100. В новейших процессах КМОП β вертикальных PNP-транзисторов может даже опускаться ниже 1. Чтобы усложнить проектирование, свойства устройства часто варьируются в зависимости от обрабатываемой полупроводниковой пластины. Свойства устройств могут даже существенно различаться в зависимости от каждой отдельной микросхемы из-за градиентов легирования . Основная причина этой изменчивости заключается в том, что многие полупроводниковые устройства очень чувствительны к неконтролируемым случайным отклонениям в процессе. Небольшие изменения во времени диффузии, неравномерность уровней легирования и т. д. могут оказать существенное влияние на свойства устройства.

Некоторые методы проектирования, используемые для уменьшения влияния вариаций устройства: [15]

- Использование соотношений резисторов, которые действительно совпадают, а не абсолютного значения резистора.

- Использование устройств с совпадающими геометрическими формами, чтобы они имели одинаковые вариации.

- Делать устройства большими, чтобы статистические вариации стали незначительной частью общих свойств устройства.

- Сегментация больших устройств, таких как резисторы, на части и их переплетение для устранения отклонений.

- Использование общей схемы устройства центроида для устранения различий в устройствах, которые должны точно совпадать (например, дифференциальная пара транзисторов операционного усилителя ).

Продавцы

[ редактировать ]Тремя крупнейшими компаниями, продающими инструменты автоматизации электронного проектирования, являются Synopsys , Cadence и Mentor Graphics . [16]

См. также

[ редактировать ]- Защита компоновки интегральной схемы

- Проектирование электронных схем

- Автоматизация электронного проектирования

- Проектирование электросетей (ИС)

- Дизайн процессора

- Транзакции IEEE по автоматизированному проектированию интегральных схем и систем

- Многопроектный вафельный сервис

- Стандартная ячейка

Ссылки

[ редактировать ]- ^ «К вашему сведению: сегодняшние компьютерные чипы настолько продвинуты, что они скорее подвижны, чем точны – и вот доказательство» .

- ^ «Теперь Google использует ИИ для разработки чипов, гораздо быстрее, чем инженеры-люди могут выполнить эту работу» . ЗДНет .

- ^ Джейкоб Ридли (26 декабря 2022 г.). «Внутри Intel: вот что нужно для создания передового игрового процессора» . PC Gamer – через www.pcgamer.com.

- ^ Шимпи, Ананд Лал. «Внутри Intel: от кремния к миру» . www.anandtech.com .

- ^ Jump up to: а б Чен, Вай-Кай (3 октября 2018 г.). Справочник по СБИС . ЦРК Пресс. ISBN 978-1-4200-0596-7 .

- ^ Токуда, Т.; Коремацу, Дж.; Симадзу, Ю.; Сакашита, Н.; Кенгаку, Т.; Фугияма, Т.; Оно, Т.; Томисава, О. (7 декабря 1988 г.). «Макросотовый подход к проектированию процессоров СБИС» . Транзакции IEEE по автоматизированному проектированию интегральных схем и систем . 7 (12): 1272–1277. doi : 10.1109/43.16805 — через IEEE Xplore.

- ^ «Cadence представляет Palladium XP II» . 18 февраля 2024 г.

- ^ «Процессоры для эмуляции процессоров: Palladium II | Музей CPU Shack» . 21 октября 2016 г.

- ^ «Эмуляция на основе транзакций» . 24 марта 2024 г.

- ^ «Cadence наносит ответный удар Synopsys новым инструментом моделирования цепей» . 21 мая 2021 г.

- ^ «Первые эмуляторы весны» . 13 апреля 2021 г.

- ^ Й. Лиениг, Й. Шейбле (2020). «Глава 3.3: Данные маски: постобработка макета». Основы топологии электронных схем . Спрингер. стр. 102–110. дои : 10.1007/978-3-030-39284-0 . ISBN 978-3-030-39284-0 . S2CID 215840278 .

- ^ https://www-group.slac.stanford.edu/ais/publicDocs/presentation137.pdf. [ только URL-адрес PDF ]

- ^ Jump up to: а б Й. Лиениг, Й. Шейбле (2020). «Глава 4.6: Процессы аналогового и цифрового проектирования». Основы топологии электронных схем . Спрингер. стр. 151–159. дои : 10.1007/978-3-030-39284-0 . ISBN 978-3-030-39284-0 . S2CID 215840278 .

- ^ Басу, Джойдип (09 октября 2019 г.). «От проектирования до вывода на ленту в технологии производства интегральных схем КМОП SCL 180 нм». Образовательный журнал IETE . 60 (2): 51–64. arXiv : 1908.10674 . дои : 10.1080/09747338.2019.1657787 . S2CID 201657819 .

- ^ «Развитие моделей Multi-CAD» (PDF) . Тенденции рынка IC CAD 2015 . 11 июля 2015 г.

Дальнейшее чтение

[ редактировать ]- Справочник по автоматизации проектирования электронных систем для интегральных схем , автор: Лаваньо, Мартин и Шеффер, ISBN 0-8493-3096-3 Обзор области автоматизации проектирования электроники , одного из основных факторов современного проектирования ИС.