Flash memory

| Computer memory and Computer data storage types |

|---|

| Volatile |

| Non-volatile |

Flash memory is an electronic non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for the NOR and NAND logic gates. Both use the same cell design, consisting of floating gate MOSFETs. They differ at the circuit level depending on whether the state of the bit line or word lines is pulled high or low: in NAND flash, the relationship between the bit line and the word lines resembles a NAND gate; in NOR flash, it resembles a NOR gate.

Flash memory, a type of floating-gate memory, was invented in Toshiba in 1980 and is based on EEPROM technology. Toshiba began marketing flash memory in 1987.[1] EPROMs had to be erased completely before they could be rewritten. NAND flash memory, however, may be erased, written, and read in blocks (or pages), which generally are much smaller than the entire device. NOR flash memory allows a single machine word to be written – to an erased location – or read independently. A flash memory device typically consists of one or more flash memory chips (each holding many flash memory cells), along with a separate flash memory controller chip.

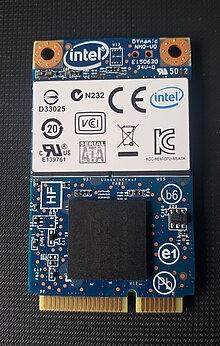

The NAND type is found mainly in memory cards, USB flash drives, solid-state drives (those produced since 2009), feature phones, smartphones, and similar products, for general storage and transfer of data. NAND or NOR flash memory is also often used to store configuration data in digital products, a task previously made possible by EEPROM or battery-powered static RAM. A key disadvantage of flash memory is that it can endure only a relatively small number of write cycles in a specific block.[2]

NOR flash is known for its direct random access capabilities, making it apt for executing code directly. Its architecture allows for individual byte access, facilitating faster read speeds compared to NAND flash. NAND flash memory operates with a different architecture, relying on a serial access approach. This makes NAND suitable for high-density data storage but less efficient for random access tasks. NAND flash is often employed in scenarios where cost-effective, high-capacity storage is crucial, such as in USB drives, memory cards, and solid-state drives (SSDs).

The primary differentiator lies in their use cases and internal structures. NOR flash is optimal for applications requiring quick access to individual bytes, like in embedded systems for program execution. NAND flash, on the other hand, shines in scenarios demanding cost-effective, high-capacity storage with sequential data access.

Flash memory[3] is used in computers, PDAs, digital audio players, digital cameras, mobile phones, synthesizers, video games, scientific instrumentation, industrial robotics, and medical electronics. Flash memory has a fast read access time but it is not as fast as static RAM or ROM. In portable devices, it is preferred to use flash memory because of its mechanical shock resistance since mechanical drives are more prone to mechanical damage.[4]

Because erase cycles are slow, the large block sizes used in flash memory erasing give it a significant speed advantage over non-flash EEPROM when writing large amounts of data. As of 2019,[update] flash memory costs greatly less than byte-programmable EEPROM and had become the dominant memory type wherever a system required a significant amount of non-volatile solid-state storage. EEPROMs, however, are still used in applications that require only small amounts of storage, as in serial presence detect.[5][6]

Flash memory packages can use die stacking with through-silicon vias and several dozen layers of 3D TLC NAND cells (per die) simultaneously to achieve capacities of up to 1 tebibyte per package using 16 stacked dies and an integrated flash controller as a separate die inside the package.[7][8][9][10]

History[edit]

Background[edit]

The origins of flash memory can be traced back to the development of the floating-gate MOSFET (FGMOS), also known as the floating-gate transistor.[11][12] The original MOSFET (metal–oxide–semiconductor field-effect transistor), also known as the MOS transistor, was invented by Egyptian engineer Mohamed M. Atalla and Korean engineer Dawon Kahng at Bell Labs in 1959.[13] Kahng went on to develop a variation, the floating-gate MOSFET, with Taiwanese-American engineer Simon Min Sze at Bell Labs in 1967.[14] They proposed that it could be used as floating-gate memory cells for storing a form of programmable read-only memory (PROM) that is both non-volatile and re-programmable.[14]

Early types of floating-gate memory included EPROM (erasable PROM) and EEPROM (electrically erasable PROM) in the 1970s.[14] However, early floating-gate memory required engineers to build a memory cell for each bit of data, which proved to be cumbersome,[15] slow,[16] and expensive, restricting floating-gate memory to niche applications in the 1970s, such as military equipment and the earliest experimental mobile phones.[11]

Invention and commercialization[edit]

Fujio Masuoka, while working for Toshiba, proposed a new type of floating-gate memory that allowed entire sections of memory to be erased quickly and easily, by applying a voltage to a single wire connected to a group of cells.[11] This led to Masuoka's invention of flash memory at Toshiba in 1980.[15][17][18] According to Toshiba, the name "flash" was suggested by Masuoka's colleague, Shōji Ariizumi, because the erasure process of the memory contents reminded him of the flash of a camera.[19] Masuoka and colleagues presented the invention of NOR flash in 1984,[20][21] and then NAND flash at the IEEE 1987 International Electron Devices Meeting (IEDM) held in San Francisco.[22]

Toshiba commercially launched NAND flash memory in 1987.[1][14] Intel Corporation introduced the first commercial NOR type flash chip in 1988.[23] NOR-based flash has long erase and write times, but provides full address and data buses, allowing random access to any memory location. This makes it a suitable replacement for older read-only memory (ROM) chips, which are used to store program code that rarely needs to be updated, such as a computer's BIOS or the firmware of set-top boxes. Its endurance may be from as little as 100 erase cycles for an on-chip flash memory,[24] to a more typical 10,000 or 100,000 erase cycles, up to 1,000,000 erase cycles.[25] NOR-based flash was the basis of early flash-based removable media; CompactFlash was originally based on it, though later cards moved to less expensive NAND flash.

NAND flash has reduced erase and write times, and requires less chip area per cell, thus allowing greater storage density and lower cost per bit than NOR flash. However, the I/O interface of NAND flash does not provide a random-access external address bus. Rather, data must be read on a block-wise basis, with typical block sizes of hundreds to thousands of bits. This makes NAND flash unsuitable as a drop-in replacement for program ROM, since most microprocessors and microcontrollers require byte-level random access. In this regard, NAND flash is similar to other secondary data storage devices, such as hard disks and optical media, and is thus highly suitable for use in mass-storage devices, such as memory cards and solid-state drives (SSD). For example, SSDs store data using multiple NAND flash memory chips.

The first NAND-based removable memory card format was SmartMedia, released in 1995. Many others followed, including MultiMediaCard, Secure Digital, Memory Stick, and xD-Picture Card.

Later developments[edit]

A new generation of memory card formats, including RS-MMC, miniSD and microSD, feature extremely small form factors. For example, the microSD card has an area of just over 1.5 cm2, with a thickness of less than 1 mm.

NAND flash has achieved significant levels of memory density as a result of several major technologies that were commercialized during the late 2000s to early 2010s.[26]

NOR flash was the most common type of Flash memory sold until 2005, when NAND flash overtook NOR flash in sales.[27]

Multi-level cell (MLC) technology stores more than one bit in each memory cell. NEC demonstrated multi-level cell (MLC) technology in 1998, with an 80 Mb flash memory chip storing 2 bits per cell.[28] STMicroelectronics also demonstrated MLC in 2000, with a 64 MB NOR flash memory chip.[29] In 2009, Toshiba and SanDisk introduced NAND flash chips with QLC technology storing 4 bits per cell and holding a capacity of 64 Gbit.[30][31] Samsung Electronics introduced triple-level cell (TLC) technology storing 3-bits per cell, and began mass-producing NAND chips with TLC technology in 2010.[32]

Charge trap flash[edit]

Charge trap flash (CTF) technology replaces the polysilicon floating gate, which is sandwiched between a blocking gate oxide above and a tunneling oxide below it, with an electrically insulating silicon nitride layer; the silicon nitride layer traps electrons. In theory, CTF is less prone to electron leakage, providing improved data retention.[33][34][35][36][37][38]

Because CTF replaces the polysilicon with an electrically insulating nitride, it allows for smaller cells and higher endurance (lower degradation or wear). However, electrons can become trapped and accumulate in the nitride, leading to degradation. Leakage is exacerbated at high temperatures since electrons become more excited with increasing temperatures. CTF technology however still uses a tunneling oxide and blocking layer which are the weak points of the technology, since they can still be damaged in the usual ways (the tunnel oxide can be degraded due to extremely high electric fields and the blocking layer due to Anode Hot Hole Injection (AHHI).[39][40]

Degradation or wear of the oxides is the reason why flash memory has limited endurance, and data retention goes down (the potential for data loss increases) with increasing degradation, since the oxides lose their electrically insulating characteristics as they degrade. The oxides must insulate against electrons to prevent them from leaking which would cause data loss.

In 1991, NEC researchers including N. Kodama, K. Oyama and Hiroki Shirai described a type of flash memory with a charge trap method.[41] In 1998, Boaz Eitan of Saifun Semiconductors (later acquired by Spansion) patented a flash memory technology named NROM that took advantage of a charge trapping layer to replace the conventional floating gate used in conventional flash memory designs.[42] In 2000, an Advanced Micro Devices (AMD) research team led by Richard M. Fastow, Egyptian engineer Khaled Z. Ahmed and Jordanian engineer Sameer Haddad (who later joined Spansion) demonstrated a charge-trapping mechanism for NOR flash memory cells.[43] CTF was later commercialized by AMD and Fujitsu in 2002.[44] 3D V-NAND (vertical NAND) technology stacks NAND flash memory cells vertically within a chip using 3D charge trap flash (CTP) technology. 3D V-NAND technology was first announced by Toshiba in 2007,[45] and the first device, with 24 layers, was first commercialized by Samsung Electronics in 2013.[46][47]

3D integrated circuit technology[edit]

3D integrated circuit (3D IC) technology stacks integrated circuit (IC) chips vertically into a single 3D IC chip package.[26] Toshiba introduced 3D IC technology to NAND flash memory in April 2007, when they debuted a 16 GB eMMC compliant (product number THGAM0G7D8DBAI6, often abbreviated THGAM on consumer websites) embedded NAND flash memory chip, which was manufactured with eight stacked 2 GB NAND flash chips.[48] In September 2007, Hynix Semiconductor (now SK Hynix) introduced 24-layer 3D IC technology, with a 16 GB flash memory chip that was manufactured with 24 stacked NAND flash chips using a wafer bonding process.[49] Toshiba also used an eight-layer 3D IC for their 32 GB THGBM flash chip in 2008.[50] In 2010, Toshiba used a 16-layer 3D IC for their 128 GB THGBM2 flash chip, which was manufactured with 16 stacked 8 GB chips.[51] In the 2010s, 3D ICs came into widespread commercial use for NAND flash memory in mobile devices.[26]

In 2016, Micron and Intel introduced a technology known as CMOS Under the Array/CMOS Under Array (CUA), Core over Periphery (COP), Periphery Under Cell (PUA), or Xtacking,[52] in which the control circuitry for the flash memory is placed under or above the flash memory cell array. This has allowed for an increase in the number of planes or sections a flash memory chip has, increasing from 2 planes to 4, without increasing the area dedicated to the control or periphery circuitry. This increases the number of IO operations per flash chip or die, but it also introduces challenges when building capacitors for charge pumps used to write to the flash memory.[53][54][55] Some flash dies have as many as 6 planes.[56]

As of August 2017, microSD cards with a capacity up to 400 GB (400 billion bytes) are available.[57][58] The same year, Samsung combined 3D IC chip stacking with its 3D V-NAND and TLC technologies to manufacture its 512 GB KLUFG8R1EM flash memory chip with eight stacked 64-layer V-NAND chips.[8] In 2019, Samsung produced a 1024 GB flash chip, with eight stacked 96-layer V-NAND chips and with QLC technology.[59][60]

Principles of operation[edit]

Flash memory stores information in an array of memory cells made from floating-gate transistors. In single-level cell (SLC) devices, each cell stores only one bit of information. Multi-level cell (MLC) devices, including triple-level cell (TLC) devices, can store more than one bit per cell.

The floating gate may be conductive (typically polysilicon in most kinds of flash memory) or non-conductive (as in SONOS flash memory).[61]

Floating-gate MOSFET[edit]

In flash memory, each memory cell resembles a standard metal–oxide–semiconductor field-effect transistor (MOSFET) except that the transistor has two gates instead of one. The cells can be seen as an electrical switch in which current flows between two terminals (source and drain) and is controlled by a floating gate (FG) and a control gate (CG). The CG is similar to the gate in other MOS transistors, but below this, there is the FG insulated all around by an oxide layer. The FG is interposed between the CG and the MOSFET channel. Because the FG is electrically isolated by its insulating layer, electrons placed on it are trapped. When the FG is charged with electrons, this charge screens the electric field from the CG, thus, increasing the threshold voltage (VT) of the cell. This means that the VT of the cell can be changed between the uncharged FG threshold voltage (VT1) and the higher charged FG threshold voltage (VT2) by changing the FG charge. In order to read a value from the cell, an intermediate voltage (VI) between VT1 and VT2 is applied to the CG. If the channel conducts at VI, the FG must be uncharged (if it were charged, there would not be conduction because VI is less than VT2). If the channel does not conduct at the VI, it indicates that the FG is charged. The binary value of the cell is sensed by determining whether there is current flowing through the transistor when VI is asserted on the CG. In a multi-level cell device, which stores more than one bit per cell, the amount of current flow is sensed (rather than simply its presence or absence), in order to determine more precisely the level of charge on the FG.

Floating gate MOSFETs are so named because there is an electrically insulating tunnel oxide layer between the floating gate and the silicon, so the gate "floats" above the silicon. The oxide keeps the electrons confined to the floating gate. Degradation or wear (and the limited endurance of floating gate Flash memory) occurs due to the extremely high electric field (10 million volts per centimeter) experienced by the oxide. Such high voltage densities can break atomic bonds over time in the relatively thin oxide, gradually degrading its electrically insulating properties and allowing electrons to be trapped in and pass through freely (leak) from the floating gate into the oxide, increasing the likelihood of data loss since the electrons (the quantity of which is used to represent different charge levels, each assigned to a different combination of bits in MLC Flash) are normally in the floating gate. This is why data retention goes down and the risk of data loss increases with increasing degradation.[62][63][37][64][65] The silicon oxide in a cell degrades with every erase operation. The degradation increases the amount of negative charge in the cell over time due to trapped electrons in the oxide and negates some of the control gate voltage, this over time also makes erasing the cell slower, so to maintain the performance and reliability of the NAND chip, the cell must be retired from use. Endurance also decreases with the number of bits in a cell. With more bits in a cell, the number of possible states (each represented by a different voltage level) in a cell increases and is more sensitive to the voltages used for programming. Voltages may be adjusted to compensate for degradation of the silicon oxide, and as the number of bits increases, the number of possible states also increases and thus the cell is less tolerant of adjustments to programming voltages, because there is less space between the voltage levels that define each state in a cell.[66]

Fowler–Nordheim tunneling[edit]

The process of moving electrons from the control gate and into the floating gate is called Fowler–Nordheim tunneling, and it fundamentally changes the characteristics of the cell by increasing the MOSFET's threshold voltage. This, in turn, changes the drain-source current that flows through the transistor for a given gate voltage, which is ultimately used to encode a binary value. The Fowler-Nordheim tunneling effect is reversible, so electrons can be added to or removed from the floating gate, processes traditionally known as writing and erasing.[67]

Internal charge pumps[edit]

Despite the need for relatively high programming and erasing voltages, virtually all flash chips today require only a single supply voltage and produce the high voltages that are required using on-chip charge pumps.

Over half the energy used by a 1.8 V-NAND flash chip is lost in the charge pump itself. Since boost converters are inherently more efficient than charge pumps, researchers developing low-power SSDs have proposed returning to the dual Vcc/Vpp supply voltages used on all early flash chips, driving the high Vpp voltage for all flash chips in an SSD with a single shared external boost converter.[68][69][70][71][72][73][74][75]

In spacecraft and other high-radiation environments, the on-chip charge pump is the first part of the flash chip to fail, although flash memories will continue to work – in read-only mode – at much higher radiation levels.[76]

NOR flash[edit]

In NOR flash, each cell has one end connected directly to ground, and the other end connected directly to a bit line. This arrangement is called "NOR flash" because it acts like a NOR gate: when one of the word lines (connected to the cell's CG) is brought high, the corresponding storage transistor acts to pull the output bit line low. NOR flash continues to be the technology of choice for embedded applications requiring a discrete non-volatile memory device.[citation needed] The low read latencies characteristic of NOR devices allow for both direct code execution and data storage in a single memory product.[77]

Programming[edit]

A single-level NOR flash cell in its default state is logically equivalent to a binary "1" value, because current will flow through the channel under application of an appropriate voltage to the control gate, so that the bitline voltage is pulled down. A NOR flash cell can be programmed, or set to a binary "0" value, by the following procedure:

- an elevated on-voltage (typically >5 V) is applied to the CG

- the channel is now turned on, so electrons can flow from the source to the drain (assuming an NMOS transistor)

- the source-drain current is sufficiently high to cause some high energy electrons to jump through the insulating layer onto the FG, via a process called hot-electron injection.

Erasing[edit]

To erase a NOR flash cell (resetting it to the "1" state), a large voltage of the opposite polarity is applied between the CG and source terminal, pulling the electrons off the FG through Fowler–Nordheim tunneling (FN tunneling).[78] This is known as Negative gate source source erase. Newer NOR memories can erase using negative gate channel erase, which biases the wordline on a NOR memory cell block and the P-well of the memory cell block to allow FN tunneling to be carried out, erasing the cell block. Older memories used source erase, in which a high voltage was applied to the source and then electrons from the FG were moved to the source.[79][80] Modern NOR flash memory chips are divided into erase segments (often called blocks or sectors). The erase operation can be performed only on a block-wise basis; all the cells in an erase segment must be erased together.[81] Programming of NOR cells, however, generally can be performed one byte or word at a time.

NAND flash[edit]

NAND flash also uses floating-gate transistors, but they are connected in a way that resembles a NAND gate: several transistors are connected in series, and the bit line is pulled low only if all the word lines are pulled high (above the transistors' VT). These groups are then connected via some additional transistors to a NOR-style bit line array in the same way that single transistors are linked in NOR flash.

Compared to NOR flash, replacing single transistors with serial-linked groups adds an extra level of addressing. Whereas NOR flash might address memory by page then word, NAND flash might address it by page, word and bit. Bit-level addressing suits bit-serial applications (such as hard disk emulation), which access only one bit at a time. Execute-in-place applications, on the other hand, require every bit in a word to be accessed simultaneously. This requires word-level addressing. In any case, both bit and word addressing modes are possible with either NOR or NAND flash.

To read data, first the desired group is selected (in the same way that a single transistor is selected from a NOR array). Next, most of the word lines are pulled up above VT2, while one of them is pulled up to VI. The series group will conduct (and pull the bit line low) if the selected bit has not been programmed.

Despite the additional transistors, the reduction in ground wires and bit lines allows a denser layout and greater storage capacity per chip. (The ground wires and bit lines are actually much wider than the lines in the diagrams.) In addition, NAND flash is typically permitted to contain a certain number of faults (NOR flash, as is used for a BIOS ROM, is expected to be fault-free). Manufacturers try to maximize the amount of usable storage by shrinking the size of the transistors or cells, however the industry can avoid this and achieve higher storage densities per die by using 3D NAND, which stacks cells on top of each other.

NAND flash cells are read by analysing their response to various voltages.[64]

Writing and erasing[edit]

NAND flash uses tunnel injection for writing and tunnel release for erasing. NAND flash memory forms the core of the removable USB storage devices known as USB flash drives, as well as most memory card formats and solid-state drives available today.

The hierarchical structure of NAND flash starts at a cell level which establishes strings, then pages, blocks, planes and ultimately a die. A string is a series of connected NAND cells in which the source of one cell is connected to the drain of the next one. Depending on the NAND technology, a string typically consists of 32 to 128 NAND cells. Strings are organised into pages which are then organised into blocks in which each string is connected to a separate line called a bitline. All cells with the same position in the string are connected through the control gates by a wordline. A plane contains a certain number of blocks that are connected through the same bitline. A flash die consists of one or more planes, and the peripheral circuitry that is needed to perform all the read, write, and erase operations.

The architecture of NAND flash means that data can be read and programmed (written) in pages, typically between 4 KiB and 16 KiB in size, but can only be erased at the level of entire blocks consisting of multiple pages. When a block is erased, all the cells are logically set to 1. Data can only be programmed in one pass to a page in a block that was erased. Any cells that have been set to 0 by programming can only be reset to 1 by erasing the entire block. This means that before new data can be programmed into a page that already contains data, the current contents of the page plus the new data must be copied to a new, erased page. If a suitable erased page is available, the data can be written to it immediately. If no erased page is available, a block must be erased before copying the data to a page in that block. The old page is then marked as invalid and is available for erasing and reuse.[82]

Vertical NAND[edit]

Vertical NAND (V-NAND) or 3D NAND memory stacks memory cells vertically and uses a charge trap flash architecture. The vertical layers allow larger areal bit densities without requiring smaller individual cells.[83] It is also sold under the trademark BiCS Flash, which is a trademark of Kioxia Corporation (formerly Toshiba Memory Corporation). 3D NAND was first announced by Toshiba in 2007.[45] V-NAND was first commercially manufactured by Samsung Electronics in 2013.[46][47][84][85]

Structure[edit]

V-NAND uses a charge trap flash geometry (which was commercially introduced in 2002 by AMD and Fujitsu)[44] that stores charge on an embedded silicon nitride film. Such a film is more robust against point defects and can be made thicker to hold larger numbers of electrons. V-NAND wraps a planar charge trap cell into a cylindrical form.[83] As of 2020, 3D NAND flash memories by Micron and Intel instead use floating gates, however, Micron 128 layer and above 3D NAND memories use a conventional charge trap structure, due to the dissolution of the partnership between Micron and Intel. Charge trap 3D NAND flash is thinner than floating gate 3D NAND. In floating gate 3D NAND, the memory cells are completely separated from one another, whereas in charge trap 3D NAND, vertical groups of memory cells share the same silicon nitride material.[86]

An individual memory cell is made up of one planar polysilicon layer containing a hole filled by multiple concentric vertical cylinders. The hole's polysilicon surface acts as the gate electrode. The outermost silicon dioxide cylinder acts as the gate dielectric, enclosing a silicon nitride cylinder that stores charge, in turn enclosing a silicon dioxide cylinder as the tunnel dielectric that surrounds a central rod of conducting polysilicon which acts as the conducting channel.[83]

Memory cells in different vertical layers do not interfere with each other, as the charges cannot move vertically through the silicon nitride storage medium, and the electric fields associated with the gates are closely confined within each layer. The vertical collection is electrically identical to the serial-linked groups in which conventional NAND flash memory is configured.[83] There is also string stacking, which builds several 3D NAND memory arrays or "plugs"[87] separately, but stacked together to create a product with a higher number of 3D NAND layers on a single die. Often, two or 3 arrays are stacked. The misalignment between plugs is in the order of 30 to 10nm.[53][88][89]

Construction[edit]

Growth of a group of V-NAND cells begins with an alternating stack of conducting (doped) polysilicon layers and insulating silicon dioxide layers.[83]

The next step is to form a cylindrical hole through these layers. In practice, a 128 Gbit V-NAND chip with 24 layers of memory cells requires about 2.9 billion such holes. Next, the hole's inner surface receives multiple coatings, first silicon dioxide, then silicon nitride, then a second layer of silicon dioxide. Finally, the hole is filled with conducting (doped) polysilicon.[83]

Performance[edit]

As of 2013,[update] V-NAND flash architecture allows read and write operations twice as fast as conventional NAND and can last up to 10 times as long, while consuming 50 percent less power. They offer comparable physical bit density using 10-nm lithography but may be able to increase bit density by up to two orders of magnitude, given V-NAND's use of up to several hundred layers.[83] As of 2020, V-NAND chips with 160 layers are under development by Samsung.[90]

Cost[edit]

The wafer cost of a 3D NAND is comparable with scaled down (32 nm or less) planar NAND flash.[91] However, with planar NAND scaling stopping at 16 nm, the cost per bit reduction can continue by 3D NAND starting with 16 layers. However, due to the non-vertical sidewall of the hole etched through the layers; even a slight deviation leads to a minimum bit cost, i.e., minimum equivalent design rule (or maximum density), for a given number of layers; this minimum bit cost layer number decreases for smaller hole diameter.[92]

Limitations[edit]

Block erasure[edit]

One limitation of flash memory is that it can be erased only a block at a time. This generally sets all bits in the block to 1. Starting with a freshly erased block, any location within that block can be programmed. However, once a bit has been set to 0, only by erasing the entire block can it be changed back to 1. In other words, flash memory (specifically NOR flash) offers random-access read and programming operations but does not offer arbitrary random-access rewrite or erase operations. A location can, however, be rewritten as long as the new value's 0 bits are a superset of the over-written values. For example, a nibble value may be erased to 1111, then written as 1110. Successive writes to that nibble can change it to 1010, then 0010, and finally 0000. Essentially, erasure sets all bits to 1, and programming can only clear bits to 0.[93]Some file systems designed for flash devices make use of this rewrite capability, for example Yaffs1, to represent sector metadata.Other flash file systems, such as YAFFS2, never make use of this "rewrite" capability—they do a lot of extra work to meet a "write once rule".

Although data structures in flash memory cannot be updated in completely general ways, this allows members to be "removed" by marking them as invalid. This technique may need to be modified for multi-level cell devices, where one memory cell holds more than one bit.

Common flash devices such as USB flash drives and memory cards provide only a block-level interface, or flash translation layer (FTL), which writes to a different cell each time to wear-level the device. This prevents incremental writing within a block; however, it does help the device from being prematurely worn out by intensive write patterns.

Data retention[edit]

Data stored on flash cells is steadily lost due to electron detrapping[definition needed]. The rate of loss increases exponentially as the absolute temperature increases. For example: For a 45 nm NOR flash, at 1000 hours, the threshold voltage (Vt) loss at 25 deg Celsius is about half that at 90 deg Celsius.[94]

Memory wear[edit]

Another limitation is that flash memory has a finite number of program – erase cycles (typically written as P/E cycles).[95][96] Micron Technology and Sun Microsystems announced an SLC NAND flash memory chip rated for 1,000,000 P/E cycles on 17 December 2008.[97]

The guaranteed cycle count may apply only to block zero (as is the case with TSOP NAND devices), or to all blocks (as in NOR). This effect is mitigated in some chip firmware or file system drivers by counting the writes and dynamically remapping blocks in order to spread write operations between sectors; this technique is called wear leveling. Another approach is to perform write verification and remapping to spare sectors in case of write failure, a technique called bad block management (BBM). For portable consumer devices, these wear out management techniques typically extend the life of the flash memory beyond the life of the device itself, and some data loss may be acceptable in these applications. For high-reliability data storage, however, it is not advisable to use flash memory that would have to go through a large number of programming cycles. This limitation also exists for 'read-only' applications such as thin clients and routers, which are programmed only once or at most a few times during their lifetimes, due to read disturb (see below).

In December 2012, Taiwanese engineers from Macronix revealed their intention to announce at the 2012 IEEE International Electron Devices Meeting that they had figured out how to improve NAND flash storage read/write cycles from 10,000 to 100 million cycles using a "self-healing" process that used a flash chip with "onboard heaters that could anneal small groups of memory cells."[98] The built-in thermal annealing was to replace the usual erase cycle with a local high temperature process that not only erased the stored charge, but also repaired the electron-induced stress in the chip, giving write cycles of at least 100 million.[99] The result was to be a chip that could be erased and rewritten over and over, even when it should theoretically break down. As promising as Macronix's breakthrough might have been for the mobile industry, however, there were no plans for a commercial product featuring this capability to be released any time in the near future.[100]

Read disturb[edit]

The method used to read NAND flash memory can cause nearby cells in the same memory block to change over time (become programmed). This is known as read disturb. The threshold number of reads is generally in the hundreds of thousands of reads between intervening erase operations. If reading continually from one cell, that cell will not fail but rather one of the surrounding cells will on a subsequent read. To avoid the read disturb problem the flash controller will typically count the total number of reads to a block since the last erase. When the count exceeds a target limit, the affected block is copied over to a new block, erased, then released to the block pool. The original block is as good as new after the erase. If the flash controller does not intervene in time, however, a read disturb error will occur with possible data loss if the errors are too numerous to correct with an error-correcting code.[101][102][103]

X-ray effects[edit]

Most flash ICs come in ball grid array (BGA) packages, and even the ones that do not are often mounted on a PCB next to other BGA packages. After PCB Assembly, boards with BGA packages are often X-rayed to see if the balls are making proper connections to the proper pad, or if the BGA needs rework. These X-rays can erase programmed bits in a flash chip (convert programmed "0" bits into erased "1" bits). Erased bits ("1" bits) are not affected by X-rays.[104][105]

Some manufacturers are now making X-ray proof SD[106] and USB[107] memory devices.

Low-level access[edit]

The low-level interface to flash memory chips differs from those of other memory types such as DRAM, ROM, and EEPROM, which support bit-alterability (both zero to one and one to zero) and random access via externally accessible address buses.

NOR memory has an external address bus for reading and programming. For NOR memory, reading and programming are random-access, and unlocking and erasing are block-wise. For NAND memory, reading and programming are page-wise, and unlocking and erasing are block-wise.

NOR memories[edit]

Reading from NOR flash is similar to reading from random-access memory, provided the address and data bus are mapped correctly. Because of this, most microprocessors can use NOR flash memory as execute in place (XIP) memory,[108] meaning that programs stored in NOR flash can be executed directly from the NOR flash without needing to be copied into RAM first. NOR flash may be programmed in a random-access manner similar to reading. Programming changes bits from a logical one to a zero. Bits that are already zero are left unchanged. Erasure must happen a block at a time, and resets all the bits in the erased block back to one. Typical block sizes are 64, 128, or 256 KiB.

Bad block management is a relatively new feature in NOR chips. In older NOR devices not supporting bad block management, the software or device driver controlling the memory chip must correct for blocks that wear out, or the device will cease to work reliably.

The specific commands used to lock, unlock, program, or erase NOR memories differ for each manufacturer. To avoid needing unique driver software for every device made, special Common Flash Memory Interface (CFI) commands allow the device to identify itself and its critical operating parameters.

Besides its use as random-access ROM, NOR flash can also be used as a storage device, by taking advantage of random-access programming. Some devices offer read-while-write functionality so that code continues to execute even while a program or erase operation is occurring in the background. For sequential data writes, NOR flash chips typically have slow write speeds, compared with NAND flash.

Typical NOR flash does not need an error correcting code.[109]

NAND memories[edit]

NAND flash architecture was introduced by Toshiba in 1989.[110] These memories are accessed much like block devices, such as hard disks. Each block consists of a number of pages. The pages are typically 512,[111] 2,048 or 4,096 bytes in size. Associated with each page are a few bytes (typically 1/32 of the data size) that can be used for storage of an error correcting code (ECC) checksum.

Typical block sizes include:

- 32 pages of 512+16 bytes each for a block size (effective) of 16 KiB

- 64 pages of 2,048+64 bytes each for a block size of 128 KiB[112]

- 64 pages of 4,096+128 bytes each for a block size of 256 KiB[113]

- 128 pages of 4,096+128 bytes each for a block size of 512 KiB.

Modern NAND flash may have erase block size between 1 MiB to 128 MiB. While reading and programming is performed on a page basis, erasure can only be performed on a block basis.[114]

NAND devices also require bad block management by the device driver software or by a separate controller chip. Some SD cards, for example, include controller circuitry to perform bad block management and wear leveling. When a logical block is accessed by high-level software, it is mapped to a physical block by the device driver or controller. A number of blocks on the flash chip may be set aside for storing mapping tables to deal with bad blocks, or the system may simply check each block at power-up to create a bad block map in RAM. The overall memory capacity gradually shrinks as more blocks are marked as bad.

NAND relies on ECC to compensate for bits that may spontaneously fail during normal device operation. A typical ECC will correct a one-bit error in each 2048 bits (256 bytes) using 22 bits of ECC, or a one-bit error in each 4096 bits (512 bytes) using 24 bits of ECC.[115] If the ECC cannot correct the error during read, it may still detect the error. When doing erase or program operations, the device can detect blocks that fail to program or erase and mark them bad. The data is then written to a different, good block, and the bad block map is updated.

Hamming codes are the most commonly used ECC for SLC NAND flash. Reed-Solomon codes and BCH codes (Bose-Chaudhuri-Hocquenghem codes) are commonly used ECC for MLC NAND flash. Some MLC NAND flash chips internally generate the appropriate BCH error correction codes.[109]

Most NAND devices are shipped from the factory with some bad blocks. These are typically marked according to a specified bad block marking strategy. By allowing some bad blocks, manufacturers achieve far higher yields than would be possible if all blocks had to be verified to be good. This significantly reduces NAND flash costs and only slightly decreases the storage capacity of the parts.

When executing software from NAND memories, virtual memory strategies are often used: memory contents must first be paged or copied into memory-mapped RAM and executed there (leading to the common combination of NAND + RAM). A memory management unit (MMU) in the system is helpful, but this can also be accomplished with overlays. For this reason, some systems will use a combination of NOR and NAND memories, where a smaller NOR memory is used as software ROM and a larger NAND memory is partitioned with a file system for use as a non-volatile data storage area.

NAND sacrifices the random-access and execute-in-place advantages of NOR. NAND is best suited to systems requiring high capacity data storage. It offers higher densities, larger capacities, and lower cost. It has faster erases, sequential writes, and sequential reads.

Standardization[edit]

A group called the Open NAND Flash Interface Working Group (ONFI) has developed a standardized low-level interface for NAND flash chips. This allows interoperability between conforming NAND devices from different vendors. The ONFI specification version 1.0[116] was released on 28 December 2006. It specifies:

- A standard physical interface (pinout) for NAND flash in TSOP-48, WSOP-48, LGA-52, and BGA-63 packages

- A standard command set for reading, writing, and erasing NAND flash chips

- A mechanism for self-identification (comparable to the serial presence detection feature of SDRAM memory modules)

The ONFI group is supported by major NAND flash manufacturers, including Hynix, Intel, Micron Technology, and Numonyx, as well as by major manufacturers of devices incorporating NAND flash chips.[117]

Two major flash device manufacturers, Toshiba and Samsung, have chosen to use an interface of their own design known as Toggle Mode (and now Toggle). This interface isn't pin-to-pin compatible with the ONFI specification. The result is that a product designed for one vendor's devices may not be able to use another vendor's devices.[118]

A group of vendors, including Intel, Dell, and Microsoft, formed a Non-Volatile Memory Host Controller Interface (NVMHCI) Working Group.[119] The goal of the group is to provide standard software and hardware programming interfaces for nonvolatile memory subsystems, including the "flash cache" device connected to the PCI Express bus.

Distinction between NOR and NAND flash[edit]

NOR and NAND flash differ in two important ways:

- The connections of the individual memory cells are different.[120]

- The interface provided for reading and writing the memory is different; NOR allows random access[121] as it can be either byte-addressable or word-addressable, with words being for example 32 bits long,[122][123][124] while NAND allows only page access.[125]

NOR[126] and NAND flash get their names from the structure of the interconnections between memory cells.[citation needed] In NOR flash, cells are connected in parallel to the bit lines, allowing cells to be read and programmed individually.[127] The parallel connection of cells resembles the parallel connection of transistors in a CMOS NOR gate.[128] In NAND flash, cells are connected in series,[127] resembling a CMOS NAND gate. The series connections consume less space than parallel ones, reducing the cost of NAND flash.[127] It does not, by itself, prevent NAND cells from being read and programmed individually.[citation needed]

Each NOR flash cell is larger than a NAND flash cell – 10 F2 vs 4 F2 – even when using exactly the same semiconductor device fabrication and so each transistor, contact, etc. is exactly the same size – because NOR flash cells require a separate metal contact for each cell.[129][130]

Because of the series connection and removal of wordline contacts, a large grid of NAND flash memory cells will occupy perhaps only 60% of the area of equivalent NOR cells[131] (assuming the same CMOS process resolution, for example, 130 nm, 90 nm, or 65 nm). NAND flash's designers realized that the area of a NAND chip, and thus the cost, could be further reduced by removing the external address and data bus circuitry. Instead, external devices could communicate with NAND flash via sequential-accessed command and data registers, which would internally retrieve and output the necessary data. This design choice made random-access of NAND flash memory impossible, but the goal of NAND flash was to replace mechanical hard disks, not to replace ROMs.

The first GSM phones and many feature phones had NOR flash memory, from which processor instructions could be executed directly in an execute in place architecture and allowed for short boot times. With smartphones, NAND flash memory was adopted as it has larger storage capacities and lower costs, but causes longer boot times because instructions cannot be executed from it directly, and must be copied to RAM memory first before execution.[132]

| Attribute | NAND | NOR |

|---|---|---|

| Main application | File storage | Code execution |

| Storage capacity | High | Low |

| Cost per bit | Low | |

| Active power | Low | |

| Standby power | Low | |

| Write speed | Fast | |

| Read speed | Fast | |

| Execute in place[133] (XIP) | No | Yes |

| Reliability | High |

Write endurance[edit]

The write endurance of SLC floating-gate NOR flash is typically equal to or greater than that of NAND flash, while MLC NOR and NAND flash have similar endurance capabilities. Examples of endurance cycle ratings listed in datasheets for NAND and NOR flash, as well as in storage devices using flash memory, are provided.[134]

| Type of flash memory | Endurance rating (erases per block) | Example(s) of flash memory or storage device |

|---|---|---|

| SLC NAND | 50,000–100,000 | Samsung OneNAND KFW4G16Q2M, Toshiba SLC NAND flash chips,[135][136][137][138][139] Transcend SD500, Fujitsu S26361-F3298 |

| MLC NAND | 5,000–10,000 for medium-capacity; 1,000 to 3,000 for high-capacity[140] | Samsung K9G8G08U0M (Example for medium-capacity applications), Memblaze PBlaze4,[141] ADATA SU900, Mushkin Reactor |

| TLC NAND | 1,000 | Samsung SSD 840 |

| QLC NAND | Unknown | SanDisk X4 NAND flash SD cards[142][143][144][145] |

| 3D SLC NAND | >100,000 | Samsung Z-NAND[146] |

| 3D MLC NAND | 6,000–40,000 | Samsung SSD 850 PRO, Samsung SSD 845DC PRO,[147][148] Samsung 860 PRO |

| 3D TLC NAND | 1,500–5,000 | Samsung SSD 850 EVO, Samsung SSD 845DC EVO, Crucial MX300[149][150][151],Memblaze PBlaze5 900, Memblaze PBlaze5 700, Memblaze PBlaze5 910/916, Memblaze PBlaze5 510/516,[152] [153] [154] [155] ADATA SX 8200 PRO (also being sold under "XPG Gammix" branding, model S11 PRO) |

| 3D QLC NAND | 100–1,500 | Твердотельный накопитель Samsung 860 QVO SATA, твердотельный накопитель Intel 660p, Micron 5210 ION, Crucial P1, твердотельный накопитель Samsung BM991 NVMe [156] [157] [158] [159] [160] [161] [162] [163] |

| 3D ПЛК NAND | Unknown | В разработке SK Hynix (ранее Intel) [164] и Kioxia (ранее Toshiba Memory). [140] |

| SLC (плавающий- ворота) НО | 100,000–1,000,000 | Numonyx M58BW (рейтинг выносливости 100 000 стираний на блок); Spansion S29CD016J (долговечность: 1 000 000 стираний на блок) |

| MLC (плавающий- ворота) НО | 100,000 | Вспышка Numonyx J3 |

Однако, применяя определенные алгоритмы и парадигмы проектирования, такие как выравнивание износа и избыточное выделение памяти , можно настроить надежность системы хранения в соответствии с конкретными требованиями. [165]

Чтобы рассчитать срок службы флэш-памяти NAND, необходимо учитывать размер микросхемы памяти, тип памяти (например, SLC/MLC/TLC) и шаблон использования. Промышленная NAND и серверная NAND пользуются спросом благодаря своей емкости, большей выносливости и надежности в чувствительных средах.

По мере увеличения количества битов на ячейку производительность и срок службы флэш-памяти NAND могут ухудшаться, что приводит к увеличению времени случайного чтения до 100 мкс для TLC NAND, что в 4 раза больше времени, необходимого для SLC NAND, и в два раза больше времени, необходимого для MLC NAND для случайного чтения. . [66]

Файловые системы Flash [ править ]

Из-за особых характеристик флэш-памяти ее лучше всего использовать либо с контроллером для выравнивания износа и исправления ошибок, либо со специально разработанными флэш-файловыми системами, которые распределяют записи по носителю и справляются с длительным временем стирания флэш-блоков NOR. Основная концепция файловых систем флэш-памяти заключается в следующем: когда флэш-память должна быть обновлена, файловая система записывает новую копию измененных данных в новый блок, переназначает указатели файлов, а затем стирает старый блок позже, когда он есть время.

На практике флэш-файловые системы используются только для устройств памяти (MTD), которые представляют собой встроенную флэш-память, не имеющую контроллера. Съемные карты флэш-памяти , твердотельные накопители, чипы eMMC / eUFS и флэш-накопители USB имеют встроенные контроллеры для выравнивания износа и исправления ошибок, поэтому использование конкретной файловой системы флэш-памяти может не принести пользы.

Вместимость [ править ]

Несколько чипов часто располагаются в массиве или на кристалле для достижения более высокой производительности. [166] для использования в бытовых электронных устройствах, таких как мультимедийные проигрыватели или GPS . Масштабирование (увеличение) емкости флэш-чипов обычно соответствует закону Мура , поскольку они производятся с использованием многих одних и тех же технологий и оборудования для интегральных схем . С момента появления 3D NAND масштабирование больше не обязательно связано с законом Мура, поскольку транзисторы (ячейки) меньшего размера больше не используются.

Потребительские флэш-накопители обычно рекламируются с указанием полезных размеров, выраженных небольшим целым числом, степенью двойки (2, 4, 8 и т. д.), и традиционным обозначением мегабайтов (МБ) или гигабайтов (ГБ); например, 512 МБ, 8 ГБ. Сюда входят твердотельные накопители , продаваемые в качестве замены жестких дисков, в соответствии с традиционными жесткими дисками , в которых используются десятичные префиксы . [167] Таким образом, SSD с маркировкой «64 ГБ » имеет размер не менее 64×1000. 3 байт (64 ГБ). У большинства пользователей для файлов будет немного меньшая емкость, чем эта, из-за места, занимаемого метаданными файловой системы, а также из-за того, что некоторые операционные системы сообщают о емкости SSD, используя двоичные префиксы , которые несколько больше, чем обычные префиксы.

Чипы флэш-памяти внутри них имеют строго двоичные кратные размеры, но фактическая общая емкость чипов не может быть использована в интерфейсе накопителя.Она значительно превышает заявленную емкость, чтобы обеспечить распределение операций записи ( выравнивание износа ), резервирование, коды исправления ошибок и другие метаданные, необходимые внутренней прошивке устройства.

В 2005 году Toshiba и SanDisk разработали флэш-чип NAND, способный хранить 1 ГБ данных с использованием технологии многоуровневых ячеек (MLC), способной хранить два бита данных на ячейку. В сентябре 2005 года компания Samsung Electronics объявила о разработке первого в мире чипа емкостью 2 ГБ. [168]

В марте 2006 года Samsung анонсировала флэш-жесткие диски емкостью 4 ГБ, что по сути того же порядка, что и жесткие диски для ноутбуков меньшего размера, а в сентябре 2006 года Samsung анонсировала чип емкостью 8 ГБ, произведенный с использованием 40-нм производственного процесса. [169] В январе 2008 года SanDisk объявила о выпуске карт MicroSDHC емкостью 16 ГБ и SDHC Plus емкостью 32 ГБ. [170] [171]

Более поздние флэш-накопители (по состоянию на 2012 год) имеют гораздо большую емкость: 64, 128 и 256 ГБ. [172]

Совместная разработка Intel и Micron позволит производить 32-слойные накопители емкостью 3,5 терабайта (ТБ). [ нужны разъяснения ] ) Флеш-накопители NAND и твердотельные накопители стандартного размера емкостью 10 ТБ. Устройство включает в себя 5 пакетов кристаллов TLC по 16 × 48 ГБ с использованием конструкции ячейки с плавающим затвором. [173]

Флэш-чипы продолжают производиться с емкостью менее или около 1 МБ (например, для BIOS-ROM и встроенных приложений).

В июле 2016 года Samsung анонсировала модель емкостью 4 ТБ. [ нужны разъяснения ] Samsung 850 EVO, в котором используется 48-слойная TLC 3D V-NAND емкостью 256 Гбит. [174] В августе 2016 года Samsung анонсировала 2,5-дюймовый твердотельный накопитель SAS емкостью 32 ТБ на базе 64-слойной TLC 3D V-NAND емкостью 512 Гбит. Кроме того, к 2020 году Samsung планирует представить твердотельные накопители емкостью до 100 ТБ. [175]

Стоимость трансфера [ править ]

Устройства флэш-памяти обычно гораздо быстрее читают, чем записывают. [176] Производительность также зависит от качества контроллеров хранилища, которое становится более критичным, когда устройства частично заполнены. [ нечеткий ] [176] Даже если единственным изменением в производстве является усадка штампа, отсутствие соответствующего контроллера может привести к снижению скорости. [177]

Приложения [ править ]

Серийная вспышка [ править ]

Последовательная флэш-память — это небольшая флэш-память с низким энергопотреблением, которая обеспечивает только последовательный доступ к данным — вместо обращения к отдельным байтам пользователь последовательно читает или записывает большие смежные группы байтов в адресном пространстве. Шина последовательного периферийного интерфейса (SPI) — это типичный протокол доступа к устройству. При включении во встраиваемую систему последовательная флэш-память требует меньше проводов на печатной плате , чем параллельная флэш-память, поскольку она передает и принимает данные побитно. Это может позволить сократить пространство на плате, энергопотребление и общую стоимость системы.

Существует несколько причин, по которым последовательное устройство с меньшим количеством внешних контактов, чем параллельное устройство, может значительно снизить общую стоимость:

- Многие ASIC имеют ограничение по количеству контактных площадок, что означает, что размер кристалла ограничен количеством контактных площадок, а не сложностью и количеством вентилей, используемых для логики устройства. Таким образом, устранение контактных площадок позволяет создать более компактную интегральную схему на кристалле меньшего размера; это увеличивает количество штампов, которые можно изготовить на пластине , и, таким образом, снижает стоимость одного кристалла.

- Уменьшение количества внешних контактов также снижает затраты на сборку и упаковку . Последовательное устройство может быть упаковано в меньший и более простой корпус, чем параллельное устройство.

- Корпуса меньшего размера и с меньшим количеством контактов занимают меньшую площадь печатной платы.

- Устройства с меньшим количеством контактов упрощают разводку печатных плат .

Существует два основных типа флэш-памяти SPI. Первый тип характеризуется небольшими страницами и одним или несколькими внутренними страничными буферами SRAM, позволяющими считывать всю страницу в буфер, частично изменять ее и затем записывать обратно (например, Atmel AT45 DataFlash или Micron Technology Page Erase NOR Flash). ). Второй тип имеет секторы большего размера, при этом наименьшие сектора, обычно встречающиеся во флэш-памяти SPI этого типа, имеют размер 4 КБ, но они могут достигать 64 КБ. Поскольку у этого типа флэш-памяти SPI отсутствует внутренний буфер SRAM, вся страница должна быть считана и изменена перед обратной записью, что замедляет управление. Однако второй тип дешевле первого и поэтому является хорошим выбором, когда приложение дублирует код.

Эти два типа нелегко заменить, поскольку они не имеют одинаковой распиновки, а наборы команд несовместимы.

Большинство FPGA основаны на ячейках конфигурации SRAM и требуют внешнего устройства конфигурации, часто последовательного флэш-чипа, для перезагрузки битового потока конфигурации при каждом цикле включения питания. [178]

Хранилище прошивки [ править ]

С ростом скорости современных процессоров параллельные флэш-устройства часто работают намного медленнее, чем шина памяти компьютера, к которому они подключены. И наоборот, современная SRAM обеспечивает время доступа менее 10 нс , а DDR2 SDRAM — менее 20 нс. По этой причине часто желательно перенести код, хранящийся во флэш-памяти, в ОЗУ; то есть код копируется из флэш-памяти в ОЗУ перед выполнением, чтобы ЦП мог получить к нему доступ на полной скорости. устройства Прошивка может храниться на последовательном флэш-чипе, а затем копироваться в SDRAM или SRAM при включении устройства. [179] Использование внешнего последовательного флэш-устройства вместо встроенной флэш-памяти устраняет необходимость значительного компромисса с процессом (производственный процесс, который хорош для высокоскоростной логики, обычно не подходит для флэш-памяти, и наоборот). Если принято решение считать прошивку одним большим блоком, обычно добавляют сжатие, чтобы можно было использовать флэш-чип меньшего размера. С 2005 года многие устройства используют последовательную флэш-память NOR, чтобы отказаться от параллельной флэш-памяти NOR для хранения прошивки. Типичные применения последовательной флэш-памяти включают хранение встроенного ПО для жестких дисков , Ethernet адаптеров сетевого интерфейса , модемов DSL и т. д.

Флэш-память как замена жёстким дискам [ править ]

Еще одно недавнее применение флэш-памяти — замена жестких дисков . Флэш-память не имеет механических ограничений и задержек, присущих жестким дискам, поэтому твердотельный накопитель (SSD) привлекателен с точки зрения скорости, шума, энергопотребления и надежности. Флеш-накопители набирают популярность в качестве дополнительных устройств хранения данных для мобильных устройств; они также используются вместо жестких дисков в высокопроизводительных настольных компьютерах и некоторых серверах с RAID и SAN архитектурами .

Остаются некоторые аспекты твердотельных накопителей на базе флэш-памяти, которые делают их непривлекательными. Стоимость гигабайта флэш-памяти остается значительно выше, чем у жестких дисков. [180] Кроме того, флэш-память имеет ограниченное количество циклов P/E ( программирование/стирание ), но, похоже, в настоящее время это находится под контролем, поскольку гарантии на твердотельные накопители на основе флэш-памяти приближаются к гарантиям современных жестких дисков. [181] Кроме того, удаленные файлы на твердотельных накопителях могут сохраняться в течение неопределенного периода времени, прежде чем будут перезаписаны свежими данными; методы стирания или уничтожения или программное обеспечение, которые хорошо работают на магнитных жестких дисках, не влияют на твердотельные накопители, ставя под угрозу безопасность и судебно-медицинскую экспертизу. Однако из-за так называемой команды TRIM , используемой большинством твердотельных накопителей, которая помечает адреса логических блоков, занятые удаленным файлом, как неиспользуемые для включения сборки мусора , программное обеспечение для восстановления данных не может восстановить файлы, удаленные с них.

Для реляционных баз данных или других систем, требующих транзакций ACID , даже скромный объем флэш-памяти может обеспечить значительное ускорение по сравнению с массивами дисков. [182]

В мае 2006 года Samsung Electronics анонсировала два ПК на базе флэш-памяти, Q1-SSD и Q30-SSD, которые должны были стать доступными в июне 2006 года, оба из которых использовали твердотельные накопители емкостью 32 ГБ и, по крайней мере, первоначально были доступны только в Южной Корее . [183] Выпуск Q1-SSD и Q30-SSD был отложен и, наконец, был отправлен в конце августа 2006 года. [184]

Первым доступным ПК с флэш-памятью стал Sony Vaio UX90, предварительный заказ которого был объявлен 27 июня 2006 года, а поставки в Японию начались 3 июля 2006 года с жестким диском с флэш-памятью емкостью 16 ГБ. [185] В конце сентября 2006 года Sony увеличила объем флэш-памяти Vaio UX90 до 32 ГБ. [186]

Твердотельный накопитель предлагался в качестве опции для первого MacBook Air, представленного в 2008 году, а с 2010 года все модели поставлялись с SSD. конца 2011 года в рамках инициативы Intel Ultrabook Начиная с все большее количество ультратонких ноутбуков поставляется со стандартными твердотельными накопителями.

Существуют также гибридные методы, такие как гибридный диск и ReadyBoost , которые пытаются объединить преимущества обеих технологий, используя флэш-память в качестве высокоскоростного энергонезависимого кэша для файлов на диске, к которым часто обращаются, но редко изменяют, например файлы приложений и файлы. файлы операционной системы исполняемые .

Флэш-память как ОЗУ [ править ]

По состоянию на 2012 год [update] предпринимаются попытки использовать флэш-память в качестве основной памяти компьютера, DRAM . [187]

Архивное или долговременное хранение [ править ]

Транзисторы с плавающим затвором во флэш-накопителе удерживают заряд, который представляет данные. Этот заряд со временем постепенно утекает, что приводит к накоплению логических ошибок , также известных как « гниение битов » или «затухание битов». [188]

Хранение данных [ править ]

Неясно, как долго данные во флэш-памяти будут сохраняться в архивных условиях (т. е. при благоприятных температуре и влажности при нечастом доступе с профилактической перезаписью или без нее). компании Atmel на базе флэш-памяти В технических описаниях микроконтроллеров ATmega обычно указывается срок хранения 20 лет при 85 °C (185 °F) и 100 лет при 25 °C (77 °F). [189]

Срок хранения варьируется в зависимости от типа и модели флэш-памяти. При подаче питания и простое заряд транзисторов, хранящих данные, регулярно обновляется прошивкой флэш -накопителя. [188] Способность сохранять данные различается в зависимости от устройства флэш-памяти из-за различий в прошивке, избыточности данных и алгоритмах исправления ошибок . [190]

В статье CMU в 2015 году говорится: «Сегодняшние флэш-устройства, которые не требуют обновления флэш-памяти, имеют типичный срок хранения 1 год при комнатной температуре». И это время удерживания экспоненциально уменьшается с увеличением температуры. Это явление можно смоделировать уравнением Аррениуса . [191] [192]

Конфигурация FPGA [ править ]

Некоторые FPGA основаны на ячейках флэш-конфигурации, которые используются непосредственно как (программируемые) переключатели для соединения внутренних элементов вместе с использованием того же типа транзистора с плавающим затвором, что и ячейки флэш-памяти в устройствах хранения данных. [178]

Промышленность [ править ]

Один источник утверждает, что в 2008 году объем производства и продаж индустрии флэш-памяти составил около 9,1 миллиарда долларов США. Другие источники оценивают объем рынка флэш-памяти в 2006 году в более чем 20 миллиардов долларов США, что составляет более восьми процентов от общего рынка полупроводников и более 34 процентов от общего рынка полупроводниковой памяти. [193] В 2012 году рынок оценивался в $26,8 млрд. [194] Производство чипа флэш-памяти может занять до 10 недель. [195]

Производители [ править ]

Ниже приведены крупнейшие производители флэш-памяти NAND по состоянию на второй квартал 2023 года. [196]

- Самсунг Электроникс – 31,4%

- Киоксиа – 20,6%

- Вестерн Цифровая Корпорация – 12,6%

- СК Хайникс – 18,5%

- Микрон Технология – 12,3%

- Прочие – 8,7% Примечание. SK Hynix приобрела бизнес Intel по производству NAND в конце 2021 г. [197] Kioxia выделилась и была переименована в Toshiba в 2018/2019 году. [198]

Samsung остается крупнейшим производителем флэш-памяти NAND по состоянию на первый квартал 2022 года. [199]

Поставки [ править ]

| Годы) | Дискретные чипы флэш-памяти | Объем данных флэш-памяти ( гигабайты ) | MOSFET с плавающим затвором Ячейки памяти (миллиарды) |

|---|---|---|---|

| 1992 | 26,000,000 [200] | 3 [200] | 24 [а] |

| 1993 | 73,000,000 [200] | 17 [200] | 139 [а] |

| 1994 | 112,000,000 [200] | 25 [200] | 203 [а] |

| 1995 | 235,000,000 [200] | 38 [200] | 300 [а] |

| 1996 | 359,000,000 [200] | 140 [200] | 1,121 [а] |

| 1997 | 477,200,000+ [201] | 317+ [201] | 2,533+ [а] |

| 1998 | 762,195,122 [202] | 455+ [201] | 3,642+ [а] |

| 1999 | 12,800,000,000 [203] | 635+ [201] | 5,082+ [а] |

| 2000–2004 | 134 217 728 000 (НЕ-НЕ) [204] | 1 073 741 824 000 (НЕ-НЕ) [204] | |

| 2005–2007 | ? | ||

| 2008 | 1 226 215 645 (мобильная NAND) [205] | ||

| 2009 | 1 226 215 645+ (мобильная NAND) | ||

| 2010 | 7,280,000,000+ [б] | ||

| 2011 | 8,700,000,000 [207] | ||

| 2012 | 5 151 515 152 ( серийный ) [208] | ||

| 2013 | ? | ||

| 2014 | ? | 59,000,000,000 [209] | 118,000,000,000+ [а] |

| 2015 | 7 692 307 692 (НЕ-НЕ) [210] | 85,000,000,000 [211] | 170,000,000,000+ [а] |

| 2016 | ? | 100,000,000,000 [212] | 200,000,000,000+ [а] |

| 2017 | ? | 148,200,000,000 [с] | 296,400,000,000+ [а] |

| 2018 | ? | 231,640,000,000 [д] | 463,280,000,000+ [а] |

| 2019 | ? | ? | ? |

| 2020 | ? | ? | ? |

| 1992–2020 | 45 358 454 134+ чипов памяти | 758 057 729 630+ гигабайт | 2 321 421 837 044 миллиарда+ клеток |

Помимо отдельных микросхем флэш-памяти, флэш-память также встроена в микроконтроллеры (MCU) и «система-на-кристалле» (SoC). устройства [216] Флэш-память встроена в чипы ARM , [216] которые продали 150 миллиардов единиц по всему миру по состоянию на 2019 год [update], [217] и в программируемых устройствах «система-на-кристалле» (PSoC), которых по состоянию на 2012 год было продано 1,1 миллиарда единиц. [update]. [218] В сумме это составляет как минимум 151,1 миллиарда микросхем MCU и SoC со встроенной флэш-памятью в дополнение к 45,4 миллиардам известных продаж отдельных флэш-чипов по состоянию на 2015 год. [update], что в общей сложности составляет не менее 196,5 миллиардов чипов, содержащих флэш-память.

Масштабируемость Flash [ править ]

Благодаря своей относительно простой структуре и высокой потребности в большей емкости флэш-память NAND является наиболее агрессивно масштабируемой технологией среди электронных устройств . Жесткая конкуренция среди нескольких ведущих производителей только усиливает агрессивность в сокращении правил проектирования МОП-транзисторов с плавающим затвором или технологических узлов. [102] Хотя ожидаемые сроки сокращения составляют два раза каждые три года в соответствии с исходной версией закона Мура , недавно в случае флэш-памяти NAND этот процесс был ускорен до двух раз каждые два года.

| ITRS или компания | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|---|---|---|---|---|---|---|---|---|---|

| Дорожная карта ITRS Flash на 2011 год [219] | 32 нм | 22 нм | 20 нм | 18 нм | 16 нм | ||||

| Обновленная дорожная карта ITRS Flash [220] | 17 нм | 15 нм | 14 нм | ||||||

| Samsung [219] [220] [221] (Samsung 3D NAND) [220] | 35–20 нм [32] | 27 нм | 21 нм ( МЛК , ТСХ ) | 19–16 нм 19–10 нм (МСХ, ТСХ) [222] | 19–10 нм V-NAND (24 л) | 16–10 нм V-NAND (32 л) | 16–10 нм | 12–10 нм | 12–10 нм |

| Микрон , Интел [219] [220] [221] | 34–25 нм | 25 нм | 20 нм (МЛК + Гонконг) | 20 нм (ТСХ) | 16 нм | 16 нм 3D-НЕ-НЕ | 16 нм 3D-НЕ-НЕ | 12 нм 3D-НЕ-НЕ | 12 нм 3D-НЕ-НЕ |

| Тошиба , WD ( СанДиск ) [219] [220] [221] | 43–32 нм 24 нм (Тошиба) [223] | 24 нм | 19 морских миль (МЛХ, ТСХ) | 15 нм | 15 нм 3D-НЕ-НЕ | 15 нм 3D-НЕ-НЕ | 12 нм 3D-НЕ-НЕ | 12 нм 3D-НЕ-НЕ | |

| СК Хайникс [219] [220] [221] | 46–35 нм | 26 нм | 20 нм (МЛК) | 16 нм | 16 нм | 16 нм | 12 нм | 12 нм |

Поскольку размер ячеек флэш-памяти MOSFET достигнет минимального предела 15–16 нм, дальнейшее увеличение плотности флэш-памяти будет обусловлено TLC (3 бита на ячейку) в сочетании с вертикальным укладкой плоскостей памяти NAND. Уменьшение срока службы и увеличение частоты неисправимых ошибок по битам, сопровождающие уменьшение размера объекта, могут быть компенсированы улучшенными механизмами исправления ошибок. [224] Даже с учетом этих достижений может оказаться невозможным экономически масштабировать вспышку до меньших и меньших размеров, поскольку количество удерживающих электронов уменьшается. Многие многообещающие новые технологии (такие как FeRAM , MRAM , PMC , PCM , ReRAM и другие) находятся на стадии исследования и разработки как возможные более масштабируемые замены флэш-памяти. [225]

Хронология [ править ]

| Дата введения | Название чипа | Емкость пакета памяти Мегабиты (Мб), Гигабиты (Гб), Терабиты (Тб) | Тип вспышки | Тип ячейки | Слои или Стеки слоев | Производитель(и) | Процесс | Область | Ссылка |

|---|---|---|---|---|---|---|---|---|---|

| 1984 | ? | ? | НИ | СЛК | 1 | Тошиба | ? | ? | [20] |

| 1985 | ? | 256 КБ | НИ | СЛК | 1 | Тошиба | 2000 нм | ? | [29] |

| 1987 | ? | ? | NAND | СЛК | 1 | Тошиба | ? | ? | [1] |

| 1989 | ? | 1 Мб | НИ | СЛК | 1 | Сик, Intel | ? | ? | [29] |

| 4 Мб | NAND | СЛК | 1 | Тошиба | 1000 нм | ||||

| 1991 | ? | 16 Мб | НИ | СЛК | 1 | Мицубиси | 600 нм | ? | [29] |

| 1993 | DD28F032SA | 32 Мб | НИ | СЛК | 1 | Интел | ? | 280 мм² | [226] [227] |

| 1994 | ? | 64 Мб | НИ | СЛК | 1 | НЭК | 400 нм | ? | [29] |

| 1995 | ? | 16 Мб | ДИНАР | СЛК | 1 | Мицубиси, Хитачи | ? | ? | [29] [228] |

| NAND | СЛК | 1 | Тошиба | ? | ? | [229] | |||

| 32 Мб | NAND | СЛК | 1 | Хитачи, Самсунг, Тошиба | ? | ? | [29] | ||

| 34 Мб | Серийный | СЛК | 1 | СанДиск | |||||

| 1996 | ? | 64 Мб | NAND | СЛК | 1 | Хитачи, Мицубиси | 400 нм | ? | [29] |

| КЛК | 1 | НЭК | |||||||

| 128 Мб | NAND | СЛК | 1 | Самсунг, Хитачи | ? | ||||

| 1997 | ? | 32 Мб | НИ | СЛК | 1 | Интел, Шарп | 400 нм | ? | [230] |

| NAND | СЛК | 1 | АМД, Фуджицу | 350 нм | |||||

| 1999 | ? | 256 Мб | NAND | СЛК | 1 | Тошиба | 250 нм | ? | [29] |

| МЛК | 1 | Хитачи | 1 | ||||||

| 2000 | ? | 32 Мб | НИ | СЛК | 1 | Тошиба | 250 нм | ? | [29] |

| 64 Мб | НИ | КЛК | 1 | СТМикроэлектроника | 180 нм | ||||

| 512 Мб | NAND | СЛК | 1 | Тошиба | ? | ? | [110] | ||

| 2001 | ? | 512 Мб | NAND | МЛК | 1 | Хитачи | ? | ? | [29] |

| 1 Гибит | NAND | МЛК | 1 | Samsung | |||||

| 1 | Тошиба, СанДиск | 160 нм | ? | [231] | |||||

| 2002 | ? | 512 Мб | НРОМ | МЛК | 1 | Сайфун | 170 нм | ? | [29] |

| 2 ГБ | NAND | СЛК | 1 | Самсунг, Тошиба | ? | ? | [232] [233] | ||

| 2003 | ? | 128 Мб | НИ | МЛК | 1 | Интел | 130 нм | ? | [29] |

| 1 ГБ | NAND | МЛК | 1 | Хитачи | |||||

| 2004 | ? | 8 ГБ | NAND | СЛК | 1 | Samsung | 60 нм | ? | [232] |

| 2005 | ? | 16 Гб | NAND | СЛК | 1 | Samsung | 50 нм | ? | [32] |

| 2006 | ? | 32 ГБ | NAND | СЛК | 1 | Samsung | 40 нм | ||

| 7 апреля | ТГАМ | 128 ГБ | Сложенное NAND | СЛК | Тошиба | 56 нм | 252 мм² | [48] | |

| 7 сентября | ? | 128 ГБ | Сложенное NAND | СЛК | Хайникс | ? | ? | [49] | |

| 2008 | ТГБМ | 256 ГБ | Сложенное NAND | СЛК | Тошиба | 43 нм | 353 мм² | [50] | |

| 2009 | ? | 32 ГБ | NAND | ТСХ | Тошиба | 32 нм | 113 мм² | [30] | |

| 64 ГБ | NAND | КЛК | Тошиба, СанДиск | 43 нм | ? | [30] [31] | |||

| 2010 | ? | 64 ГБ | NAND | СЛК | Хайникс | 20 нм | ? | [234] | |

| ТСХ | Samsung | 20 нм | ? | [32] | |||||

| ТГБМ2 | 1 Тб | Сложенное NAND | КЛК | Тошиба | 32 нм | 374 мм² | [51] | ||

| 2011 | КЛМКГ8ГЕ4А | 512 ГБ | Сложенное NAND | МЛК | Samsung | ? | 192 мм² | [235] | |

| 2013 | ? | ? | NAND | СЛК | СК Хайникс | 16 нм | ? | [234] | |

| 128 ГБ | V-NAND | ТСХ | Samsung | 10 нм | ? | ||||

| 2015 | ? | 256 ГБ | V-NAND | ТСХ | Samsung | ? | ? | [222] | |

| 2017 | еУФС 2.1 | 512 ГБ | V-NAND | ТСХ | 8 из 64 | Samsung | ? | ? | [8] |

| 768 ГБ | V-NAND | КЛК | Тошиба | ? | ? | [236] | |||

| KLUFG8R1EM | 4 Тб | Сложенный V-NAND | ТСХ | Samsung | ? | 150 мм² | [8] | ||

| 2018 | ? | 1 Тб | V-NAND | КЛК | Samsung | ? | ? | [237] | |

| 1,33 Тб | V-NAND | КЛК | Тошиба | ? | 158 мм² | [238] [239] | |||

| 2019 | ? | 512 ГБ | V-NAND | КЛК | Samsung | ? | ? | [59] [60] | |

| 1 Тб | V-NAND | ТСХ | СК Хайникс | ? | ? | [240] | |||

| еУФС 2.1 | 1 Тб | Сложенный V-NAND [241] | КЛК | 16 из 64 | Samsung | ? | 150 мм² | [59] [60] [242] | |

| 2023 | еУФС 4.0 | 8 Тб | 3D-НЕ-НЕ | КЛК | 232 | микрон | ? | ? | [243] |

См. также [ править ]

- eMMC

- Контроллер флэш-памяти

- Шестнадцатеричный формат файла Intel

- Список файловых систем флэш-памяти

- Список производителей контроллеров флэш-памяти

- microSDXC (до 2 ТБ ) и последующий формат Secure Digital Ultra емкости ( SDUC ) с поддержкой карт емкостью до 128 ТиБ.

- Замена флэшки NOR

- Открытая рабочая группа по интерфейсу флэш-памяти NAND

- Оперативная память (RMM)

- Универсальное флэш-хранилище

- Безопасность USB-накопителя

- Написать усиление

Пояснительные примечания [ править ]

- ↑ Перейти обратно: Перейти обратно: а б с д и ж г час я дж к л м Одноуровневая ячейка (1 бит на ячейку ) до 2009 года. Многоуровневая ячейка (до 4 бит или полбайта на ячейку) поступила в продажу в 2009 году. [30] [31]

- ^ флэш- Поставки чипов памяти в 2010 г.:

- НОР – 3,64 миллиарда [206]

- NAND – 3,64 миллиарда+ ( оценка )

- ^ Поставки данных флэш-памяти в 2017 году:

- NAND Энергонезависимая память (NVM) – 85 эксабайт ( оценка ) [213]

- Твердотельный накопитель (SSD) – 63,2 эксабайта [214]

- ^ Поставки данных флэш-памяти в 2018 г. ( оценка )

Ссылки [ править ]

- ↑ Перейти обратно: Перейти обратно: а б с «1987: Toshiba выпускает флэш-память NAND» . электронная неделя . 11 апреля 2012 года . Проверено 20 июня 2019 г.

- ^ «Технический и экономический учебник по флэш-накопителям» . FlashStorage.com . 30 марта 2015 г. Архивировано из оригинала 20 июля 2015 г.

- ^ «Руководство по флэш-памяти» (PDF) . Кингстон Технология . 2012. МКФ-283УС. Архивировано (PDF) из оригинала 19 октября 2023 года . Проверено 4 декабря 2023 г.

- ^ Бауэр, Родерик (6 марта 2018 г.). «HDD против SSD: какое будущее ждет системы хранения данных?» . Бэкблэйз . Архивировано из оригинала 22 декабря 2022 года.

- ^ «Введение в функцию обнаружения последовательного присутствия модуля памяти» (PDF) . Технология Микрон . ТН-04-42. Архивировано (PDF) из оригинала 26 июля 2022 года . Проверено 1 июня 2022 г.

- ^ «Обнаружение последовательного присутствия — Технический справочник» (PDF) . Техасские инструменты . Январь 1998 г. SMMU001. Архивировано (PDF) из оригинала 4 декабря 2023 года.

- ^ Шилов, Антон (30 января 2019 г.). «Samsung начинает производство хранилища eUFS 2.1 емкостью 1 ТБ для смартфонов» . АнандТех . Архивировано из оригинала 2 ноября 2023 года.

- ↑ Перейти обратно: Перейти обратно: а б с д Шилов, Антон (5 декабря 2017 г.). «Samsung начинает производство флэш-памяти UFS NAND объемом 512 ГБ: 64-слойная V-NAND, скорость чтения 860 МБ/с» . АнандТех . Архивировано из оригинала 3 ноября 2023 года.

- ^ Ким, Внутренний; Чо, Джи-Хо; Чон, Вупио; Пак, Иль-хан; Пак, Хён Ук; Ким, Ду-Хен; Канг, Дэвон; Ли, Сонхун; Ли, Джи-Сан; Ким, Вонтэ; Парк, Жизнь; Ан, Ян-ло; Ли, Джиён; Ли, Чон Хун; Ким, Тишина; Юн, Хён Джун; Ты, Джедоег; Чой, Наён; Квон, Йелим; Ким, Нахён; Ян, Хваджун; Пак, Чонхун; Сон, Сынхван; Пак, Ёнха; Бан, Джинбэ; Хун, Саньци; Чон, Бёнхун; Ким, Хён Джин; Ли, Чунан; и др. (2017). 11,4 64-стековая флэш-память WL 3D V-NAND емкостью 512 ГБ, 3 бита на ячейку . Международная конференция по твердотельным схемам . Сан-Франциско: IEEE . пп. 202–203. дои : 10.1109/ISSCC.2017.7870331 . ISBN 978-1-5090-3758-2 . ISSN 2376-8606 . S2CID 206998691 .

- ^ Тайсон, Марк. «Samsung поддерживает смартфоны eUFS 2.1 емкостью 1 ТБ» . Гексус . Архивировано из оригинала 23 апреля 2023 года.

- ↑ Перейти обратно: Перейти обратно: а б с «Не просто вспышка на сковороде» . Экономист . Рейтер . 11 марта 2006 г. Архивировано из оригинала 21 ноября 2023 г. . Проверено 10 сентября 2019 г.

- ^ Без, Р.; Пировано, А. (2019). Достижения в области энергонезависимой памяти и технологий хранения данных . Издательство Вудхед . ISBN 9780081025857 .

- ^ «1960 - Демонстрация металлооксидно-полупроводникового (МОП) транзистора» . Кремниевый двигатель . Музей истории компьютеров . Архивировано из оригинала 10 апреля 2023 года.

- ↑ Перейти обратно: Перейти обратно: а б с д «1971: Представлено многоразовое полупроводниковое ПЗУ» . Механизм хранения . Музей истории компьютеров . 11 июня 2018 года. Архивировано из оригинала 10 августа 2023 года . Проверено 19 июня 2019 г.

- ↑ Перейти обратно: Перейти обратно: а б Фулфорд, Адель (24 июня 2002 г.). «Невоспетый герой» . Форбс . Архивировано из оригинала 3 марта 2008 года . Проверено 18 марта 2008 г.

- ^ Тайсон, Джефф (29 августа 2000 г.). «Как работает ПЗУ» . Как все работает . Архивировано из оригинала 2 декабря 2023 года . Проверено 10 сентября 2019 г.

- ^ США 4531203 Фудзио Масуока

- ^ Полупроводниковое запоминающее устройство и способ его изготовления.

- ^ «Флэш-память NAND: 25 лет изобретений, разработок – Хранение данных – Новости и обзоры» . eWeek.com . Архивировано из оригинала 18 августа 2014 года . Проверено 18 августа 2014 г.

- ↑ Перейти обратно: Перейти обратно: а б «Toshiba: изобретатель флэш-памяти» . Тошиба . Архивировано из оригинала 20 июня 2019 года . Проверено 20 июня 2019 г.

- ^ Масуока, Ф.; Асано, М.; Ивахаси, Х.; Комуро, Т.; Танака, С. (декабрь 1984 г.). Новая вспышка E 2 Ячейка PROM с использованием технологии тройного поликремния . 1984 Международная встреча по электронным устройствам . Сан-Франциско. стр. 464–467. дои : 10.1109/IEDM.1984.190752 . S2CID 25967023 .

- ^ Масуока, Ф.; Момодоми, М.; Ивата, Ю.; Широта, Р. (1987). «Новая СППЗУ сверхвысокой плотности и флэш-ЭСППЗУ с ячейкой структуры NAND». Встреча электронных устройств, Международная конференция 1987 г. IEDM 1987. IEEE . стр. 552–555. дои : 10.1109/IEDM.1987.191485 .

- ^ Таль, Арье (февраль 2002 г.). «Технология флэш-памяти NAND и NOR: разработчик должен взвесить варианты использования флэш-памяти» . Архивировано из оригинала 28 июля 2010 года . Проверено 31 июля 2010 г.

- ^ «Группа H8S/2357, H8S/2357F-ZTATTM, H8S/2398F-ZTATTM Руководство по аппаратному обеспечению» . Ренесас . Октябрь 2004 г. с. 574. Архивировано из оригинала 9 января 2023 года . Проверено 23 января 2012 г.