1T-SRAM

Эта статья включает список литературы , связанную литературу или внешние ссылки , но ее источники остаются неясными, поскольку в ней отсутствуют встроенные цитаты . ( декабрь 2012 г. ) |

| памяти компьютера и хранения данных компьютера Типы |

|---|

| Неустойчивый |

| Энергонезависимый |

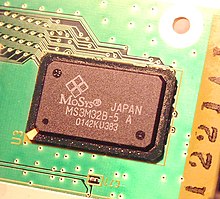

1T-SRAM — это технология псевдостатической оперативной памяти (PSRAM), представленная компанией MoSys, Inc. в сентябре 1998 года, которая предлагает высокоплотную альтернативу традиционной статической памяти с произвольным доступом (SRAM) во встроенных приложениях памяти. Mosys использует ячейку хранения с одним транзистором (битовую ячейку), такую как динамическое запоминающее устройство с произвольным доступом (DRAM), но окружает битовую ячейку схемой управления, которая делает память функционально эквивалентной SRAM (контроллер скрывает все операции, специфичные для DRAM, такие как предварительная зарядка и обновить). 1T-SRAM (и PSRAM в целом) имеет стандартный однотактный интерфейс SRAM и воспринимается окружающей логикой так же, как и SRAM.

Благодаря однотранзисторной битовой ячейке 1T-SRAM меньше обычной (шеститранзисторной или «6T») SRAM и ближе по размеру и плотности к встроенной DRAM ( eDRAM ). В то же время 1T-SRAM имеет производительность, сравнимую с SRAM при плотности в несколько мегабит, потребляет меньше энергии, чем eDRAM, и производится по стандартному логическому процессу CMOS , как и обычная SRAM.

MoSys продает 1T-SRAM как физический IP для встроенного (на кристалле) использования в «система на кристалле приложениях » (SOC). Он доступен для различных литейных процессов, включая Chartered, SMIC, TSMC и UMC. Некоторые инженеры используют термины 1T-SRAM и «встроенная DRAM» как взаимозаменяемые, поскольку некоторые литейные заводы предоставляют 1T-SRAM MoSys как «eDRAM». Однако другие литейные заводы предлагают 1T-SRAM в качестве отдельного предложения.

Технология

[ редактировать ]1T SRAM представляет собой массив небольших банков (обычно 128 строк × 256 бит/строка, 32 килобита всего ), соединенных с кэшем SRAM размером с банк и интеллектуальным контроллером. Хотя короткие строки слов неэффективны по сравнению с обычной DRAM, они обеспечивают гораздо более высокие скорости, поэтому массив может выполнять полный анализ и предварительную зарядку (цикл RAS) при каждом доступе, обеспечивая высокоскоростной произвольный доступ. Каждый доступ осуществляется к одному банку, что позволяет одновременно обновлять неиспользуемые банки. Кроме того, каждая строка, считываемая из активного банка, копируется в кэш SRAM размером с банк . В случае повторных обращений к одному банку, при которых не остается времени на циклы обновления, есть два варианта: либо все обращения происходят к разным строкам, и в этом случае все строки будут обновляться автоматически, либо к некоторым строкам осуществляется повторный доступ. В последнем случае кэш предоставляет данные и дает время для обновления неиспользуемой строки активного банка.

Было четыре поколения 1T-SRAM: [ когда? ]

- Оригинальный 1T-SRAM

- Примерно вдвое меньше 6T-SRAM, меньше половины мощности.

- 1Т-СРАМ-М

- Вариант с более низким энергопотреблением в режиме ожидания для таких приложений, как сотовые телефоны.

- 1Т-СРАМ-Р

- Включает ECC для снижения уровня программных ошибок . Чтобы избежать штрафа за площадь, он использует меньшие битовые ячейки, которые имеют более высокую частоту ошибок, но ECC более чем компенсирует это.

- 1Т-СРАМ-Q

- В этой версии «четверной плотности» используется немного нестандартный производственный процесс для производства складчатого конденсатора меньшего размера, что позволяет снова уменьшить размер памяти вдвое по сравнению с 1T-SRAM-R. Это немного увеличивает затраты на производство пластин, но не мешает изготовлению логических транзисторов, как это происходит с обычной конструкцией конденсаторов DRAM.

Сравнение с другими технологиями встроенной памяти

[ редактировать ]1T-SRAM имеет скорость, сравнимую с 6T-SRAM (при плотности в несколько мегабит). Это значительно более высокая скорость, чем у eDRAM, а вариант с «четверной плотностью» лишь немного больше (заявлено 10–15%). В большинстве литейных процессов конструкции с использованием eDRAM требуют дополнительных (и дорогостоящих) масок и этапов обработки, что компенсирует стоимость более крупного кристалла 1T-SRAM. Кроме того, некоторые из этих этапов требуют очень высоких температур и должны выполняться после того, как логические транзисторы сформированы, что может привести к их повреждению.

1T-SRAM также доступен в форме устройства (IC). GameCube была первой системой видеоигр , которая использовала 1T-SRAM в качестве основной памяти; GameCube имеет несколько выделенных устройств 1T-SRAM. 1T-SRAM также используется в преемнике GameCube — Wii .

Это не то же самое, что 1T DRAM , которая представляет собой «безконденсаторную» ячейку DRAM, построенную с использованием паразитного канального конденсатора SOI- транзисторов, а не дискретного конденсатора.

MoSys заявляет следующие размеры массивов 1T-SRAM:

| Узел процесса | 250 нм | 180 нм | 130 нм | 90 нм | 65 нм | 45 нм | |

|---|---|---|---|---|---|---|---|

| 6Т-СРАМ | битовая ячейка | 7.56 | 4.65 | 2.43 | 1.36 | 0.71 | 0.34 |

| с накладными расходами | 11.28 | 7.18 | 3.73 | 2.09 | 1.09 | 0.52 | |

| 1T-SRAM | битовая ячейка | 3.51 | 1.97 | 1.10 | 0.61 | 0.32 | 0.15 |

| с накладными расходами | 7.0 | 3.6 | 1.9 | 1.1 | 0.57 | 0.28 | |

| 1Т-СРАМ-Q | битовая ячейка | 0.50 | 0.28 | 0.15 | 0.07 | ||

| с накладными расходами | 1.05 | 0.55 | 0.29 | 0.14 | |||

См. также

[ редактировать ]Патент США 7,146,454 «Скрытие обновления в архитектуре 1T-SRAM»* (от Cypress Semiconductor ) описывает аналогичную систему для сокрытия обновления DRAM с использованием кэша SRAM.

Ссылки

[ редактировать ]- Глазковски, Питер Н. (13 сентября 1999 г.). «MoSys объясняет технологию 1T-SRAM: уникальная архитектура скрывает обновление, заставляет DRAM работать как SRAM» (PDF) . Отчет микропроцессора . 13 (12) . Проверено 6 октября 2007 г.

- Джонс, Марк-Эрик (14 октября 2003 г.). 1T-SRAM-Q: технология четырехкратной плотности снижает требования к быстрорастущей памяти (PDF) (отчет). МоСис, Инк . Проверено 6 октября 2007 г.

- Домашняя страница MoSys

- В патенте США № 6 256 248 показан массив DRAM, лежащий в основе 1T-SRAM.

- В патенте США № 6 487 135 термин «1T DRAM» используется для описания внутреннего устройства 1T-SRAM.

- Молодежь, Techfor (16 декабря 2002 г.). «Макросы 1-T SRAM предварительно настроены для быстрой интеграции в конструкции SoC» . Архивировано из оригинала 20 июля 2019 г. Проверено 21 августа 2020 г.

- Катальдо, Энтони (16 декабря 2002 г.). «NEC и Mosys расширяют границы встроенной DRAM» . ЭЭ Таймс . ISSN 0192-1541 . Проверено 6 октября 2007 г.