Соединение периферийных компонентов

| Локальная шина PCI | |

Три 5-вольтовых 32-битных слота расширения PCI на материнской плате (кронштейн для ПК с левой стороны) | |

| Год создания | 22 июня 1992 г [1] |

|---|---|

| Создано | Интел |

| Заменяет | ИСА , ЕИСА , МКА , ВЛБ |

| Заменено | AGP для графики (1997 г.), PCI Express (2004 г.) |

| Ширина в битах | 32 или 64 |

| Скорость | Полудуплекс : [2]

133 МБ /с (32 бит при 33 МГц – стандартная конфигурация) 266 МБ/с (32 бит при 66 МГц) 266 МБ/с (64 бит при 33 МГц) 533 МБ/с (64 бит при 66 МГц) |

| Стиль | Параллельно |

| Интерфейс горячего подключения | Необязательный |

| Веб-сайт | www |

Соединение периферийных компонентов ( PCI ) [3] представляет собой локальную компьютерную шину для подключения аппаратных устройств к компьютеру и является частью стандарта локальной шины PCI. Шина PCI поддерживает функции, имеющиеся на шине процессора , но в стандартизированном формате, независимом от собственной шины конкретного процессора . Устройства, подключенные к шине PCI, кажутся мастеру шины подключенными непосредственно к его собственной шине, и им назначаются адреса в адресном пространстве процессора . [4] Это параллельная шина, синхронизированная с тактовой частотой одной шины . Подключенные устройства могут иметь форму либо интегральной схемы, установленной на материнской плате (называемой планарным устройством в спецификации PCI), либо карты расширения , которая вставляется в слот. Локальная шина PCI была впервые реализована в компьютерах, совместимых с IBM PC , где она заменила комбинацию нескольких медленных слотов промышленной стандартной архитектуры (ISA) и одного быстрого слота локальной шины VESA (VLB) в качестве конфигурации шины. Впоследствии он был принят для других типов компьютеров. Типичные карты PCI, используемые в ПК, включают: сетевые карты , звуковые карты , модемы , дополнительные порты, такие как универсальная последовательная шина ( USB ) или последовательный порт , карты ТВ-тюнера и жесткого диска хост-адаптеры . PCI Видеокарты заменили карты ISA и VLB, пока растущая потребность в пропускной способности не переросла возможности PCI. Затем предпочтительным интерфейсом для видеокарт стал порт ускоренной графики (AGP), расширенная версия PCI, прежде чем уступить место PCI Express. [5]

Первая версия PCI, обнаруженная в розничных настольных компьютерах, представляла собой 32-битную шину с тактовой частотой шины 33 МГц и сигнализацией 5 В , хотя стандарт PCI 1.0 предусматривал 64-битный вариант. также [ нужны разъяснения ] У них есть одна установочная выемка на карте. Версия 2.0 стандарта PCI представила слоты 3,3 В, физически отличающиеся перевернутым физическим разъемом для предотвращения случайной вставки карт с напряжением 5 В. Универсальные карты, которые могут работать при любом напряжении, имеют два выреза. Версия 2.1 стандарта PCI представила дополнительную работу на частоте 66 МГц. Серверно-ориентированный вариант PCI, PCI Extended ( PCI-X ), работал на частотах до 133 МГц для PCI-X 1.0 и до 533 МГц для PCI-X 2.0. Внутренний разъем для карт ноутбука, получивший название Mini PCI , был представлен в версии 2.2 спецификации PCI. Шина PCI также была принята в качестве стандарта внешнего разъема ноутбука — CardBus . [6] Первая спецификация PCI была разработана Intel , но последующая разработка стандарта стала обязанностью PCI Special Interest Group ( PCI-SIG ). [7]

PCI и PCI-X иногда называют параллельным PCI или обычным PCI. [8] чтобы отличить их технологически от своего более недавнего преемника PCI Express , который принял последовательную архитектуру на основе полос. [9] [10] Расцвет PCI на рынке настольных компьютеров пришелся примерно на 1995–2005 годы. [9] PCI и PCI-X устарели для большинства целей и практически исчезли из многих других современных материнских плат с 2013 года; однако по состоянию на 2020 год они все еще распространены на некоторых современных настольных компьютерах. [update] в целях обратной совместимости и относительно низкой стоимости производства. Другое распространенное современное применение параллельного PCI — промышленные ПК , где многие используемые здесь специализированные карты расширения так и не перешли на PCI Express, как и некоторые карты ISA. Многие виды устройств, ранее доступные на картах расширения PCI, теперь обычно интегрированы в материнские платы или доступны в версиях USB и PCI Express.

История

[ редактировать ]

Работа над PCI началась в Лаборатории архитектуры Intel (IAL, также Лаборатория разработки архитектуры) c. 1990 . Команда, состоящая в основном из инженеров IAL, определила архитектуру и разработала экспериментальный набор микросхем и платформу (Saturn) в партнерстве с группами компании, занимающимися системами настольных ПК, и организациями, занимающимися основными логическими продуктами.

PCI был немедленно использован в серверах, заменив архитектуру Micro Channel (MCA) и расширенную отраслевую стандартную архитектуру (EISA) в качестве предпочтительной шины расширения сервера. В обычных ПК PCI медленнее вытеснял VLB и не получил значительного проникновения на рынок до конца 1994 года в ПК Pentium второго поколения . К 1996 году VLB практически исчез, и производители внедрили PCI даже для компьютеров Intel 80486 (486). [11] EISA продолжала использоваться наряду с PCI до 2000 года. Apple Computer приняла PCI для профессиональных Power Macintosh компьютеров (заменив NuBus ) в середине 1995 года, а потребительскую линейку продуктов Performa (заменив LC Processor Direct Slot (PDS)) в середине 1996 года.

Однако за пределами серверного рынка 64-битная версия обычного PCI на практике оставалась редкостью. [12] хотя он использовался, например, на всех G4 (после iMac) G3 и компьютерах Power Macintosh . [13]

В более поздних версиях PCI были добавлены новые функции и улучшения производительности, включая стандарт 66 МГц 3,3 В и PCI-X 133 МГц , а также адаптация сигнализации PCI к другим форм-факторам. И PCI-X 1.0b, и PCI-X 2.0 обратно совместимы с некоторыми стандартами PCI. Эти версии использовались на серверном оборудовании, но оборудование потребительских ПК оставалось почти полностью 32-битным, 33 МГц и 5 В.

PCI-SIG представила последовательный PCI Express в c. 2004 . С тех пор производители материнских плат стали включать все меньше слотов PCI в пользу нового стандарта. По состоянию на конец 2013 года многие новые материнские платы вообще не имеют слотов PCI. [ нужна ссылка ]

| Спецификация | Год | Сводка изменений [15] |

|---|---|---|

| PCI 1.0 | 1992 | Оригинальный выпуск |

| PCI 2.0 | 1993 | Характеристики встроенного разъема и карты расширения |

| PCI 2.1 | 1995 | Включены пояснения и добавлена глава о 66 МГц. |

| PCI 2.2 | 1998 | Встроенные ECN и улучшенная читаемость. |

| PCI 2.3 | 2002 | Включены ECN, исправлены ошибки и удалены карты расширения с ключом только на 5 В. |

| PCI 3.0 | 2004 | Удалена поддержка разъема системной платы с ключом на 5,0 В. |

Автоматическая конфигурация

[ редактировать ]PCI обеспечивает отдельную память и адресное пространство портов ввода-вывода, отображаемых в памяти, для семейства процессоров x86 , 64 и 32 бита соответственно. Адреса в этих адресных пространствах назначаются программным обеспечением. Третье адресное пространство, называемое пространством конфигурации PCI , в котором используется фиксированная схема адресации, позволяет программному обеспечению определять объем памяти и адресное пространство ввода-вывода, необходимое каждому устройству. Каждое устройство может запрашивать до шести областей памяти или пространства портов ввода-вывода (I/O) через свои регистры пространства конфигурации.

В типичной системе встроенное ПО (или операционная система ) запрашивает все шины PCI во время запуска (через пространство конфигурации PCI ), чтобы узнать, какие устройства присутствуют и какие системные ресурсы (пространство памяти, пространство ввода-вывода, линии прерываний и т. д.). ) каждому нужен. Затем он распределяет ресурсы и сообщает каждому устройству, каково их распределение.

Пространство конфигурации PCI также содержит небольшой объем информации о типе устройства, которая помогает операционной системе выбирать для нее драйверы устройств или, по крайней мере, вести диалог с пользователем о конфигурации системы.

Устройства могут иметь встроенное постоянное запоминающее устройство (ПЗУ), содержащее исполняемый код для x86 или PA-RISC процессоров , драйвер открытой прошивки или дополнительное ПЗУ . Обычно они необходимы для устройств, используемых во время запуска системы, до загрузки драйверов устройств операционной системой.

Кроме того, существуют таймеры задержки PCI , которые представляют собой механизм, позволяющий устройствам управления шиной PCI справедливо распределять шину PCI. «Справедливо» в данном случае означает, что устройства не будут использовать такую большую часть доступной пропускной способности шины PCI, что другие устройства не смогут выполнить необходимую работу. Обратите внимание: это не относится к PCI Express.

Это работает так: каждое устройство PCI, которое может работать в режиме мастера шины, должно иметь таймер, называемый таймером задержки, который ограничивает время, в течение которого устройство может удерживать шину PCI. Таймер запускается, когда устройство становится владельцем шины, и ведет отсчет со скоростью тактовой частоты PCI. Когда счетчик достигнет нуля, устройство обязано освободить шину. Если никакие другие устройства не ожидают владения шиной, оно может просто снова захватить шину и передать больше данных. [16]

Прерывания

[ редактировать ]Устройства должны следовать протоколу, чтобы линии запроса на прерывание (IRQ) могли быть общими. Шина PCI включает четыре линии прерываний, от INTA# до INTD#, все из которых доступны каждому устройству. До восьми устройств PCI используют одну и ту же линию IRQ (от LNKA до LNKH) в системах x86 с поддержкой APIC . Линии прерываний не подключаются параллельно, как другие линии шины PCI. Позиции линий прерываний меняются между слотами, поэтому то, что для одного устройства выглядит как линия INTA#, для следующего будет INTB#, а для следующего за ним INTC#. Однофункциональные устройства обычно используют свой INTA# для сигнализации прерываний, поэтому нагрузка устройства распределяется довольно равномерно по четырем доступным линиям прерываний. Это облегчает распространенную проблему совместного использования прерываний.

Сопоставление линий прерываний PCI с линиями системных прерываний через хост-мост PCI зависит от реализации. или операционной системы для конкретной платформы Код прошивки должен знать это и установить поле «строки прерывания» в пространстве конфигурации каждого устройства, указывающее, к какому IRQ оно подключено.

Линии прерываний PCI активируются по уровню . Это было выбрано вместо запуска по фронту, чтобы получить преимущество при обслуживании общей линии прерываний, а также для обеспечения надежности: прерывания, запускаемые по фронту, легко пропустить.

В более поздних версиях спецификации PCI добавлена поддержка прерываний, сигнализируемых сообщениями . В этой системе устройство сигнализирует о необходимости обслуживания, выполняя запись в память, а не путем подключения выделенной линии. Это смягчает проблему нехватки линий прерываний. Даже если векторы прерываний по-прежнему являются общими, они не страдают от проблем совместного использования прерываний, запускаемых по уровню. Это также решает проблему маршрутизации, поскольку запись в память не изменяется непредсказуемо между устройством и хостом. Наконец, поскольку сигнализация сообщений является внутриполосной , она решает некоторые проблемы синхронизации, которые могут возникнуть при опубликованных операциях записи и внеполосных линиях прерываний.

PCI Express вообще не имеет физических линий прерываний. Он использует исключительно прерывания, сигнализируемые сообщениями.

Стандартные характеристики оборудования

[ редактировать ]

Эти спецификации представляют наиболее распространенную версию PCI, используемую в обычных ПК:

- 33,33 МГц Тактовая частота с синхронной передачей

- Пиковая скорость передачи 133 МБ /с (133 МБ /с) для ширины шины 32 бита (33,33 МГц × 32 бита ÷ 8 бит/байт = 133 МБ/с)

- 32-битная ширина шины

- 32- или 64-битное адресное пространство памяти (4 ГиБ или 16 ЭйБ )

- 32-битное пространство порта ввода-вывода

- Конфигурационное пространство 256 байт (на каждое устройство)

- 5-вольтовая сигнализация

- Переключение отраженной волны

Спецификация PCI также предоставляет опции для передачи сигналов 3,3 В, ширины шины 64 бита и тактовой частоты 66 МГц, но они обычно не встречаются за пределами поддержки PCI-X на серверных материнских платах.

Арбитр шины PCI выполняет арбитраж шины между несколькими ведущими устройствами на шине PCI. На шине PCI может находиться любое количество мастеров шины, а также запросов к шине. Каждому мастеру шины выделяется одна пара сигналов запроса и разрешения.

Напряжение карты и кодирование

[ редактировать ]

Типичные карты PCI имеют одну или две ключевые выемки, в зависимости от их сигнального напряжения. Карты, требующие 3,3 В, имеют выемку на расстоянии 56,21 мм от задней панели карты; те, которым требуется 5 вольт, имеют выемку в 104,41 мм от задней панели. Это позволяет устанавливать карты только в слоты с напряжением, которое они поддерживают. «Универсальные карты», поддерживающие любое напряжение, имеют обе ключевые выемки.

Распиновка разъема

[ редактировать ]Разъем PCI определяется как имеющий 62 контакта на каждой стороне краевого разъема , но два или четыре из них заменены ключевыми выемками, поэтому карта имеет 60 или 58 контактов с каждой стороны. Сторона A относится к «стороне пайки», а сторона B относится к «стороне компонентов»: если держать карту разъемом вниз, на виде стороны A задняя панель будет находиться справа, тогда как на виде стороны B задняя панель будет слева. Распиновка сторон B и A следующая, если смотреть на разъем материнской платы (контакты A1 и B1 расположены ближе всего к задней панели). [15] [17] [18]

| Приколоть | Сторона Б | Сторона А | Комментарии | ||

|---|---|---|---|---|---|

| 1 | −12 V | ТРЕСТ# | Контакты порта JTAG (опционально) | ||

| 2 | ТСК | +12 V | |||

| 3 | Земля | ТМС | |||

| 4 | ТДО | ТДИ | |||

| 5 | +5 V | +5 V | |||

| 6 | +5 V | ПОКА# | Прерывающие контакты (открытый сток) | ||

| 7 | ИНТБ# | ИНТС# | |||

| 8 | INTD# | +5 V | |||

| 9 | ПРСНТ1# | Сдержанный | Низкий уровень указывает на требуемую мощность 7,5 или 25 Вт. | ||

| 10 | Сдержанный | ИОПВР | +5 В или +3,3 В | ||

| 11 | PRSNT2# | Сдержанный | Низкий уровень указывает на требуемую мощность 7,5 или 15 Вт. | ||

| 12 | Земля | Земля | Ключевой вырез для карт с поддержкой напряжения 3,3 В | ||

| 13 | Земля | Земля | |||

| 14 | Сдержанный | 3,3 В доп. | Резервное питание (опционально) | ||

| 15 | Земля | RST# | Сброс шины | ||

| 16 | КЛК | ИОПВР | Часы 33/66 МГц | ||

| 17 | Земля | ГНТ# | Предоставление шины от материнской платы к карте | ||

| 18 | REQ# | Земля | Запрос шины от карты к материнской плате | ||

| 19 | ИОПВР | МСП# | Событие управления питанием (опция) 3,3 В, открытый сток, активный низкий уровень. [19] | ||

| 20 | нашей эры[31] | нашей эры[30] | Шина адреса/данных (верхняя половина) | ||

| 21 | нашей эры[29] | +3.3 V | |||

| 22 | Земля | нашей эры[28] | |||

| 23 | нашей эры[27] | нашей эры[26] | |||

| 24 | нашей эры[25] | Земля | |||

| 25 | +3.3 V | нашей эры[24] | |||

| 26 | C/BE[3]# | ИДСЕЛЬ | |||

| 27 | нашей эры[23] | +3.3 V | |||

| 28 | Земля | нашей эры[22] | |||

| 29 | нашей эры[21] | нашей эры[20] | |||

| 30 | нашей эры[19] | Земля | |||

| 31 | +3.3 V | нашей эры[18] | |||

| 32 | нашей эры[17] | нашей эры[16] | |||

| 33 | C/BE[2]# | +3.3 V | |||

| 34 | Земля | РАМКА# | Идет трансфер на автобусе | ||

| 35 | ИРДИ# | Земля | Инициатор готов | ||

| 36 | +3.3 V | ТРДИ# | Цель готова | ||

| 37 | РАЗРАБОТКА# | Земля | Цель выбрана | ||

| 38 | PCIXCAP | Земля | ОСТАНАВЛИВАТЬСЯ# | поддержка PCI-X ; Целевые запросы остановлены | |

| 39 | ЗАМОК# | +3.3 V | Заблокированная транзакция | ||

| 40 | ПЕРР# | СМБКЛК | СДОНЕ | Ошибка четности; Часы SMBus или Snoop Done (устарело) | |

| 41 | +3.3 V | СМБДАТ | СБО# | Данные SMBus или отсрочка Snoop (устарело) | |

| 42 | ГОЛОВА# | Земля | Системная ошибка | ||

| 43 | +3.3 V | О | Равенство над AD[31:00] и C/BE[3:0]# | ||

| 44 | К/БЭ[1]# | нашей эры[15] | Шина адреса/данных (верхняя половина) | ||

| 45 | нашей эры[14] | +3.3 V | |||

| 46 | Земля | нашей эры[13] | |||

| 47 | нашей эры[12] | нашей эры[11] | |||

| 48 | нашей эры[10] | Земля | |||

| 49 | M66EN | Земля | AD[09] | ||

| 50 | Земля | Земля | Ключевой паз для 5 карт с поддержкой V | ||

| 51 | Земля | Земля | |||

| 52 | AD[08] | К/БЭ[0]# | Шина адреса/данных (нижняя половина) | ||

| 53 | AD[07] | +3.3 V | |||

| 54 | +3.3 V | AD[06] | |||

| 55 | AD[05] | AD[04] | |||

| 56 | AD[03] | Земля | |||

| 57 | Земля | AD[02] | |||

| 58 | AD[01] | AD[00] | |||

| 59 | ИОПВР | ИОПВР | |||

| 60 | ACK64# | REQ64# | Для 64-битного расширения; нет подключения для 32-битных устройств. | ||

| 61 | +5 V | +5 V | |||

| 62 | +5 V | +5 V | |||

64-битный PCI расширяет это за счет дополнительных 32 контактов с каждой стороны, которые обеспечивают AD[63:32], C/BE[7:4]#, сигнал четности PAR64, а также ряд контактов питания и заземления.

| Заземляющий контакт | Опорное значение нулевого напряжения |

|---|---|

| Контакт питания | Подает питание на карту PCI |

| Выходной контакт | Управляется картой PCI, принимается материнской платой |

| Выход инициатора | Управляется мастером/инициатором, принимается целью |

| сигнал ввода/вывода | Может управляться инициатором или целью, в зависимости от операции |

| Целевой результат | Управляемый целью, полученный инициатором/мастером |

| Вход | Управляется материнской платой, принимается картой PCI |

| Открытый слив | Может быть понижено и/или воспринято несколькими картами |

| Сдержанный | В настоящее время не используется, не подключайте |

Большинство линий подключаются к каждому слоту параллельно. Исключениями являются:

- Каждый слот имеет собственный выход REQ# и вход GNT# от арбитра материнской платы.

- Каждый слот имеет собственную линию IDSEL, обычно подключенную к определенной линии AD.

- TDO подключается последовательно к TDI следующего слота. Карты без поддержки JTAG должны подключать TDI к TDO, чтобы не разрывать цепочку.

- PRSNT1# и PRSNT2# для каждого слота имеют свои собственные подтягивающие резисторы на материнской плате. Материнская плата может (но не обязана) распознавать эти контакты, чтобы определить наличие карт PCI и их требования к питанию.

- REQ64# и ACK64# индивидуально подтягиваются только в 32-битных слотах.

- Выводы прерываний от INTA# до INTD# подключены ко всем слотам в разном порядке. (INTA# в одном слоте соответствует INTB# в следующем и INTC# в следующем.)

Примечания:

- IOPWR составляет +3,3 В или +5 В, в зависимости от объединительной платы. Слоты также имеют выступ в одном из двух мест, который предотвращает вставку карт, не имеющих соответствующего паза, что указывает на поддержку этого стандарта напряжения. Универсальные карты имеют оба ключевых выреза и используют IOPWR для определения уровней сигналов ввода-вывода.

- PCI SIG настоятельно рекомендует передачу сигналов PCI 3,3 В. [15] требуется его поддержка начиная со стандартной версии 2.3, [17] но большинство материнских плат ПК используют вариант с напряжением 5 В. Таким образом, хотя многие доступные в настоящее время карты PCI поддерживают оба варианта и имеют два ключевых выреза, указывающих на это, на рынке все еще существует большое количество карт только с 5 V.

- Вывод M66EN — это дополнительная земля на шинах PCI 5 В, которые есть на большинстве материнских плат ПК. Карты и материнские платы, не поддерживающие работу на частоте 66 МГц, также заземляют этот контакт. Если все участники поддерживают работу на частоте 66 МГц, подтягивающий резистор на материнской плате повышает уровень этого сигнала и включается работа на частоте 66 МГц. Вывод по-прежнему подключен к земле через разделительные конденсаторы на каждой плате, чтобы сохранить функцию экранирования переменного тока .

- Вывод PCIXCAP является дополнительным заземлением на шинах и картах PCI. Если все карты и материнская плата поддерживают протокол PCI-X , подтягивающий резистор на материнской плате повышает уровень этого сигнала и включается работа PCI-X. Вывод по-прежнему подключен к земле через разделительные конденсаторы на каждой плате, чтобы сохранить функцию экранирования переменного тока.

- По крайней мере один из PRSNT1# и PRSNT2# должен быть заземлен картой. Выбранная комбинация указывает общую потребляемую мощность карты (25 Вт, 15 Вт или 7,5 Вт).

- SBO# и SDONE — это сигналы от контроллера кэша к текущей цели. Они не являются выходами инициатора, но окрашены таким образом, потому что являются целевыми входами.

- PME# ( 19 A ) — событие управления питанием (дополнительно), которое поддерживается в PCI версии 2.2 и выше. Это сигнал 3,3 В с открытым стоком и активным низким уровнем. [19] Карты PCI могут использовать этот сигнал для отправки и получения PME напрямую через разъем PCI, что устраняет необходимость в специальном кабеле Wake-on-LAN . [20]

Смешивание 32-битных и 64-битных карт PCI в слотах разной ширины.

[ редактировать ]

Большинство 32-битных карт PCI будут правильно работать в 64-битных слотах PCI-X, но тактовая частота шины будет ограничена тактовой частотой самой медленной карты, что является неотъемлемым ограничением топологии общей шины PCI. Например, если периферийное устройство PCI 2.3, 66 МГц установлено в шину PCI-X с частотой 133 МГц, вся объединительная плата шины будет ограничена частотой 66 МГц. Чтобы обойти это ограничение, многие материнские платы имеют две или более шины PCI/PCI-X, одна из которых предназначена для использования с высокоскоростными периферийными устройствами PCI-X, а другая — для периферийных устройств общего назначения.

Многие 64-битные карты PCI-X предназначены для работы в 32-битном режиме при установке в более короткие 32-битные разъемы с некоторой потерей производительности. [21] [22] Примером этого является 64-битная интерфейсная карта Adaptec 29160 SCSI . [23] Однако некоторые 64-битные карты PCI-X не работают в стандартных 32-битных слотах PCI. [24] [ ненадежный источник? ]

При установке 64-битной карты PCI-X в 32-битный слот 64-битная часть краевого разъема карты останется неподключенной и выступающей. Для этого необходимо, чтобы компоненты материнской платы не располагались таким образом, чтобы механически блокировать выступающую часть краевого разъема карты.

Физические размеры

[ редактировать ]Высота кронштейнов PCI:

Длина карты PCI (стандартный кронштейн и 3,3 В): [27]

- Короткая карта: 169,52 мм;

- Длинная карта: 313,78 мм.

Длина карты PCI (низкопрофильный кронштейн и 3,3 В): [28]

- МД1: 121,79 мм;

- МД2: 169,52 мм;

- МД3: 243,18 мм.

-

Полноразмерный кронштейн

-

Низкопрофильная карта с полноразмерным кронштейном.

Мини PCI

[ редактировать ]

Mini PCI был добавлен в PCI версии 2.2 для использования в ноутбуках и некоторых маршрутизаторах; [ нужна ссылка ] он использует 32-битную шину 33 МГц с питанием (только 3,3 В; 5 В ограничено 100 мА) и поддержкой управления шиной и DMA . Стандартный размер карт Mini PCI составляет примерно четверть от их полноразмерных аналогов. Доступа к карте снаружи корпуса нет, в отличие от настольных PCI-карт с кронштейнами, несущими разъемы. Это ограничивает виды функций, которые может выполнять карта Mini PCI.

Было разработано множество устройств Mini PCI, таких как Wi-Fi , Fast Ethernet , Bluetooth , модемы (часто Winmodems ), звуковые карты , криптографические ускорители , контроллеры SCSI , IDE - ATA , SATA и комбинированные карты. Mini PCI-PCI Карты Mini PCI можно использовать с обычным оборудованием, оснащенным PCI, с помощью преобразователей . На смену Mini PCI пришла гораздо более узкая мини-карта PCI Express.

Технические подробности Mini PCI

[ редактировать ]Карты Mini PCI имеют максимальное энергопотребление 2 Вт, что ограничивает функциональность, которую можно реализовать в этом форм-факторе. Они также необходимы для поддержки сигнала CLKRUN# PCI, используемого для запуска и остановки тактовой частоты PCI в целях управления питанием.

Существует три форм-фактора карт : карты типа I, типа II и типа III. Разъемы карт, используемые для каждого типа, включают: Тип I и II используют 100-контактный разъем для стекирования, а Тип III использует 124-контактный краевой разъем, т. е. разъем для типов I и II отличается от разъема для типа III, где разъем находится на краю карты, как в случае с SO-DIMM . Дополнительные 24 контакта обеспечивают дополнительные сигналы, необходимые для обратного направления ввода -вывода через системный разъем (аудио, AC-Link , LAN , интерфейс телефонной линии). Карты типа II имеют установленные разъемы RJ11 и RJ45. Эти карты должны быть расположены на краю компьютера или док-станции, чтобы порты RJ11 и RJ45 можно было установить для внешнего доступа.

| Тип | Карта включена внешний край хост-система |

Разъем | Размер (мм × мм × мм) |

комментарии |

|---|---|---|---|---|

| Я | Нет | 100-контактный штабелирование |

7.5 × 70 × 45 | Большой размер Z (7,5 мм) |

| ИБ | 5.5 × 70 × 45 | Меньший размер Z (5,5 мм) | ||

| ИМА | Да | 17.44 × 70 × 45 | Большой размер Z (17,44 мм) | |

| МИБ | 5.5 × 78 × 45 | Меньший размер Z (5,5 мм) | ||

| IIIА | Нет | 124-контактный край карты |

2.4 × 59.6 × 50.95 | Больший размер Y (50,95 мм) |

| IIIБ | 2.4 × 59.6 × 44.6 | Меньший размер Y (44,6 мм) |

Mini PCI отличается от 144-контактного Micro PCI. [29]

Транзакции по шине PCI

[ редактировать ]Трафик шины PCI состоит из серии транзакций шины PCI. Каждая транзакция состоит из фазы адреса, за которой следуют одна или несколько фаз данных . Направление фаз данных может быть от инициатора к цели (транзакция записи) или наоборот (транзакция чтения), но все фазы данных должны быть в одном направлении. Любая сторона может приостановить или остановить этапы передачи данных в любой момент. (Одним из распространенных примеров является низкопроизводительное устройство PCI, которое не поддерживает пакетные транзакции и всегда останавливает транзакцию после первой фазы данных.)

Любое PCI-устройство может инициировать транзакцию. Во-первых, он должен запросить разрешение у арбитра шины PCI на материнской плате. Арбитр предоставляет разрешение одному из запрашивающих устройств. Инициатор начинает фазу адреса с широковещательной рассылки 32-битного адреса плюс 4-битного кода команды, а затем ждет ответа цели. Все остальные устройства проверяют этот адрес, и одно из них отвечает через несколько циклов.

64-битная адресация осуществляется с использованием двухэтапной фазы адреса. Инициатор передает младшие 32 бита адреса в сопровождении специального командного кода «цикла двойного адреса». Устройства, не поддерживающие 64-битную адресацию, могут просто не ответить на этот код команды. В следующем цикле инициатор передает старшие 32 бита адреса плюс реальный код команды. С этого момента транзакция работает идентично. Для обеспечения совместимости с 32-битными PCI-устройствами запрещено использовать цикл двойного адреса, если в этом нет необходимости, т. е. если все старшие биты адреса равны нулю.

В то время как шина PCI передает 32 бита за фазу данных, инициатор передает 4 сигнала разрешения активного младшего байта, указывающие, какие 8-битные байты следует считать значимыми. В частности, запись должна затрагивать только разрешенные байты в целевом устройстве PCI. Они не имеют большого значения для чтения из памяти, но чтение ввода-вывода может иметь побочные эффекты. Стандарт PCI явно допускает фазу данных без включенных байтов, которая должна вести себя как неактивная.

Адресные пространства PCI

[ редактировать ]PCI имеет три адресных пространства: память, адрес ввода-вывода и конфигурационное.

Адреса памяти имеют размер 32 бита (опционально 64 бита), поддерживают кэширование и могут быть пакетными транзакциями.

Адреса ввода-вывода предназначены для совместимости с адресным пространством портов ввода-вывода архитектуры Intel x86 . Хотя спецификация шины PCI допускает пакетные транзакции в любом адресном пространстве, большинство устройств поддерживают ее только для адресов памяти, а не ввода-вывода.

Наконец, пространство конфигурации PCI обеспечивает доступ к 256 байтам специальных регистров конфигурации для каждого устройства PCI. Каждый слот PCI имеет свой собственный диапазон адресов конфигурационного пространства. Регистры используются для настройки памяти устройств и диапазонов адресов ввода-вывода, на которые они должны отвечать от инициаторов транзакций. При первом включении компьютера все устройства PCI реагируют только на доступ к их конфигурационному пространству. BIOS компьютера сканирует устройства и назначает им диапазоны адресов памяти и ввода-вывода.

Если адрес не запрошен каким-либо устройством, фаза адреса инициатора транзакции истечет по тайм-ауту, в результате чего инициатор прервет операцию. В случае чтения в этом случае принято указывать все единицы для значения считанных данных (0xFFFFFFFF). Поэтому устройства PCI обычно стараются избегать использования значения «все единицы» в важных регистрах состояния, чтобы такую ошибку можно было легко обнаружить программным обеспечением.

Коды команд PCI

[ редактировать ]Существует 16 возможных 4-битных кодов команд, 12 из них назначены. За исключением уникального цикла двойного адреса, младший бит кода команды указывает, являются ли следующие фазы данных чтением (данные передаются от цели к инициатору) или записью (данные отправляются от инициатора к цели). Цели PCI должны проверять код команды, а также адрес и не реагировать на фазы адреса, которые указывают неподдерживаемый код команды.

Команды, которые относятся к строкам кэша, зависят от пространства конфигурации PCI правильной настройки регистра размера строки кэша ; их нельзя использовать до тех пор, пока это не будет сделано.

- 0000: Подтверждение прерывания

- Это особая форма цикла чтения, неявно адресованная контроллеру прерываний, который возвращает вектор прерывания. 32-битное поле адреса игнорируется. Одной из возможных реализаций является создание цикла подтверждения прерывания на шине ISA с использованием моста шины PCI/ISA. Эта команда предназначена для совместимости с IBM PC ; если на шине PCI нет контроллера прерываний в стиле Intel 8259 , этот цикл никогда не нужно использовать.

- 0001: Специальный цикл

- Этот цикл представляет собой специальную широковещательную запись системных событий, которые могут быть интересны карте PCI. Поле адреса специального цикла игнорируется, но за ним следует фаза данных, содержащая сообщение полезной нагрузки. Определенные в данный момент сообщения сообщают, что процессор по какой-либо причине останавливается (например, для экономии энергии). Ни одно устройство никогда не реагирует на этот цикл; он всегда завершается прерыванием ведущего устройства после того, как данные остаются на шине в течение как минимум 4 циклов.

- 0010: Чтение ввода-вывода

- При этом выполняется чтение из пространства ввода-вывода. Предоставляются все 32 бита адреса чтения, так что устройство может (по соображениям совместимости) реализовать регистры ввода-вывода размером менее 4 байт. Если байт разрешает запрос данных за пределами диапазона адресов, поддерживаемого устройством PCI (например, 4-байтовое чтение с устройства, которое поддерживает только 2 байта адресного пространства ввода-вывода), он должен быть завершен целевым прерыванием. Допускаются несколько циклов данных с использованием линейного (простого приращения) порядка пакетов.

- Стандарт PCI не поощряет использование пространства ввода-вывода в новых устройствах, предпочитая, чтобы как можно больше делалось посредством сопоставления основной памяти.

- 0011: Запись ввода/вывода

- При этом выполняется запись в пространство ввода-вывода.

- 010 x : Зарезервировано

- Устройство PCI не должно отвечать на цикл адреса этими кодами команд.

- 0110: Чтение памяти

- При этом выполняется цикл чтения из области памяти. Поскольку наименьший объем памяти, который разрешено реализовать устройству PCI, составляет 16 байт. [17] [15] : §6.5.2.1 два младших бита адреса не нужны на этапе адреса; эквивалентная информация будет поступать на этапах передачи данных в виде сигналов выбора байта. Вместо этого они определяют порядок, в котором должны быть возвращены пакетные данные. [17] [15] : §3.2.2.2 Если устройство не поддерживает запрошенный порядок, оно должно предоставить первое слово, а затем отключиться.

- Если пространство памяти помечено как «предварительно выборочное», то целевое устройство должно игнорировать сигналы выбора байта при чтении памяти и всегда возвращать 32 действительных бита.

- 0111: Запись в память

- Это работает аналогично чтению памяти. Сигналы выбора байта более важны при записи, поскольку невыбранные байты не должны записываться в память.

- Как правило, запись PCI выполняется быстрее, чем чтение PCI, поскольку устройство может буферизовать входящие данные записи и быстрее освобождать шину. Для чтения он должен задержать фазу данных до тех пор, пока данные не будут получены.

- 100 х : Зарезервировано

- Устройство PCI не должно отвечать на цикл адреса этими кодами команд.

- 1010: Чтение конфигурации

- Это похоже на чтение ввода-вывода, но чтение осуществляется из пространства конфигурации PCI. Устройство должно отвечать только в том случае, если младшие 11 бит адреса определяют функцию и регистр, которые оно реализует, и если установлен специальный сигнал IDSEL. Он должен игнорировать старшие 21 бит. Пакетное чтение (с использованием линейного приращения) разрешено в пространстве конфигурации PCI.

- В отличие от пространства ввода-вывода, стандартные регистры конфигурации PCI определены таким образом, что операции чтения никогда не нарушают состояние устройства. Устройство может иметь регистры пространства конфигурации, превышающие стандартные 64 байта, что имеет побочные эффекты чтения, но это случается редко. [30]

- Доступ к пространству конфигурации часто имеет задержку в несколько циклов, чтобы позволить линиям IDSEL стабилизироваться, что делает их медленнее, чем другие формы доступа. Кроме того, доступ к пространству конфигурации требует многошаговой операции, а не одной машинной инструкции. Таким образом, лучше избегать их во время повседневной работы PCI-устройства.

- 1011: Запись конфигурации

- Это работает аналогично чтению конфигурации.

- 1100: Многократное чтение памяти

- Эта команда идентична обычному чтению памяти, но включает подсказку о том, что длинный пакет чтения будет продолжаться за пределами текущей строки кэша, и цель должна выполнить внутреннюю предварительную выборку большого объема данных. Целевому объекту всегда разрешается рассматривать это как синоним общего чтения памяти.

- 1101: Цикл двойного адреса

- При доступе к адресу памяти, для представления которого требуется более 32 бит, фаза адреса начинается с этой команды и младших 32 бит адреса, за которым следует второй цикл с фактической командой и старшими 32 битами адреса. Цели PCI, которые не поддерживают 64-битную адресацию, могут просто рассматривать это как еще один зарезервированный командный код и не реагировать на него. Этот код команды можно использовать только с ненулевым старшим адресным словом; запрещено использовать этот цикл без необходимости.

- 1110: Строка чтения памяти

- Эта команда идентична обычной операции чтения из памяти, но включает подсказку о том, что чтение продолжится до конца строки кэша. Целевому объекту всегда разрешается рассматривать это как синоним общего чтения памяти.

- 1111: Запись в память и аннулирование

- Эта команда идентична общей записи в память, но гарантирует, что будет записана одна или несколько целых строк кэша с включенным выбором всех байтов. Это оптимизация кэшей обратной записи, отслеживающих шину. Обычно кэш обратной записи, содержащий «грязные» данные, должен прерывать операцию записи на время, достаточное для того, чтобы сначала записать свои собственные «грязные» данные. Если запись выполняется с помощью этой команды, данные, подлежащие обратной записи, гарантированно будут нерелевантными и могут просто стать недействительными в кэше обратной записи.

- Эта оптимизация влияет только на отслеживающий кеш и не имеет никакого значения для цели, которая может рассматривать ее как синоним команды записи в память.

Задержка шины PCI

[ редактировать ]Вскоре после обнародования спецификации PCI было обнаружено, что длительные транзакции некоторых устройств из-за медленных подтверждений, длинных пакетов данных или какой-либо комбинации могут вызвать опустошение или переполнение буфера в других устройствах. Рекомендации по срокам отдельных этапов в версии 2.0 стали обязательными в версии 2.1: [31] : 3

- Цель должна иметь возможность завершить фазу начальных данных (подтвердить TRDY# и/или STOP#) в течение 16 циклов после начала транзакции.

- Инициатор должен завершить каждую фазу данных (подтвердить IRDY#) в течение 8 циклов.

Кроме того, начиная с версии 2.1, все инициаторы, способные передавать более двух фаз данных, должны реализовывать программируемый таймер задержки. Таймер начинает отсчет тактовых циклов при запуске транзакции (инициатор устанавливает FRAME#). Если время таймера истекло и арбитр удалил GNT#, то инициатор должен прекратить транзакцию при следующей законной возможности. Обычно это следующая фаза данных, но транзакции записи в память и аннулирования должны продолжаться до конца строки кэша.

Отложенные транзакции

[ редактировать ]Устройства, неспособные удовлетворить эти ограничения по времени, должны использовать комбинацию опубликованных записей (для записи в память) и отложенных транзакций (для других операций записи и всех операций чтения). В отложенной транзакции целевой объект записывает транзакцию (включая данные записи) внутри себя и прерывает (указывает STOP#, а не TRDY#) первую фазу данных. Инициатор должен повторить ту же транзакцию позже. Тем временем цель выполняет транзакцию внутри себя и ожидает повторной транзакции. Когда повторная транзакция видна, доставляется буферизованный результат.

Устройство может быть целью других транзакций при выполнении одной отложенной транзакции; он должен запомнить тип транзакции, адрес, выбор байта и (если запись) значение данных и выполнять только правильную транзакцию.

Если цель имеет ограничение на количество отложенных транзакций, которые она может записать внутри (простые цели могут устанавливать ограничение в 1), она заставит эти транзакции повторить попытку без их записи. Они будут обработаны после завершения текущей отложенной транзакции. Если два инициатора попытаются выполнить одну и ту же транзакцию, результат отложенной транзакции, начатой одним, может быть доставлен другому; это безвредно.

Цель отказывается от отложенной транзакции, когда повторная попытка доставляет буферизованный результат, шина сбрасывается или когда 2 15 =32768 тактов (приблизительно 1 мс) проходят без повторных попыток. Последнее никогда не должно происходить при нормальной работе, но предотвращает тупик всей шины в случае сброса или неисправности одного инициатора.

Шинные мосты PCI

[ редактировать ]Стандарт PCI позволяет соединять несколько независимых шин PCI с помощью шинных мостов, которые при необходимости перенаправляют операции с одной шины на другую. Хотя PCI, как правило, не использует много шинных мостов, системы PCI Express используют множество мостов PCI-to-PCI, обычно называемых корневым портом PCI Express ; каждый слот PCI Express представляет собой отдельную шину, соединенную мостом с остальными. Хост-мост PCI (обычно северный мост на платформах x86) соединяет процессор, основную память и шину PCI. [32]

Опубликовано пишет

[ редактировать ]Обычно, когда шинный мост обнаруживает транзакцию на одной шине, которую необходимо перенаправить на другую, исходная транзакция должна дождаться завершения перенаправленной транзакции, прежде чем результат будет готов. Одно заметное исключение возникает в случае записи в память. Здесь мост может записывать данные записи внутри себя (если у него есть место) и сигнализировать о завершении записи до завершения переадресованной записи. Или, вернее, еще до того, как оно началось. Такие записи «отправлено, но еще не доставлено» называются «отправленными записями» по аналогии с почтовым сообщением. Хотя они открывают большие возможности для повышения производительности, правила, определяющие дозволенность, довольно сложны. [33]

Объединение, слияние и свертывание

[ редактировать ]Стандарт PCI позволяет мостам шины преобразовывать несколько транзакций шины в одну более крупную транзакцию в определенных ситуациях. Это может повысить эффективность шины PCI.

Объединение

[ редактировать ]Транзакции записи по последовательным адресам могут быть объединены в более длительную пакетную запись, при условии, что порядок доступа в пакете такой же, как порядок исходной записи. Разрешено вставлять дополнительные фазы данных с отключенными разрешениями всех байтов, если записи почти последовательные.

Слияние

[ редактировать ]Множественные записи в непересекающиеся части одного и того же слова могут быть объединены в одну запись с включением разрешения нескольких байтов. В этом случае записи, которые были представлены шинному мосту в определенном порядке, объединяются, поэтому при пересылке они происходят одновременно.

Сворачивание

[ редактировать ]Несколько операций записи в один и тот же байт или байты нельзя объединить, например, выполнив только вторую запись и пропустив первую запись, которая была перезаписана. Это связано с тем, что спецификация PCI допускает, что запись может иметь побочные эффекты.

Сигналы шины PCI

[ редактировать ]Транзакции шины PCI контролируются пятью основными управляющими сигналами, два из которых управляются инициатором транзакции (FRAME# и IRDY#), а три управляются целью (DEVSEL#, TRDY# и STOP#). Существует два дополнительных арбитражных сигнала (REQ# и GNT#), которые используются для получения разрешения на инициацию транзакции. Все они являются активными-низкими , что означает, что активное или утвержденное состояние представляет собой низкое напряжение . Подтягивающие резисторы на материнской плате гарантируют, что они останутся высокими (неактивными или отключенными ), если они не управляются каким-либо устройством, но шина PCI не зависит от резисторов при изменении уровня сигнала; все устройства повышают уровень сигналов в течение одного цикла, прежде чем перестать подавать сигналы.

Синхронизация сигнала

[ редактировать ]Все сигналы шины PCI дискретизируются по нарастающему фронту тактового сигнала. Сигналы номинально изменяются по спадающему фронту тактовой частоты, что дает каждому устройству PCI примерно половину тактового цикла, чтобы решить, как реагировать на сигналы, которые оно наблюдает по нарастающему фронту, и одну половину тактового цикла, чтобы передать свой ответ другому устройству. .

Шина PCI требует, чтобы при каждом изменении сигнала шины PCI устройством, управляющим сигналом шины PCI, один цикл обработки между моментом прекращения передачи сигнала одним устройством и запуском другого устройства должен пройти . Без этого может быть период, когда оба устройства передают сигнал, что будет мешать работе шины.

Сочетание этого оборотного цикла и требования поддерживать высокий уровень линии управления в течение одного цикла, прежде чем прекратить его управление, означает, что каждая из основных линий управления должна находиться в высоком состоянии в течение как минимум двух циклов при смене владельцев. Протокол шины PCI разработан таким образом, что это редко является ограничением; только в некоторых особых случаях (особенно при быстрых транзакциях ) необходимо вводить дополнительную задержку для удовлетворения этого требования.

Арбитраж

[ редактировать ]Любое устройство на шине PCI, способное выступать в качестве мастера шины, может инициировать транзакцию с любым другим устройством. Чтобы гарантировать, что одновременно инициируется только одна транзакция, каждый мастер должен сначала дождаться сигнала разрешения шины GNT# от арбитра, расположенного на материнской плате. Каждое устройство имеет отдельную линию запроса REQ#, которая запрашивает шину, но арбитр может «припарковать» сигнал разрешения шины на любом устройстве, если текущих запросов нет.

Арбитр может удалить GNT# в любое время. Устройство, потерявшее GNT#, может завершить свою текущую транзакцию, но не может начать ее (путем установки FRAME#), если только оно не увидит, что GNT# подтвердил цикл до его начала.

Арбитр также может предоставить GNT# в любое время, в том числе во время транзакции другого мастера. Во время транзакции утверждается либо FRAME#, либо IRDY#, либо оба; когда оба сигнала отключены, шина простаивает. Устройство может инициировать транзакцию в любой момент, когда установлен GNT# и шина простаивает.

Адресная фаза

[ редактировать ]Транзакция шины PCI начинается с фазы адреса . Инициатор (обычно набор микросхем ), видя, что у него есть GNT# и шина простаивает, передает целевой адрес на линии AD[31:0], соответствующую команду (например, чтение памяти или запись ввода-вывода) на C/BE[3:0]# строк и переводит FRAME# в низкий уровень.

Каждое другое устройство проверяет адрес и команду и решает, отвечать ли в качестве цели, выставляя DEVSEL#. Устройство должно отреагировать, установив DEVSEL# в течение 3 циклов. Говорят, что устройства, которые обещают ответить в течение 1 или 2 циклов, имеют «быстрый DEVSEL» или «средний DEVSEL» соответственно. (На самом деле время ответа составляет 2,5 такта, поскольку устройства PCI должны передавать все сигналы на полпериода раньше, чтобы их можно было получить на три такта позже.)

Устройство должно зафиксировать адрес в первом цикле; инициатору необходимо удалить адрес и команду из шины в следующем цикле, еще до получения ответа DEVSEL#. Дополнительное время доступно только для интерпретации адреса и команды после их захвата.

На пятом цикле фазы адреса (или раньше, если все остальные устройства имеют средний DEVSEL или выше) для некоторых диапазонов адресов разрешено всеобъемлющее «вычитающее декодирование». Это обычно используется шинным мостом ISA для адресов в его диапазоне (24 бита для памяти и 16 бит для ввода-вывода).

В шестом цикле, если ответа не было, инициатор может прервать транзакцию, сняв сигнал FRAME#. Это известно как прерывание главного прерывания , и в этом случае мосты шины PCI обычно возвращают данные «все единицы» (0xFFFFFFFF). Поэтому устройства PCI обычно проектируются таким образом, чтобы избежать использования значений «все единицы» в важных регистрах состояния, чтобы такую ошибку можно было легко обнаружить программным обеспечением.

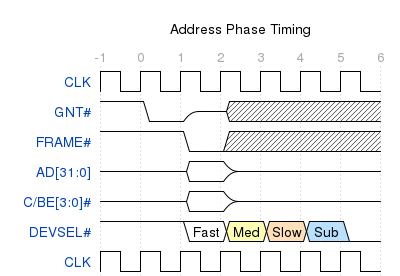

Время фазы адреса

[ редактировать ]Примечания:

- GNT# Не имеет значения после начала цикла

- Адрес действителен только в течение одного цикла.

- C/BE предоставит команду, следующую за включением первого байта фазы данных.

По нарастающему фронту тактового сигнала 0 инициатор наблюдает высокий уровень FRAME# и IRDY#, а низкий GNT#, поэтому он управляет адресом, командой и выставляет FRAME# вовремя для нарастающего фронта тактового сигнала 1. Цели фиксируют адрес и начать его расшифровку. Они могут ответить DEVSEL# вовремя для тактов 2 (быстрый DEVSEL), 3 (средний) или 4 (медленный). Устройства субтрактивного декодирования, не видя другого ответа по такту 4, могут ответить на такте 5. Если ведущее устройство не видит ответа по такту 5, оно завершит транзакцию и удалит FRAME# на такте 6.

TRDY# и STOP# сбрасываются (высокий уровень) во время фазы адреса. Инициатор может установить IRDY#, как только он будет готов передать данные, что теоретически может произойти как только такт 2.

Двухтактный адрес

[ редактировать ]Чтобы разрешить 64-битную адресацию, мастер будет предоставлять адрес в течение двух последовательных циклов. Сначала он отправляет младшие биты адреса с помощью специальной команды «двойного адреса» на C/BE[3:0]#. В следующем цикле он отправляет старшие биты адреса и фактическую команду. Двухадресные циклы запрещены, если старшие биты адреса равны нулю, поэтому устройства, не поддерживающие 64-битную адресацию, могут просто не реагировать на команды двойного цикла.

_ 0_ 1_ 2_ 3_ 4_ 5_ 6_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/

___

GNT# \___/XXXXXXXXXXXXXXXXXXXXXXX

_______

FRAME# \_______________________

___ ___

AD[31:0] -------<___X___>--------------- (Low, then high bits)

___ ___ _______________

C/BE[3:0]# -------<___X___X_______________ (DAC, then actual command)

___________________________

DEVSEL# \___\___\___\___

Fast Med Slow

_ _ _ _ _ _ _ _

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/

0 1 2 3 4 5 6

Доступ к конфигурации

[ редактировать ]Адреса доступа к конфигурационному пространству PCI используют специальное декодирование. Для них младшие адресные строки указывают смещение желаемого регистра конфигурации PCI, а старшие адресные строки игнорируются. Вместо этого дополнительный адресный сигнал, вход IDSEL, должен иметь высокий уровень, прежде чем устройство сможет установить DEVSEL#. Каждый слот подключает отдельную адресную линию старшего порядка к выводу IDSEL и выбирается с помощью горячего кодирования в верхних адресных линиях.

Этапы данных

[ редактировать ]После фазы адреса (точнее, начиная с цикла, когда DEVSEL# переходит в низкий уровень) происходит пакет из одной или нескольких фаз данных . Во всех случаях инициатор подает сигналы выбора активного младшего байта на линиях C/BE[3:0]#, но данные на AD[31:0] могут управляться инициатором (в случае записи) или цель (в случае чтения).

Во время фаз данных строки C/BE[3:0]# интерпретируются как активный младший байт . В случае записи выданные сигналы указывают, какой из четырех байтов шины AD должен быть записан в адресную ячейку. В случае чтения они указывают, какие байты интересуют инициатора. При чтении всегда допустимо игнорировать сигналы разрешения байтов и просто возвращать все 32 бита; ресурсы кэшируемой памяти должны всегда возвращать 32 действительных бита. Разрешения байтов в основном полезны для доступа к пространству ввода-вывода, где чтение имеет побочные эффекты.

Фаза данных со всеми четырьмя отключенными строками C/BE# явно разрешена стандартом PCI и не должна оказывать никакого влияния на цель, кроме как для продвижения адреса в текущем пакетном доступе.

Фаза данных продолжается до тех пор, пока обе стороны не будут готовы завершить передачу и перейти к следующей фазе данных. Инициатор выдает IRDY# ( инициатор готов ), когда ему больше не нужно ждать, в то время как цель утверждает TRDY# ( цель готова ). Какая бы сторона ни предоставляла данные, она должна передать их по шине AD, прежде чем подавать сигнал готовности.

Как только один из участников подтвердит свой сигнал готовности, он не может стать неготовым или иным образом изменить свои управляющие сигналы до конца фазы данных. Получатель данных должен фиксировать шину AD в каждом цикле до тех пор, пока не увидит утвержденные оба IRDY# и TRDY#, что отмечает конец текущей фазы данных и указывает, что только что защелкнутые данные являются словом, которое необходимо передать.

Чтобы поддерживать полную пакетную скорость, отправитель данных затем имеет половину тактового цикла после того, как будет подтверждено как IRDY#, так и TRDY#, для передачи следующего слова на шину AD.

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_ 9_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/

___ _______ ___ ___ ___

AD[31:0] ---<___XXXXXXXXX_______XXXXX___X___X___ (If a write)

___ ___ _______ ___ ___

AD[31:0] ---<___>~~~<XXXXXXXX___X_______X___X___ (If a read)

___ _______________ _______ ___ ___

C/BE[3:0]# ---<___X_______________X_______X___X___ (Must always be valid)

_______________ | ___ | | |

IRDY# x \_______/ x \___________

___________________ | | | |

TRDY# x x \___________________

___________ | | | |

DEVSEL# \___________________________

___ | | | |

FRAME# \___________________________________

_ _ _ _ _ |_ _ |_ |_ |_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/

0 1 2 3 4 5 6 7 8 9

Это продолжает показанный выше цикл адреса, предполагая одиночный цикл адреса со средой DEVSEL, поэтому цель отвечает вовремя для такта 3. Однако на данный момент ни одна из сторон не готова передавать данные. К такту 4 инициатор готов, а цель — нет. На такте 5 оба готовы, и происходит передача данных (как показано вертикальными линиями). На такте 6 цель готова к передаче, а инициатор — нет. На такте 7 инициатор становится готовым, и данные передаются. Для тактов 8 и 9 обе стороны остаются готовыми к передаче данных, и данные передаются с максимально возможной скоростью (32 бита за такт).

В случае чтения тактовый сигнал 2 зарезервирован для переключения шины AD, поэтому цели не разрешается передавать данные по шине, даже если она способна к быстрому DEVSEL.

Быстрый DEVSEL# при чтении

[ редактировать ]Цель, поддерживающая быстрый DEVSEL, теоретически может начать отвечать на чтение в цикле после представления адреса. Однако этот цикл зарезервирован для обновления шины AD. Таким образом, цель не может управлять шиной AD (и, следовательно, не может устанавливать TRDY#) во втором цикле транзакции. Большинство целей не будут такими быстрыми и не будут нуждаться в какой-либо специальной логике для обеспечения выполнения этого условия.

Завершение транзакций

[ редактировать ]Любая сторона может запросить завершение пакета после текущей фазы данных. Простые устройства PCI, которые не поддерживают пакеты из нескольких слов, всегда будут запрашивать это немедленно. Даже устройства, которые поддерживают пакеты, будут иметь некоторые ограничения на максимальную длину, которую они могут поддерживать, например, конец их адресуемой памяти.

Завершение пакета инициатора

[ редактировать ]Инициатор может пометить любую фазу данных как последнюю в транзакции, сняв сигнал FRAME# одновременно с установкой IRDY#. Цикл после того, как цель выставляет TRDY#, окончательная передача данных завершается, обе стороны снимают соответствующие сигналы RDY#, и шина снова простаивает. Ведущее устройство не может отменить подтверждение FRAME# до утверждения IRDY#, а также не может отменить подтверждение FRAME# во время ожидания с установленным IRDY# цели, чтобы установить TRDY#.

Единственным незначительным исключением является прерывание основного прерывания , когда ни одна цель не отвечает DEVSEL#. Очевидно, что в таком случае ждать TRDY# бессмысленно. Однако даже в этом случае мастер должен активировать IRDY# как минимум в течение одного цикла после отмены подтверждения FRAME#. (Обычно ведущее устройство устанавливает IRDY# до получения DEVSEL#, поэтому ему необходимо просто удерживать IRDY# установленным на один цикл дольше.) Это необходимо для обеспечения соблюдения правил синхронизации шины на линии FRAME#.

Прекращение целевого пакета

[ редактировать ]Цель запрашивает инициатора завершить пакет, установив STOP#. Затем инициатор завершит транзакцию, отменив подтверждение FRAME# при следующей законной возможности; если он желает передать больше данных, это продолжится в отдельной транзакции. Есть несколько способов сделать это:

- Отключиться от данных

- Если цель одновременно выдает STOP# и TRDY#, это указывает на то, что цель желает, чтобы это была последняя фаза данных. Например, цель, которая не поддерживает пакетную передачу, всегда будет делать это для принудительной транзакции PCI с одним словом. Это наиболее эффективный способ для цели прекратить взрыв.

- Отключиться без данных

- Если цель выдает STOP# без подтверждения TRDY#, это указывает на то, что цель желает остановиться без передачи данных. STOP# считается эквивалентным TRDY# в целях завершения фазы данных, но данные не передаются.

- Повторить попытку

- Отключение без данных перед передачей каких-либо данных представляет собой повторную попытку , и в отличие от других транзакций PCI, инициаторам PCI необходимо сделать небольшую паузу, прежде чем продолжить операцию. Подробности смотрите в спецификации PCI.

- Целевое прерывание

- Обычно цель содержит DEVSEL#, установленный на последней фазе данных. Однако, если цель отменяет подтверждение DEVSEL# перед отключением без данных (подтверждением STOP#), это указывает на прерывание цели , что является фатальной ошибкой. Инициатор не может повторить попытку и обычно рассматривает это как ошибку шины . Цель не может отменить сигнал DEVSEL# во время ожидания с низким TRDY# или STOP#; он должен сделать это в начале фазы данных.

После отключения, инициированного целью, всегда будет как минимум еще один цикл, чтобы позволить ведущему устройству отменить подтверждение FRAME#. Есть два подслучая, которые занимают одинаковое количество времени, но один требует дополнительной фазы данных:

- Отключить-А

- Если инициатор наблюдает STOP# перед установкой своего собственного IRDY#, то он может завершить пакет, сняв сигнал FRAME# одновременно с установкой IRDY#, завершая пакет после текущей фазы данных.

- Отключить-B

- Если инициатор уже установил IRDY# (без отмены подтверждения FRAME#) к тому времени, когда он наблюдает STOP# цели, он переходит к дополнительной фазе данных. Цель должна дождаться дополнительной фазы данных, удерживая STOP# без TRDY#, прежде чем транзакция сможет завершиться.

Если инициатор завершает пакет в то же время, когда цель запрашивает отключение, дополнительный цикл шины не требуется.

Пакетная адресация

[ редактировать ]Для доступа к пространству памяти слова в пакете могут быть доступны в нескольких порядках. Ненужные младшие биты адреса AD[1:0] используются для передачи запрошенного инициатором порядка. Цель, которая не поддерживает определенный порядок, должна прекратить передачу пакета после первого слова. Некоторые из этих порядков зависят от размера строки кэша, который можно настроить на всех устройствах PCI.

| А[1] | А[0] | Пакетный порядок (с 16-байтовой строкой кэша) |

|---|---|---|

| 0 | 0 | Линейное приращение (0x0C, 0x10, 0x14, 0x18, 0x1C, ...) |

| 0 | 1 | Переключение кэша (0x0C, 0x08, 0x04, 0x00, 0x1C, 0x18, ...) |

| 1 | 0 | Перенос кеша (0x0C, 0x00, 0x04, 0x08, 0x1C, 0x10, ...) |

| 1 | 1 | Зарезервировано (отключение после первой передачи) |

Если начальное смещение в строке кэша равно нулю, все эти режимы сводятся к одному и тому же порядку.

Режимы переключения строк кэша и переноса строк кэша — это две формы выборки строк кэша по критическому слову. Режим переключения выполняет XOR для предоставленного адреса с увеличивающимся счетчиком. Это собственный порядок для процессоров Intel 486 и Pentium. Его преимущество состоит в том, что для его реализации не обязательно знать размер строки кэша.

В версии PCI 2.1 устаревший режим переключения и добавлен режим переноса строк кэша. [31] : 2 где выборка происходит линейно, с переносом в конце каждой строки кэша. Когда одна строка кэша полностью выбрана, выборка переходит к начальному смещению в следующей строке кэша.

Большинство устройств PCI поддерживают только ограниченный диапазон типичных размеров строк кэша; если размер строки кэша запрограммирован на неожиданное значение, они обеспечивают доступ по одному слову.

PCI также поддерживает пакетный доступ к пространству ввода-вывода и конфигурации, но поддерживается только линейный режим. (Этот метод используется редко и может содержать ошибки на некоторых устройствах; они могут его не поддерживать, но также не обеспечивают должным образом доступ по одному слову.)

Примеры транзакций

[ редактировать ]Это максимально возможная скорость записи четырех слов, завершаемая ведущим устройством:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

___ ___ ___ ___ ___

AD[31:0] ---<___X___X___X___X___>---<___>

___ ___ ___ ___ ___

C/BE[3:0]# ---<___X___X___X___X___>---<___>

| | | | ___

IRDY# ^^^^^^^^\______________/ ^^^^^

| | | | ___

TRDY# ^^^^^^^^\______________/ ^^^^^

| | | | ___

DEVSEL# ^^^^^^^^\______________/ ^^^^^

___ | | | ___

FRAME# \_______________/ | ^^^^\____

_ _ |_ |_ |_ |_ _ _

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

0 1 2 3 4 5 6 7

На фронте тактовой частоты 1 инициатор запускает транзакцию, вводя адрес, команду и выдавая FRAME#. Остальные сигналы находятся в режиме ожидания (обозначаются ^^^), их высокий уровень обеспечивается подтягивающими резисторами материнской платы. Возможно, это их оборотный цикл. Во втором цикле цель утверждает как DEVSEL#, так и TRDY#. Поскольку инициатор тоже готов, происходит передача данных. Это повторяется еще три цикла, но перед последним (перепад тактовой частоты 5) ведущий снимает сигнал FRAME#, указывая, что это конец. На тактовом фронте 6 шина AD и FRAME# неактивны (цикл оборота), а на других линиях управления устанавливается высокий уровень в течение 1 такта. На фронте тактовой частоты 7 другой инициатор может начать другую транзакцию. Это также цикл обработки для других линий управления.

Эквивалентный пакет чтения занимает еще один цикл, поскольку цель должна ждать 1 цикл, пока шина AD развернется, прежде чем она сможет установить TRDY#:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

___ ___ ___ ___ ___

AD[31:0] ---<___>---<___X___X___X___>---<___>

___ _______ ___ ___ ___

C/BE[3:0]# ---<___X_______X___X___X___>---<___>

___ | | | | ___

IRDY# ^^^^\___________________/ ^^^^^

___ _____ | | | | ___

TRDY# ^^^^ \______________/ ^^^^^

___ | | | | ___

DEVSEL# ^^^^\___________________/ ^^^^^

___ | | | ___

FRAME# \___________________/ | ^^^^\____

_ _ _ |_ |_ |_ |_ _ _

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

0 1 2 3 4 5 6 7 8

Высокоскоростная серия, прерванная целью, будет иметь в конце дополнительный цикл:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

___ ___ ___ ___ ___

AD[31:0] ---<___>---<___X___X___X___XXXX>----

___ _______ ___ ___ ___ ___

C/BE[3:0]# ---<___X_______X___X___X___X___>----

| | | | ___

IRDY# ^^^^^^^\_______________________/

_____ | | | | _______

TRDY# ^^^^^^^ \______________/

________________ | ___

STOP# ^^^^^^^ | | | \_______/

| | | | ___

DEVSEL# ^^^^^^^\_______________________/

___ | | | | ___

FRAME# \_______________________/ ^^^^

_ _ _ |_ |_ |_ |_ _ _

CLK _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \

0 1 2 3 4 5 6 7 8

На тактовом фронте 6 цель указывает, что она хочет остановиться (с данными), но инициатор уже удерживает IRDY# на низком уровне, поэтому существует пятая фаза данных (тактовый фронт 7), в течение которой данные не передаются.

Паритет

[ редактировать ]Шина PCI обнаруживает ошибки четности, но не пытается их исправить, повторяя операции; это просто признак неисправности. Благодаря этому нет необходимости обнаруживать ошибку четности до того, как она произойдет, и шина PCI фактически обнаруживает ее несколькими тактами позже. Во время фазы данных любое устройство, управляющее линиями AD[31:0], вычисляет четность по ним и линиям C/BE[3:0]# и отправляет это по линии PAR на один цикл позже. Все правила доступа и циклы обработки для шины AD применяются к линии PAR всего на один цикл позже. Устройство, прослушивающее шину AD, проверяет полученную четность и выдает строку PERR# (ошибка четности) через один такт после этого. Обычно это генерирует прерывание процессора, и процессор может выполнить поиск на шине PCI устройства, обнаружившего ошибку.

Строка PERR# используется только во время фаз данных, после того как цель выбрана. Если ошибка четности обнаружена во время фазы адреса (или фазы данных специального цикла), устройства, которые ее наблюдают, выставляют строку SERR# (системная ошибка).

Даже если некоторые байты замаскированы строками C/BE# и не используются, они все равно должны иметь какое-то определенное значение, и это значение должно использоваться для вычисления четности.

Быстрые обратные транзакции

[ редактировать ]Из-за необходимости цикла переключения между различными устройствами, передающими сигналы шины PCI, обычно необходимо иметь цикл простоя между транзакциями шины PCI. Однако в некоторых обстоятельствах разрешается пропустить этот цикл простоя, переходя непосредственно от последнего цикла одной передачи (IRDY# установлен, FRAME# снят) к первому циклу следующей (FRAME# установлен, IRDY# снят).

Инициатор может выполнять параллельные транзакции только в следующих случаях:

- они от одного и того же инициатора (иначе не было бы времени разворачивать строки C/BE# и FRAME#),

- первая транзакция была записью (поэтому нет необходимости поворачивать шину AD), и

- у инициатора все еще есть разрешение (от входа GNT#) на использование шины PCI.

Дополнительные временные ограничения могут возникнуть из-за необходимости развернуться вокруг целевых линий управления, особенно DEVSEL#. Цель снимает сигнал DEVSEL#, переводя его на высокий уровень, в цикле, следующем за финальной фазой данных, которая в случае последовательных транзакций является первым циклом фазы адреса. Затем второй цикл фазы адреса зарезервирован для переключения DEVSEL#, поэтому, если цель отличается от предыдущей, она не должна устанавливать DEVSEL# до третьего цикла (средняя скорость DEVSEL).

Одним из случаев, когда эта проблема не может возникнуть, является то, что инициатор каким-то образом знает (предположительно, потому что адреса имеют достаточное количество старших битов), что вторая передача адресована той же цели, что и предыдущая. В этом случае он может выполнять параллельные транзакции. Все цели PCI должны поддерживать это.

Цель также может отслеживать требования. Если он никогда не делает быстрый DEVSEL, они встречаются тривиально. Если да, то ему придется подождать до среднего времени DEVSEL, если:

- текущей транзакции предшествовал цикл простоя (не последовательный), или

- предыдущая транзакция была направлена на ту же цель, или

- текущая транзакция началась с двойного адресного цикла.

Цели, обладающие такой способностью, указывают на это специальным битом в регистре конфигурации PCI, и если она есть у всех целей на шине, все инициаторы могут свободно использовать обратную передачу.

Мост шины субтрактивного декодирования должен знать, что следует ожидать эту дополнительную задержку в случае последовательных циклов, чтобы объявить о непрерывной поддержке.

64-битный PCI

[ редактировать ]Начиная с версии 2.1, [ нужны разъяснения ] спецификация PCI включает дополнительную поддержку 64-бит. Это обеспечивается через расширенный разъем, который обеспечивает 64-битные расширения шины AD[63:32], C/BE[7:4]# и PAR64, а также ряд дополнительных контактов питания и заземления. 64-битный разъем PCI можно отличить от 32-битного разъема по дополнительному 64-битному сегменту.

Транзакции памяти между 64-битными устройствами могут использовать все 64 бита, чтобы удвоить скорость передачи данных. Транзакции, не связанные с памятью (включая доступ к конфигурации и пространству ввода-вывода), не могут использовать 64-битное расширение. Во время 64-битного пакета адресация пакета работает так же, как и при 32-битной передаче, но адрес увеличивается дважды за фазу данных. Начальный адрес должен быть выровнен по 64 битам; т.е. AD2 должен быть равен 0. Данные, соответствующие промежуточным адресам (при AD2 = 1), передаются по верхней половине шины AD.

Чтобы инициировать 64-битную транзакцию, инициатор передает начальный адрес по шине AD и выдает REQ64# одновременно с FRAME#. Если выбранная цель может поддерживать 64-битную передачу для этой транзакции, она отвечает, выдавая ACK64# одновременно с DEVSEL#. Цель может решать для каждой транзакции, разрешать ли 64-битную передачу.

Если REQ64# выставлен во время фазы адреса, инициатор также передает старшие 32 бита адреса и копию команды шины на старшей половине шины. Если для адреса требуется 64 бита, цикл двойного адреса все равно требуется, но старшая половина шины несет старшую половину адреса и последний код команды в течение обоих фазовых циклов адреса; это позволяет 64-битной цели видеть весь адрес и начинать отвечать раньше.

Если инициатор видит утверждение DEVSEL# без ACK64#, он выполняет 32-битные фазы данных. Данные, которые должны были передаваться по верхней половине шины во время первой фазы данных, вместо этого передаются во время второй фазы данных. Обычно инициатор обрабатывает все 64 бита данных до того, как увидит DEVSEL#. Если ACK64# отсутствует, он может перестать управлять верхней половиной шины данных.

Строки REQ64# и ACK64# остаются активными на протяжении всей транзакции, за исключением последней фазы данных, и снимаются одновременно с FRAME# и DEVSEL# соответственно.

Линия PAR64 работает так же, как линия PAR, но обеспечивает четность по AD[63:32] и C/BE[7:4]#. Это действительно только для фаз адреса, если установлен REQ64#. PAR64 действителен только для фаз данных, если установлены оба REQ64# и ACK64#.

Отслеживание кэша (устарело)

[ редактировать ]Первоначально PCI включал дополнительную поддержку с обратной записью согласованности кэша . Для этого требовалась поддержка целевых объектов кэшируемой памяти, которые будут прослушивать два контакта из кэша на шине: SDONE (отслеживание выполнено) и SBO# (откат отслеживания). [34]

Поскольку на практике это реализовывалось редко, оно было удалено из версии 2.2 спецификации PCI. [15] [35] и контакты повторно использовались для доступа к SMBus в версии 2.3. [17]

Кэш будет отслеживать все обращения к памяти, не выдавая DEVSEL#. Если бы он заметил доступ, который мог быть кэширован, он бы понизил уровень SDONE (отслеживание не выполнено). Цель, поддерживающая когерентность, будет избегать завершения фазы данных (утверждая TRDY#), пока не обнаружит высокий уровень SDONE.

В случае записи данных, которые были чистыми в кэше, кэш должен был бы только сделать свою копию недействительной и утвердить SDONE, как только это будет установлено. Однако, если бы в кэше содержались «грязные» данные, кэшу пришлось бы записать их обратно, прежде чем доступ мог бы продолжиться. поэтому он будет утверждать SBO# при повышении SDONE. Это будет сигнализировать активной цели о необходимости установить STOP#, а не TRDY#, в результате чего инициатор отключится и повторит операцию позже. Тем временем кэш будет арбитражировать шину и записывать данные обратно в память.

Цели, поддерживающие когерентность кэша, также должны завершать пакеты до того, как они пересекут строки кэша.

Инструменты разработки

[ редактировать ]

При разработке и/или устранении неисправностей шины PCI проверка аппаратных сигналов может быть очень важной. Логические анализаторы и анализаторы шин — это инструменты, которые собирают, анализируют и декодируют сигналы, чтобы пользователи могли просматривать их полезными способами.

См. также

[ редактировать ]- Конфигурационное пространство PCI

- Компактный PCI , PCI-X , PCI Express

- PCI-SIG , Специальная группа по интересам PCI

- PICMG , Группа производителей промышленных компьютеров PCI

- Еврокарта (печатная плата)

Ссылки

[ редактировать ]- ^ Спецификация локальной шины PCI, версия 2.2 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 18 декабря 1998 г. стр. ii.

- ^ «PCIe (Peripheral Component Interconnect Express) | На материнской плате | Сертификация Pearson IT» . www.pearsonitcertification.com . Проверено 25 сентября 2020 г.

- ^ «ПКИ» . Веб-о-педия. Сентябрь 1996 года . .

- ^ Хамахер, В. Карл; Вранешич, Звонко Г.; Заки, Сафват Г. (2002). Компьютерная организация (5-е изд.). МакГроу-Хилл. ISBN 9780071122184 .

- ^ «Видеокарта PCI Edition AMD HD 4350 от HIS» . Проверено 27 июля 2009 г.

- ^ Имдад-Хак, Фейсал (1996). Внутренняя PC-карта: CardBus и PCMCIA Design: CardBus и PCMCIA Design . Ньюнес. п. 39. ИСБН 978-0-08-053473-2 .

- ^ Сумати, С.; Сурекха, П. (2007). Передовые контрольно-измерительные системы на базе LabVIEW . Спрингер. п. 305. ИСБН 978-3-540-48501-8 .

- ^ Вариант шины PCI

- ^ Перейти обратно: а б Уильямс, Джон (2008). Проектирование цифровых СБИС с помощью Verilog: Учебник Технического института Кремниевой долины . Спрингер. п. 67. ИСБН 978-1-4020-8446-1 .

- ^ Бахмуцкий, Александр (2011). Проектирование систем телекоммуникационных шлюзов . Джон Уайли и сыновья. п. 81. ИСБН 978-1-119-95642-6 .

- ^ VLB был разработан для систем на базе 486, но даже более общий PCI должен был получить известность на этой платформе.

- ^ Мейерс, Майкл (2012). Универсальное руководство по сдаче экзамена CompTIA A+ (8-е изд.). МакГроу Хилл Профессионал. п. 339. ИСБН 978-0-07-179512-8 .

- ^ Определите различные слоты PCI , LaCie.

- ^ «Семейная история PCI» (PDF) .

- ^ Перейти обратно: а б с д и ж Спецификация локальной шины PCI, версия 3.0

- ^ «Как использовать таймер задержки PCI» . Reric.NET Эрика Сеппанена. 14 ноября 2004 г. Проверено 17 июля 2008 г.

- ^ Перейти обратно: а б с д и Спецификация локальной шины PCI, версия 2.3 . Портленд, Орегон : Специальная группа по интересам PCI . 29 марта 2002 г.

- ^ «Распиновка разъема PCI» .

- ^ Перейти обратно: а б Мощность PCI Спецификация интерфейса управления v1.2

- ^ «archive.org/zuavra.net — Использование Wake-On-LAN WOL/PME для удаленного включения вашего компьютера» . Архивировано из оригинала 8 марта 2007 года.

- ^ ZNYX Networks (16 июня 2009 г.). «Серия ZX370» . Архивировано из оригинала 2 мая 2011 года . Проверено 13 июля 2012 г.

Серия ZX370 — это настоящий 64-битный адаптер, расширяющий сетевой конвейер для достижения более высокой пропускной способности и обеспечивающий обратную совместимость со стандартными 32-битными слотами PCI.

- ^ Сети ZNYX. «Многоканальный PCI-адаптер Fast Ethernet серии ZX370» (PDF) . Архивировано из оригинала (PDF) 20 июля 2013 года . Проверено 13 июля 2012 г.

Обратная совместимость с 32-битными слотами PCI 33 МГц.

- ^ Адаптек (январь 2000 г.). «Справочник пользователя контроллера SCSI Adaptec SCSI Card 29160 Ultra160» (pdf) . п. 1 . Проверено 13 июля 2012 г.

Хотя карта Adaptec SCSI 29160 является 64-битной картой PCI, она также работает в 32-битном слоте PCI. При установке в 32-битный слот PCI карта автоматически работает в более медленном 32-битном режиме.

- ^ ЛаСи. «Поддержка LaCie: определение различных слотов PCI» . Архивировано из оригинала 4 апреля 2012 года . Проверено 13 июля 2012 г.

- ^ Спецификация локальной шины PCI, версия 3.0 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 3 февраля 2004 г. Рисунок 5-8.

- ^ Спецификация локальной шины PCI, версия 3.0 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 3 февраля 2004 г. Рисунок 5-9.

- ^ Спецификация локальной шины PCI, версия 3.0 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 3 февраля 2004 г. Рисунок 5-6.

- ^ Спецификация локальной шины PCI, версия 3.0 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 3 февраля 2004 г. Рисунок 5-7.

- ^ Micro PCI, Micro AGP (FAQ), iBASE, заархивировано из оригинала 11 декабря 2001 г. , получено 20 ноября 2010 г.

- ^ Рудье, Жерар (28 ноября 2001 г.). «Re: sym53c875: чтение /proc вызывает ошибку четности SCSI» . linux-kernel (список рассылки).

- ^ Перейти обратно: а б Спецификация локальной шины PCI: версия 2.1 и версия 2.0 (PDF) (примечания по применению). Корпорация Интел. Март 1997 г. АП-753. Архивировано из оригинала (PDF) 30 апреля 2015 г.

- ^ «Особенности шины — написание драйверов устройств для Oracle® Solaris 11.3» . docs.oracle.com . Проверено 18 декабря 2020 г.

- ^ Спецификация архитектуры моста PCI-to-PCI, версия 1.1

- ^ Спецификация локальной шины PCI, версия 2.1

- ^ Спецификация локальной шины PCI, версия 2.2 . Хиллсборо, Орегон : Специальная группа по интересам PCI . 18 декабря 1998 года.

Дальнейшее чтение

[ редактировать ]- Официальные технические характеристики

- Спецификация локальной шины PCI: версия 2.3 . PCI-SIG. 29 марта 2002 г. (1000 долларов США для нечленов или 50 долларов США для членов. Членство в PCI-SIG стоит 3000 долларов США в год.)

- Спецификация локальной шины PCI: версия 3.0 . PCI-SIG. 12 августа 2002 г. (1000 долларов США для нечленов или 50 долларов США для членов. Членство в PCI-SIG стоит 3000 долларов США в год.)

- Книги

- Эбботт, Дуг (2004). Демистификация шины PCI (2-е изд.). Эльзевир Наука. ISBN 978-0-7506-7739-4 . 250 страниц.

- Шенли, Том (1999). Системная архитектура PCI (4-е изд.). Аддисон-Уэсли Профессионал. ISBN 978-0-201-30974-4 . 832 страницы.

- Шенли, Том (2000). Системная архитектура PCI-X (1-е изд.). Аддисон-Уэсли. ISBN 978-0-201-72682-4 . 752 страницы.

- Солари, Эд (2001). Архитектура и проектирование аппаратного и программного обеспечения PCI и PCI-X (5-е изд.). Аннабуки. ISBN 978-0-929392-63-9 . 1140 страниц.

- Гудрам, Алан (1998). Применение и проектирование PCI HotPlug (1-е изд.). Аннабуки. ISBN 978-0-929392-60-8 . 162 страницы.

Внешние ссылки

[ редактировать ]- Официальный

- Официальный сайт Специальной группы по интересам PCI (PCI-SIG)

- Технические детали

- Введение в протокол PCI. Архивировано 19 января 2013 г. на Wayback Machine , electrofriends.com.

- Распиновка и сигналы шины PCI , pinouts.ru

- Размеры PCI-карты , Interfacebus.com

- Списки поставщиков, устройств, идентификаторов

- Списки поставщиков и устройств PCI , pcidatabase.com

- PCI ID Repository — проект по сбору всех известных идентификаторов

- Советы

- Краткий обзор требований к питанию и совместимости PCI с красивой диаграммой

- Хорошие диаграммы и текст о том, как распознать разницу между разъемами на 5 В и 3,3 В.

- Линукс

- Инструменты разработки

- Активный расширитель шины PCI , dinigroup.com

- Ядра ПЛИС

- Ядро интерфейса PCI , полупроводниковая решетка

- PCI Bridge Core , OpenCore .

- IP-поиск ядер шины PCI , Беркли .