АРМ Кортекс-М

с тактовой частотой 24 МГц, ARM Cortex-M3 Микроконтроллер 16 КБ флэш-памятью , оперативной памятью 4 КБ. Производитель STMicroelectronics .

ARM Cortex-M — это группа 32-битных процессорных ядер RISC ARM, лицензированных ARM Limited . Эти ядра оптимизированы для недорогих и энергоэффективных интегральных схем, которые встроены в десятки миллиардов потребительских устройств. [1] Хотя чаще всего они являются основным компонентом микросхем микроконтроллеров , иногда они встраиваются и в другие типы микросхем. Семейство Cortex-M состоит из Cortex-M0, [2] Кортекс-М0+, [3] Кортекс-М1, [4] Кортекс-М3, [5] Кортекс-М4, [6] Кортекс-М7, [7] Кортекс-М23, [8] Кортекс-М33, [9] Кортекс-М35П, [10] Кортекс-М52, [11] Кортекс-М55, [12] Кортекс-М85. [13] Опция модуля с плавающей запятой (FPU) доступна для ядер Cortex-M4/M7/M33/M35P/M52/M55/M85, и когда они включены в состав кремния, эти ядра иногда называют «Cortex-MxF», где 'x ' - это основной вариант.

Обзор

[ редактировать ]| 32-битный | |

|---|---|

| Год | Основной |

| 2004 | Кортекс-М3 |

| 2007 | Кортекс-М1 |

| 2009 | Кортекс-М0 |

| 2010 | Кортекс-М4 |

| 2012 | Кортекс-М0+ |

| 2014 | Кортекс-М7 |

| 2016 | Кортекс-М23 |

| 2016 | Кортекс-М33 |

| 2018 | Кортекс-М35П |

| 2020 | Кортекс-М55 |

| 2022 | Кортекс-М85 |

| 2023 | Кортекс-М52 |

Семейство ARM Cortex-M — это ядра микропроцессоров ARM, предназначенные для использования в микроконтроллерах , ASIC , ASSP , FPGA и SoC . Ядра Cortex-M обычно используются в качестве выделенных микросхем микроконтроллеров, но также «спрятаны» внутри чипов SoC в качестве контроллеров управления питанием, контроллеров ввода-вывода, системных контроллеров, контроллеров сенсорного экрана, контроллеров интеллектуальных батарей и контроллеров датчиков.

Основное отличие от ядер Cortex-A заключается в том, что ядра Cortex-M не имеют модуля управления памятью (MMU) для виртуальной памяти , который считается необходимым для «полноценных» операционных систем . Вместо этого программы Cortex-M работают на «голом железе» или в одной из многих операционных систем реального времени , которые поддерживают Cortex-M .

Хотя в прошлом 8-битные микроконтроллеры были очень популярны, Cortex-M постепенно отвоевывает рынок 8-битных процессоров, поскольку цены на младшие чипы Cortex-M снижаются. Cortex-M стали популярной заменой 8-битных чипов в приложениях, использующих 32-битные математические операции, и заменили старые устаревшие ядра ARM, такие как ARM7 и ARM9 .

Лицензия

[ редактировать ]ARM Limited не производит и не продает процессорные устройства на основе собственных разработок, а лицензирует архитектуру процессора заинтересованным сторонам. Arm предлагает различные условия лицензирования, различающиеся по стоимости и результатам. Всем лицензиатам Arm предоставляет интегрируемое аппаратное описание ядра ARM, а также полный набор инструментов для разработки программного обеспечения и право продавать готовые микросхемы, содержащие процессор ARM.

Настройка кремния

[ редактировать ]процессора ARM Производители интегрированных устройств (IDM) получают IP-адрес как синтезируемый RTL (записанный на Verilog ). В этой форме они имеют возможность выполнять оптимизацию и расширение на архитектурном уровне. Это позволяет производителю достигать индивидуальных целей проектирования, таких как более высокая тактовая частота, очень низкое энергопотребление, расширения набора команд (включая операции с плавающей запятой), оптимизация размера, поддержка отладки и т. д. Чтобы определить, какие компоненты были включены в конкретный ARM Чип ЦП, обратитесь к техническому описанию производителя и соответствующей документации.

Вот некоторые варианты кремния для ядер Cortex-M:

- Таймер SysTick: 24-битный системный таймер, расширяющий функциональные возможности как процессора, так и вложенного векторного контроллера прерываний (NVIC). Если он присутствует, он также обеспечивает дополнительное прерывание SysTick с настраиваемым приоритетом. [14] [15] [16] Хотя таймер SysTick не является обязательным для M0/M0+/M1/M23, микроконтроллер Cortex-M без него встречается крайне редко. Если микроконтроллер Cortex-M33/M35P/M52/M55/M85 имеет опцию расширения безопасности, то он опционально может иметь два SysTicks (один защищенный, один незащищенный).

- Бит-диапазон: отображает полное слово памяти на один бит в области бит-диапазона. Например, запись в слово-псевдоним установит или очистит соответствующий бит в области битового диапазона. Это позволяет напрямую получить доступ к каждому отдельному биту в битовой области по адресу, выровненному по слову. В частности, отдельные биты могут быть установлены, очищены или переключены из C/C++ без выполнения последовательности инструкций чтения-изменения-записи. [14] [15] [16] Хотя битовый диапазон не является обязательным, микроконтроллеры Cortex-M3 и Cortex-M4 без него встречаются реже. Некоторые микроконтроллеры Cortex-M0 и Cortex-M0+ имеют битовый диапазон.

- Блок защиты памяти (MPU): обеспечивает поддержку защиты областей памяти посредством соблюдения правил привилегий и доступа. Он поддерживает до шестнадцати различных регионов, каждый из которых можно разделить на субрегионы одинакового размера. [14] [15] [16]

- Плотно связанная память (TCM): с низкой задержкой ( состояние нулевого ожидания ) SRAM , которую можно использовать для хранения стека вызовов , структур управления RTOS, структур данных прерываний, кода обработчика прерываний и кода, критического по скорости. Помимо кэша ЦП , TCM является самой быстрой памятью в микроконтроллере ARM Cortex-M. Поскольку TCM не кэшируется и не доступен с той же скоростью, что и процессор и кеш, его концептуально можно описать как «адресуемый кеш». Существуют ITCM (TCM инструкций) и DTCM (TCM данных), позволяющие процессору гарвардской архитектуры считывать данные из обоих одновременно. DTCM не может содержать никаких инструкций, но ITCM может содержать данные. Поскольку TCM тесно связан с ядром процессора, механизмы DMA могут не иметь доступа к TCM в некоторых реализациях.

| ARM-ядро | Кора головного мозга М0 [17] |

Кора головного мозга М0+ [18] |

Кора головного мозга М1 [19] |

Кора головного мозга M3 [20] |

Кора головного мозга М4 [21] |

Кора головного мозга М7 [22] |

Кора головного мозга М23 [23] |

Кора головного мозга М33 [24] |

Кора головного мозга М35П [10] |

Кора головного мозга М52 [25] |

Кора головного мозга М55 [26] |

Кора головного мозга М85 [27] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 24-битный таймер SysTick | Необязательный (0,1) |

Необязательный (0, 1) |

Необязательный (0,1) |

Да (1) |

Да (1) |

Да (1) |

Необязательный (0, 1, 2) |

Да (1, 2) |

Да (1, 2) |

Да (1, 2) |

Да (1, 2) |

Да (1, 2) |

| Однотактный порт ввода-вывода | Нет | Необязательный | Нет | Нет | Нет | Нет | Необязательный | Нет | Нет | Нет | Нет | Нет |

| Бит-диапазонная память | Нет [28] | Нет [28] | Нет* | Необязательный | Необязательный | Необязательный | Нет | Нет | Нет | Нет | Нет | Нет |

| Защита памяти Блок ( МПУ ) |

Нет | Необязательный (0, 8) |

Нет | Необязательный (0,8) |

Необязательный (0, 8) |

Необязательный (0, 8, 16) |

Необязательный (0, 4, 8, 12, 16) |

Необязательный (0, 4, 8, 12, 16) |

Необязательный (до 16)* |

Необязательный (0, 4, 8, 12, 16) |

Необязательный (0, 4, 8, 12, 16) |

Необязательный (0, 4, 8, 12, 16) |

| безопасности Атрибуция Юнайтед (Орегон) и Пределы стека |

Нет | Нет | Нет | Нет | Нет | Нет | Необязательный (0, 4, 8) |

Необязательный (0, 4, 8) |

Необязательный (до 8)* |

Необязательный (0, 4, 8) |

Необязательный (0, 4, 8) |

Необязательный (0, 4, 8) |

| Кэш инструкций | Нет [29] | Нет [29] | Нет [29] | Нет [29] | Нет [29] | Необязательный (до 64 КБ) |

Нет | Нет | Необязательный (до 16 КБ) |

Необязательный (до 64 КБ) |

Необязательный (до 64 КБ) |

Необязательный (до 64 КБ) |

| Кэш данных | Нет [29] | Нет [29] | Нет [29] | Нет [29] | Нет [29] | Необязательный (до 64 КБ) |

Нет | Нет | Нет | Необязательный (до 64 КБ) |

Необязательный (до 64 КБ) |

Необязательный (до 64 КБ) |

| Инструкция ТСМ (ITCM) Память |

Нет | Нет | Необязательный (до 1 МБ) |

Нет | Нет | Необязательный (до 16 МБ) |

Нет | Нет | Нет | Необязательный (до 16 МБ) |

Необязательный (до 16 МБ) |

Необязательный (до 16 МБ) |

| Данные ТКМ (DTCM) Память |

Нет | Нет | Необязательный (до 1 МБ) |

Нет | Нет | Необязательный (до 16 МБ) |

Нет | Нет | Нет | Необязательный (до 16 МБ) |

Необязательный (до 16 МБ) |

Необязательный (до 16 МБ) |

| ECC для TCM и кэш |

Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный | Необязательный |

| векторной таблицы Смещение Зарегистрироваться (ВТОР) |

Нет | Необязательный (0,1) |

Необязательный (0,1) |

Необязательный (0,1) |

Необязательный (0,1) |

Необязательный (0,1) |

Необязательный (0,1,2) |

Да (1,2) |

Да (1,2) |

Да (1,2) |

Да (1,2) |

Да (1,2) |

- Примечание. Большинство чипов Cortex-M3 и M4 имеют битовый диапазон и MPU. Опцию битового диапазона можно добавить к M0/M0+ с помощью комплекта проектирования системы Cortex-M. [28]

- Примечание. Программное обеспечение должно проверять наличие каждой функции, прежде чем пытаться ее использовать. [16]

- Примечание. О Cortex-M35P доступна ограниченная общедоступная информация до тех пор, пока не его техническое справочное руководство . будет выпущено

Дополнительные опции кремния: [14] [15]

- Порядок данных: прямой или обратный порядок байтов. В отличие от устаревших ядер ARM, Cortex-M является одним из этих вариантов, постоянно закрепленным в кремнии.

- Прерывания: от 1 до 32 (M0/M0+/M1), от 1 до 240 (M3/M4/M7/M23), от 1 до 480 (M33/M35P/M52/M55/M85).

- Контроллер прерываний пробуждения: опционально.

- Регистр смещения таблицы векторов: опционально. (недоступно для M0).

- Ширина выборки инструкций: только 16-битная или преимущественно 32-битная.

- Поддержка пользователей/привилегий: необязательно.

- Сбросить все регистры: Необязательно.

- Однотактный порт ввода-вывода: опционально. (М0+/М23).

- Порт доступа к отладке (DAP): нет, SWD , JTAG и SWD. (опционально для всех ядер Cortex-M)

- Прекращение поддержки отладки: необязательно.

- Количество компараторов точек наблюдения: от 0 до 2 (M0/M0+/M1), от 0 до 4 (M3/M4/M7/M23/M33/M35P/M52/M55/M85).

- Количество компараторов точек останова: от 0 до 4 (M0/M0+/M1/M23), от 0 до 8 (M3/M4/M7/M33/M35P/M52/M55/M85).

Наборы инструкций

[ редактировать ]Cortex-M0/M0+/M1 реализует архитектуру ARMv6-M , [14] Cortex-M3 реализует архитектуру ARMv7-M , [15] Cortex-M4/Cortex-M7 реализует архитектуру ARMv7E-M , [15] Cortex-M23/M33/M35P реализуют архитектуру ARMv8-M , [30] а Cortex-M52/M55/M85 реализует архитектуру ARMv8.1-M . [30] Архитектуры совместимы с двоичными инструкциями снизу вверх от ARMv6-M до ARMv7-M и до ARMv7E-M. Двоичные инструкции, доступные для Cortex-M0/Cortex-M0+/Cortex-M1, могут выполняться без изменений на Cortex-M3/Cortex-M4/Cortex-M7. Двоичные инструкции, доступные для Cortex-M3, могут выполняться без изменений на Cortex-M4/Cortex-M7/Cortex-M33/Cortex-M35P. [14] [15] В архитектурах Cortex-M поддерживаются только наборы инструкций Thumb-1 и Thumb-2; устаревший набор 32-битных инструкций ARM не поддерживается.

Все ядра Cortex-M реализуют общий поднабор инструкций, который состоит из большей части Thumb-1, некоторых Thumb-2, включая умножение 32-битного результата. Cortex-M0/Cortex-M0+/Cortex-M1/Cortex-M23 были разработаны для создания самой маленькой кремниевой матрицы, имеющей наименьшее количество инструкций семейства Cortex-M.

Cortex-M0/M0+/M1 включает инструкции Thumb-1, за исключением новых инструкций (CBZ, CBNZ, IT), которые были добавлены в архитектуре ARMv7-M. Cortex-M0/M0+/M1 включает в себя небольшое подмножество инструкций Thumb-2 (BL, DMB, DSB, ISB, MRS, MSR). [14] Cortex-M3/M4/M7/M33/M35P имеют все базовые инструкции Thumb-1 и Thumb-2. Cortex-M3 добавляет три инструкции Thumb-1, все инструкции Thumb-2, аппаратное целочисленное деление и инструкции по арифметике насыщения . Cortex-M4 добавляет инструкции DSP одинарной точности и дополнительный модуль с плавающей запятой (VFPv4-SP). Cortex-M7 добавляет дополнительный FPU двойной точности (VFPv5). [22] [15] Cortex-M23/M33/M35P/M52/M55/M85 добавляет инструкции TrustZone .

| Ядро руки | Кора головного мозга М0 [17] |

Кора головного мозга М0+ [18] |

Кора головного мозга М1 [19] |

Кора головного мозга M3 [20] |

Кора головного мозга М4 [21] |

Кора головного мозга М7 [22] |

Кора головного мозга М23 [23] |

Кора головного мозга М33 [24] |

Кора головного мозга М35П |

Кора головного мозга М52 [25] |

Кора головного мозга М55 [26] |

Кора головного мозга М85 [27] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ARM-архитектура | АРМв6-М [14] |

АРМв6-М [14] |

АРМв6-М [14] |

АРМв7-М [15] |

ARMv7E-M [15] |

ARMv7E-M [15] |

АРМв8-М Базовый уровень [30] |

АРМв8-М Основная линия [30] |

АРМв8-М Основная линия [30] |

Армв8.1-М Основная линия [30] |

Армв8.1-М Основная линия [30] |

Армв8.1-М Основная линия [30] |

| Компьютерная архитектура | От Нойманн |

От Нойманн |

От Нойманн |

Гарвард | Гарвард | Гарвард | От Нойманн |

Гарвард | Гарвард | Гарвард | Гарвард | Гарвард |

| Конвейер инструкций | 3 этапа | 2 этапа | 3 этапа | 3 этапа | 3 этапа | 6 этапов | 2 этапа | 3 этапа | 3 этапа | 4 этапа | 4-5 этапов | 7 этапов |

| Задержка прерывания (нулевая память состояния ожидания ) |

16 циклов | 15 циклов | 23 для НМИ, 26 для прерывания |

12 циклов | 12 циклов | 12 циклов, 14 худших случай |

15 циклов, 24 безопасных к NS IRQ |

12 циклов, 21 безопасный к NS IRQ |

подлежит уточнению | подлежит уточнению | подлежит уточнению | подлежит уточнению |

| для большого пальца 1 Инструкции | Большинство | Большинство | Большинство | Весь | Весь | Весь | Большинство | Весь | Весь | Весь | Весь | Весь |

| для большого пальца-2 Инструкции | Некоторый | Некоторый | Некоторый | Весь | Весь | Весь | Некоторый | Весь | Весь | Весь | Весь | Весь |

| Умножение инструкций 32×32 = 32-битный результат |

Да | Да | Да | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Умножение инструкций 32×32 = 64-битный результат |

Нет | Нет | Нет | Да | Да | Да | Нет | Да | Да | Да | Да | Да |

| Разделить инструкции 32/32 = 32-битное частное |

Нет | Нет | Нет | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Насыщенные математические инструкции | Нет | Нет | Нет | Некоторый | Да | Да | Нет | Да | Да | Да | Да | Да |

| DSP Инструкции | Нет | Нет | Нет | Нет | Да | Да | Нет | Необязательный | Необязательный | Да | Да | Да |

| Полуточность (HP) с плавающей запятой инструкции |

Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный |

| Одинарная точность (SP) инструкции с плавающей запятой |

Нет | Нет | Нет | Нет | Необязательный | Необязательный | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный |

| Двойная точность (DP) инструкции с плавающей запятой |

Нет | Нет | Нет | Нет | Нет | Необязательный | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный |

| Гелиевые векторные инструкции | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный |

| TrustZone Инструкции по безопасности | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный | Да |

| сопроцессора Инструкции | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный |

| Пользовательские инструкции ARM (ACI) | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Нет | Необязательный | Необязательный | Необязательный |

| Аутентификация указателя и цель ветвления Инструкции по идентификации (PACBTI) |

Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Нет | Необязательный |

- Примечание. Подсчет циклов задержки прерывания предполагает: 1) стек находится в ОЗУ с нулевым ожиданием, 2) другая функция прерывания, которая в данный момент не выполняется, 3) опция расширения безопасности не существует, поскольку она добавляет дополнительные циклы. Ядра Cortex-M с компьютерной архитектурой Гарварда имеют меньшую задержку прерывания, чем ядра Cortex-M с компьютерной архитектурой фон Неймана.

- Примечание. Серия Cortex-M включает три новые 16-битные инструкции Thumb-1 для спящего режима: SEV, WFE, WFI.

- Примечание. Cortex-M0/M0+/M1 не содержит 16-битных инструкций Thumb-1 : CBZ, CBNZ, IT. [14] [15]

- Примечание. Cortex-M0/M0+/M1 включает только следующие 32-битные инструкции Thumb-2 : BL, DMB, DSB, ISB, MRS, MSR. [14] [15]

- Примечание. Cortex-M0/M0+/M1/M23 имеет только 32-битные инструкции умножения с младшим 32-битным результатом (32 бит × 32 бита = младшие 32 бита), тогда как Cortex-M3/M4/M7/ M33/M35P включает дополнительные 32-битные инструкции умножения с 64-битными результатами (32 бит × 32 бит = 64 бита). Cortex-M4/M7 (опционально M33/M35P) включает инструкции DSP для (16 бит × 16 бит = 32 бита), (32 бит × 16 бит = верхние 32 бита), (32 бит × 32 бит = верхние 32 бита) умножения. [14] [15]

- Примечание. Количество циклов выполнения команд умножения и деления различается в зависимости от конструкции ядра ARM Cortex-M. Некоторые ядра имеют кремниевую опцию для выбора высокой скорости или небольшого размера (медленной скорости), поэтому ядра имеют возможность использовать меньшее количество кремния с недостатком более высокого количества циклов. Прерывание, возникающее во время выполнения инструкции деления или медленно итеративной инструкции умножения, заставит процессор отказаться от выполнения инструкции, а затем перезапустить ее после возврата прерывания.

- Инструкции умножения «32-битный результат» — Cortex-M0/M0+/M23 — вариант кремния с 1 или 32 тактами, Cortex-M1 — вариант кремния с 3 или 33 тактами, Cortex-M3/M4/M7/M33/M35P — 1 такт.

- Инструкции умножения «64-битный результат» — Cortex-M3 — 3–5 тактов (в зависимости от значений), Cortex-M4/M7/M33/M35P — 1 такт.

- Инструкции разделения — Cortex-M3/M4 — 2–12 тактов (в зависимости от значений), Cortex-M7 — 3–20 тактов (в зависимости от значений), Cortex-M23 — 17 или 34 такта, Cortex-M33 — 2–11 циклов (в зависимости от значений), Cortex-M35P подлежит уточнению.

- Примечание. Некоторые ядра Cortex-M имеют варианты кремния для различных типов блоков с плавающей запятой ( FPU ). Cortex-M55/M85 имеет опцию половинной точности ( HP ), Cortex-M4/M7/M33/M35P/M52/M55/M85 имеет опцию одинарной точности ( SP ), Cortex-M7/M52 /M55/M85 имеет опцию двойной точности ( DP ). Когда включен FPU, ядро иногда называют «Cortex-MxF», где «x» — это вариант ядра, например Cortex- F. M4 [14] [15]

| Группа | Инстр биты |

Инструкции | Кора головного мозга М0, М0+, М1 |

Кора головного мозга M3 |

Кора головного мозга М4 |

Кора головного мозга М7 |

Кора головного мозга М23 |

Кора головного мозга М33 |

Кора головного мозга М35П |

Кора головного мозга М52 |

Кора головного мозга М55 |

Кора головного мозга М85 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Большой палец-1 | 16 | ADC, ADD, ADR, AND, ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSB, LDRSH, LSL, LSR, MOV, MUL, MVN, NOP, ORR, POP, PUSH, REV, REV16, REVSH, ROR, RSB, SBC, SEV, STM, STR, STRB, STRH, SUB, SVC, SXTB, SXTH, TST, UXTB, UXTH, WFE, WFI, YIELD | Да | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Большой палец-1 | 16 | КБНЗ, КБЗ | Нет | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Большой палец-1 | 16 | ЭТО | Нет | Да | Да | Да | Нет | Да | Да | Да | Да | Да |

| Большой палец-2 | 32 | БЛ, ДМБ, ДСБ, ИСБ, МРС, МСР | Да | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Большой палец-2 | 32 | SDIV, UDIV, MOVT, MOVW, BW, LDREX, LDREXB, LDREXH, STREX, STREXB, STREXH | Нет | Да | Да | Да | Да | Да | Да | Да | Да | Да |

| Большой палец-2 | 32 | ADC, ADD, ADR, AND, ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ , CMN, CMP, DBG, EOR, LDC, LDM, LDR, LDRB, LDRBT, LDRD, LDRH, LDRHT, LDRSB, LDRSBT, LDRSH, LDRSHT, LDRT, LSL, LSR, MCR, MCRR, MLA, MLS, MRC, MRRC, MUL, MVN, NOP, ORN, ORR, PLD, PLDW, PLI, POP, PUSH, RBIT, REV, REV16, REVSH, ROR, RRX, RSB, SBC, SBFX, SEV, SMLAL, SMULL, SSAT, STC, STM, STR, STRB, STRBT, STRD, STRH, STRHT, STRT, SUB, SXTB, SXTH, TBB, TBH, TEQ, TST, UBFX, UMLAL, UMULL, USAT, UXTB, UXTH, WFE, WFI, ДОХОДНОСТЬ | Нет | Да | Да | Да | Нет | Да | Да | Да | Да | Да |

| ЦСП | 32 | PKH, OLD, ODD16, ODD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB16, QSUB8, SADD16, SADD8, SASX, SEL, SHADD16, SHADD8, SHASX, SHSAX, SHSUB16, SHSUB8, SMLABB, SMLABT, SMLATB, SMLATT, SMLAD, SMLALBB, SMLALBT, SMLALTB, SMLALTT, SMLALD, SMLAWB, SMLAWT, SMLSD, SMLSLD, SMMLA, SMMLS, SMMUL, SMUAD, SMULBB, SMULBT, SMULTT, SMULTB, SMULWT, SMULWB, SMUSD, SSAT16, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHADD8, UHASX, UHSAX, UHSUB16, UHSUB8, UMAAL, UQADD16, UQADD8, UQASX, UQSAX, UQSUB16, UQSUB8, USAD8, USAD8, USAT16, УСУБ16. USUB8, UXTAB, UXTAB16, UXTAH, UXTB16 | Нет | Нет | Да | Да | Нет | Необязательный | Необязательный | Да | Да | Да |

| SP Плавающий | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMSR, VMUL, VNEG, VNMLA, VNMLS, VNMUL, VPOP, VPUSH, VSQRT, VSTM, VSTR, VSUB | Нет | Нет | Необязательный | Необязательный | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный |

| ДП с плавающей запятой | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | Нет | Нет | Нет | Необязательный | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный |

| Приобретение/Выпуск | 32 | LDA, LDAB, LDAH, LDAEX, LDAEXB, LDAEXH, STL, STLB, STLH, STLEX, STLEXB, STLEXH | Нет | Нет | Нет | Нет | Да | Да | Да | Да | Да | Да |

| TrustZone | 16 | БЛКСНС, БКСНС | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный | Да |

| 32 | СГ, ТТ, ТТТ, ТТА, ТТАТ | |||||||||||

| Сопроцессор | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRRC, MRRC2 | Нет | Нет | Нет | Нет | Нет | Необязательный | Необязательный | Необязательный | Необязательный | Необязательный |

| МСА | 32 | CX1, CX1A, CX2, CX2A, CX3, CX3A, CX1D, CX1DA, CX2D, CX2DA, CX3D, CX3DA, VCX1, VCX1A, VCX2, VCX2A, VCX3, VCX3A | Нет | Нет | Нет | Нет | Нет | Необязательный | Нет | Необязательный | Необязательный | Необязательный |

| ПАКБТИ | 32 | АУТ, АУТГ, БТИ, БХАУТ, ПАК, ПАКБТИ, ПАКГ | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Необязательный | Нет | Необязательный |

- Примечание. MOVW — это псевдоним, обозначающий 32-битную «широкую» инструкцию MOV.

- Примечание. BW — это безусловная ветвь на большие расстояния (по кодировке, работе и диапазону аналогична BL, за вычетом установки регистра LR).

- Примечание. Для Cortex-M1 существуют инструкции WFE/WFI/SEV, но они выполняются как инструкция NOP.

- Примечание. Инструкции FPU половинной точности (HP) действительны в Cortex-M52/M55/M85 только в том случае, если опция HP FPU существует в кристалле.

- Примечание. Инструкции FPU одинарной точности (SP) действительны в Cortex-M4 / M7 / M33 / M35P / M52 / M55 / M85 только в том случае, если опция SP FPU существует в кристалле.

- Примечание. Инструкции FPU двойной точности (DP) действительны в Cortex-M7 / M52 / M55 / M85 только тогда, когда опция DP FPU существует в кристалле.

Устаревания

[ редактировать ]В архитектуре ARM для серии ARM Cortex-M удалены некоторые функции старых устаревших ядер: [14] [15]

- 32-битный набор инструкций ARM не включен в ядра Cortex-M.

- Порядок байтов выбирается при реализации кремния в ядрах Cortex-M. данных «на лету» Устаревшие ядра позволяли менять порядок байтов .

- Сопроцессоры не поддерживались ядрами Cortex-M до тех пор, пока опция кремния не была повторно введена в «ARMv8-M Mainline» для ядер ARM Cortex-M33/M35P.

Возможности 32-битного набора инструкций ARM во многом дублируются наборами инструкций Thumb-1 и Thumb-2, но некоторые функции ARM не имеют аналогичной функции:

- Инструкции ARM SWP и SWPB (обмен) не имеют аналогичной функции в Cortex-M.

16-битный набор команд Thumb-1 со временем развивался с тех пор, как он был впервые выпущен в устаревших ядрах ARM7T с архитектурой ARMv4T. Новые инструкции Thumb-1 добавлялись по мере выпуска каждой устаревшей архитектуры ARMv5/ARMv6/ARMv6T2. Некоторые 16-битные инструкции Thumb-1 были удалены из ядер Cortex-M:

- Инструкция «BLX <immediate>» не существует, поскольку она использовалась для переключения с Thumb-1 на набор инструкций ARM. Инструкция «BLX <регистр>» по-прежнему доступна в Cortex-M.

- SETEND не существует, поскольку переключение режима байтов данных на лету больше не поддерживается.

- Инструкции сопроцессора не поддерживались на ядрах Cortex-M до тех пор, пока опция кремния не была повторно введена в «ARMv8-M Mainline» для ядер ARM Cortex-M33/M35P.

- Инструкция SWI была переименована в SVC, хотя двоичное кодирование инструкций осталось прежним. Однако код обработчика SVC отличается от кода обработчика SWI из-за изменений в моделях исключений.

Кортекс-М0

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Набор инструкций | ARMv6-M ( Thumb-1 (большинство), Большой палец-2 (некоторые)) |

Ядро Cortex-M0 оптимизировано для кремниевых кристаллов небольшого размера и используется в самых дешевых чипах. [2]

Ключевые особенности ядра Cortex-M0: [17]

- Архитектура ARMv6-M [14]

- 3-ступенчатый трубопровод

- Наборы инструкций:

- Большой палец-1 (большинство), отсутствует CBZ, CBNZ, IT

- Thumb-2 (некоторые), только BL, DMB, DSB, ISB, MRS, MSR

- Умножение 32-битного аппаратного целого числа с 32-битным результатом

- От 1 до 32 прерываний плюс NMI

Варианты кремния:

- Скорость аппаратного целочисленного умножения: 1 или 32 цикла.

Чипсы

[ редактировать ]

На ядре Cortex-M0 созданы следующие микроконтроллеры:

- АБОВ AC30M1x64

- Кипарис PSoC 4000, 4100, 4100M, 4200, 4200DS, 4200L, 4200M

- Infineon XMC1100 , XMC1200, XMC1300, XMC1400, TLE984x

- Диалог DA1458x, DA1468x

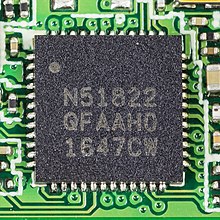

- Северный nRF51

- НСП ЛПК1100 , ЛПК1200

- Нувотон НуМикро

- Соникс SN32F700

- СТ STM32 F0

- Тошиба ТХ00

- Vorago VA10800 (экстремальные температуры), VA10820 (радиационно-стойкие)

Следующие чипы имеют Cortex-M0 в качестве вторичного ядра:

- NXP LPC4300 (один Cortex-M4F + один Cortex-M0)

- компании Texas Instruments (один программируемый Cortex-M3 + один сетевой процессор Cortex-M0 + один фирменный датчик Sensor Controller Engine) Беспроводные микроконтроллеры SimpleLink CC1310 и CC2650

Кортекс-М0+

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | АРМв6-М |

| Набор инструкций | Большой палец-1 (большинство) , Большой палец-2 (некоторые) |

Cortex-M0+ — это оптимизированная версия Cortex-M0. Cortex-M0+ имеет полную совместимость набора команд с Cortex-M0, что позволяет использовать тот же компилятор и инструменты отладки. Конвейер Cortex-M0+ был сокращен с 3 до 2 этапов, что снижает энергопотребление и увеличивает производительность (более высокий средний IPC из-за того, что ветвления занимают на один цикл меньше). В дополнение к функциям отладки в существующем Cortex-M0, к Cortex-M0+ может быть добавлена опция Micro Trace Buffer (MTB), которая обеспечивает простой буфер трассировки инструкций. Cortex-M0+ также получил функции Cortex-M3 и Cortex-M4, которые можно добавить в качестве кремниевых опций, такие как блок защиты памяти (MPU) и перемещение таблицы векторов. [18]

Ключевые особенности ядра Cortex-M0+: [18]

- Архитектура ARMv6-M [14]

- 2-ступенчатый конвейер (на один меньше, чем Cortex-M0)

- Наборы инструкций: (такие же, как Cortex-M0)

- Большой палец-1 (большинство), отсутствует CBZ, CBNZ, IT

- Thumb-2 (некоторые), только BL, DMB, DSB, ISB, MRS, MSR

- Умножение 32-битного аппаратного целого числа с 32-битным результатом

- От 1 до 32 прерываний плюс NMI

Варианты кремния:

- Скорость аппаратного целочисленного умножения: 1 или 32 цикла

- 8-регионный блок защиты памяти (MPU) (то же, что M3 и M4)

- Перемещение таблицы векторов (так же, как M3, M4)

- Однотактный порт ввода-вывода (доступен в M0+/M23)

- Микробуфер трассировки (MTB) (доступен в M0+/M23/M33/M35P)

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M0+:

- ABOV Semiconductor A31G11x, A31G12x, A31G314

- Cypress PSoC 4000S, 4100S, 4100S+, 4100PS, 4700S, FM0+

- Эпсон С1К31В74, С1К31Д01, С1К31Д50

- Холтек HT32F52000

- Микросхема SAM C2, D0, D1, D2, DA, L2, R2, R3; и PIC32CM JH и MC [31]

- НСП ЛПК800 , ЛПК11Э60, ЛПК11У60

- NXP ( Freescale ) Kinetis E, EA, L, M, V1, W0, S32K11x

- Raspberry Pi RP2040 (два ядра M0+)

- Ренесас С124, С128, РЭ, РЭ01

- Silicon Labs ( Energy Micro ) EFM32 Zero, счастливо

- ST STM32 L0 , G0 , C0 , WL (один Cortex-M4 + один Cortex-M0+)

Следующие чипы имеют Cortex-M0+ в качестве вторичного ядра:

Самые маленькие микроконтроллеры ARM относятся к типу Cortex-M0 + (по состоянию на 2014 год самым маленьким размером 1,6 на 2 мм в корпусе размером с чип является Kinetis KL03). [32]

21 июня 2018 года университета Мичиганского исследователи по симпозиуме на 2018 года СБИС Технология и Схемы с бумагой "А 0,04мм" 3 Беспроводная безбатарейная сенсорная система мощностью 16 нВт со встроенным процессором Cortex-M0+ и оптической связью для измерения температуры в клетках». Устройство составляет одну десятую размера компьютера IBM, ранее заявленного мировым рекордом по размеру, установленного несколько месяцев назад в марте 2018 года, что меньше, чем крупинка соли.

Кортекс-М1

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | АРМв6-М |

| Набор инструкций | Большой палец-1 (большинство) , Большой палец-2 (некоторые) |

Cortex-M1 — это оптимизированное ядро, специально разработанное для загрузки в чипы FPGA . [4]

Ключевые особенности ядра Cortex-M1: [19]

- Архитектура ARMv6-M [14]

- 3-ступенчатый трубопровод .

- Наборы инструкций:

- Большой палец-1 (большинство), отсутствуют CBZ, CBNZ, IT.

- Thumb-2 (некоторые), только BL, DMB, DSB, ISB, MRS, MSR.

- Умножение 32-битного аппаратного целого числа с 32-битным результатом.

- От 1 до 32 прерываний плюс NMI .

Варианты кремния:

- Скорость аппаратного целочисленного умножения: 3 или 33 цикла.

- Дополнительная тесно связанная память (TCM): от 0 до 1 МБ инструкций-TCM, от 0 до 1 МБ данных-TCM, каждая с дополнительным ECC.

- Внешние прерывания: 0, 1, 8, 16, 32.

- Отладка: нет, сокращенная, полная.

- Порядок данных: с прямым порядком байтов или с прямым порядком байтов BE-8.

- Расширение ОС: присутствует или отсутствует.

Чипсы

[ редактировать ]Следующие производители поддерживают Cortex-M1 в качестве программных ядер своих чипов FPGA:

- Альтера Циклон-II, Циклон-III, Стратикс-II, Стратикс-III

- ГОВИН М1 [33]

- Actel / Microsemi / Microchip Fusion, IGLOO/e, ProASIC3L, ProASIC3/E

- Ксилинкс Спартанец-3, Виртукс-2, Виртукс-3, Виртукс-4, Артикс-7 [34]

Кортекс-М3

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | АРМв7-М |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный (немного), Разделить |

Ключевые особенности ядра Cortex-M3: [20] [35]

- Архитектура ARMv7-M [15]

- 3-этапный конвейер со спекуляцией ветвей .

- Наборы инструкций:

- Большой палец-1 (весь).

- Большой палец-2 (целый).

- 32-битное аппаратное целочисленное умножение с 32-битным или 64-битным результатом, со знаком или без знака, сложение или вычитание после умножения. 32-битное умножение занимает 1 цикл, но 64-битное умножение и инструкции MAC требуют дополнительных циклов.

- 32-битное аппаратное целочисленное деление (2–12 тактов).

- поддержка арифметики насыщения .

- От 1 до 240 прерываний плюс NMI .

- Задержка прерывания 12 циклов.

- Интегрированные режимы сна.

Варианты кремния:

- Дополнительный модуль защиты памяти (MPU): 0 или 8 регионов.

Чипсы

[ редактировать ]На ядре Cortex-M3 созданы следующие микроконтроллеры:

- АБОВ AC33Mx128, AC33Mx064

- Actel / Microsemi / Microchip SmartFusion, SmartFusion 2 (FPGA)

- Аналоговые устройства ADUCM360, ADUCM361, ADUCM3029

- Broadcom BCM4319XKUBG Чип Wi-Fi

- Кипарис PSoC 5000, 5000LP, FM3

- Холтек HT32F

- Инфинеон TLE9860, TLE987x

- Микрочип (Atmel) SAM 3A, 3N, 3S, 3U, 3X

- НСП ЛПК1300 , ЛПК1700 , ЛПК1800

- НА Q32M210

- Реалтек RTL8710

- Кремниевая лаборатория Precision32

- Silicon Labs ( Energy Micro ) EFM32 Tiny, Gecko, Leopard, Giant

- СТ STM32 F1, F2, L1, W

- TDK-Микроны HVC4223F

- Texas Instruments F28, LM3, TMS470, OMAP 4 , беспроводные микроконтроллеры SimpleLink (CC1310 Sub-GHZ и CC2650 BLE + Zigbee + 6LoWPAN )

- Тошиба ТХ03

- Mindmotion Mindmotion MM32

Следующие чипы имеют Cortex-M3 в качестве вторичного ядра:

- Apple A9 (Cortex-M3 в качестве встроенного сопроцессора движения M9 )

- CSR Quatro 5300 (Cortex-M3 в качестве сопроцессора)

- Samsung Exynos 7420 (Cortex-M3 в качестве микроконтроллера DVS ) [36]

- Texas Instruments F28, LM3, TMS470, OMAP 4470 (один Cortex-A9 + два Cortex-M3)

- XMOS XS1-XA (семь xCORE + один Cortex-M3)

Следующие FPGA включают ядро Cortex-M3:

- Микросеми SmartFusion2 SoC

Следующие производители поддерживают Cortex-M3 в качестве программных ядер своих чипов FPGA:

- Альтера Циклон-II, Циклон-III, Стратикс-II, Стратикс-III

- Ксилинкс Спартанец-3, Виртукс-2, Виртукс-3, Виртукс-4, Артикс-7 [37]

Кортекс-М4

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMv7E-M |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (СП) |

Концептуально Cortex-M4 представляет собой Cortex-M3 плюс инструкции DSP и дополнительный модуль с плавающей запятой (FPU). Ядро с FPU известно как Cortex-M4F.

Ключевые особенности ядра Cortex-M4: [21]

- Архитектура ARMv7E-M [15]

- 3-этапный конвейер со спекуляцией ветвей .

- Наборы инструкций:

- Большой палец-1 (весь).

- Большой палец-2 (целый).

- 32-битное аппаратное целочисленное умножение с 32-битным или 64-битным результатом, со знаком или без знака, сложение или вычитание после умножения. 32-битное умножение и MAC составляют 1 цикл.

- 32-битное аппаратное целочисленное деление (2–12 тактов).

- Поддержка арифметики насыщения .

- Расширение DSP: 16/32-битный MAC 8/16-бит за один цикл, двойной 16-битный MAC за один цикл, арифметика SIMD .

- От 1 до 240 прерываний плюс NMI .

- Задержка прерывания 12 циклов.

- Интегрированные режимы сна.

Варианты кремния:

- Дополнительный модуль с плавающей запятой (FPU): соответствует только стандарту одинарной точности IEEE-754 . Оно называется расширением FPv4-SP.

- Дополнительный блок защиты памяти (MPU): 0 или 8 регионов.

Чипсы

[ редактировать ]

На ядре Cortex-M4 созданы следующие микроконтроллеры:

- Аналоговые устройства ADSP-CM40x

- Микросхема (Atmel) SAM 4L, 4N, 4S

- NXP ( Freescale ) Кинетис К, W2

- ST ( STM32 ) WL (один Cortex-M4 + один Cortex-M0+)

- Texas Instruments SimpleLink Wi-Fi CC32xx, CC32xxMOD

) созданы следующие микроконтроллеры На ядре Cortex-M4F (M4+ FPU :

- Аналоговые устройства ADUCM4050

- Cypress 6200 (один Cortex-M4F + один Cortex-M0+), FM4

- Инфинеон XMC4000

- Максим Дарвин

- Микрочип (Atmel) SAM4C (двухъядерный: один Cortex-M4F + один Cortex-M4), SAM4E, SAM4L, SAM4N, SAM4S, SAMG5, SAMD5/E5x

- Скандинавский nRF52

- Нувотон Нумикро М480

- NXP LPC4000 , LPC4300 (один Cortex-M4F + один Cortex-M0), LPC54000

- NXP ( Freescale ) Кинетис К, V3, V4, S32K14x

- Ренесас С3, С5, С7, РА4, РА6

- Silicon Labs ( Energy Micro ) EFM32 Wonder

- ST STM32 F3, F4, L4, L4+, G4, WB (один Cortex-M4F + один Cortex-M0+)

- Texas Instruments LM4F, TM4C, MSP432 , CC13x2R, CC1352P, CC26x2R

- Тошиба ТХ04

Следующие чипы имеют Cortex-M4 или M4F в качестве вторичного ядра:

- NXP ( Freescale ) Vybrid VF6 (один Cortex-A5 + один Cortex-M4F)

- NXP ( Freescale ) i.MX 6 SoloX (один Cortex-A9 + один Cortex-M4F)

- NXP ( Freescale ) i.MX 7 Solo/Dual (один или два Cortex-A7 + один Cortex-M4F)

- NXP ( Freescale ) i.MX 8 (два Cortex-A72 + четыре Cortex-A53 + два Cortex-M4F)

- NXP ( Freescale ) i.MX 8M и 8M Mini (четыре Cortex-A53 + один Cortex-M4F)

- NXP ( Freescale ) i.MX 8X (четыре Cortex-A35 + один Cortex-M4F)

- ST STM32MP1 (один или два Cortex-A7 + один Cortex-M4)

- Texas Instruments OMAP 5 (два Cortex-A15 + два Cortex-M4)

- Texas Instruments Sitara AM5700 (один или два Cortex-A15 + два Cortex-M4 в качестве блоков обработки изображений + два Cortex-M4 в качестве блоков общего назначения)

Кортекс-М7

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMv7E-M |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделение, FPU (SP и DP) |

Cortex-M7 — это высокопроизводительное ядро, энергоэффективность которого почти вдвое выше, чем у старого Cortex-M4. [7] Он оснащен 6-ступенчатым суперскалярным конвейером с прогнозированием ветвей и дополнительным модулем с плавающей запятой, способным выполнять операции с одинарной и, опционально, двойной точностью . [7] [38] Шины инструкций и данных были увеличены до 64-битной ширины по сравнению с предыдущими 32-битными шинами. Если ядро содержит FPU, оно называется Cortex-M7F, в противном случае — Cortex-M7.

Ключевые особенности ядра Cortex-M7: [22]

- Архитектура ARMv7E-M.

- 6-ступенчатый конвейер со спекуляцией ветвей . Второе по длине ядро ARM Cortex-M, первое — Cortex-M85.

- Наборы инструкций:

- Большой палец-1 (весь).

- Большой палец-2 (целый).

- 32-битное аппаратное целочисленное умножение с 32-битным или 64-битным результатом, со знаком или без знака, сложение или вычитание после умножения. 32-битное умножение и MAC составляют 1 цикл.

- 32-битное аппаратное целочисленное деление (2–12 тактов).

- Поддержка арифметики насыщения .

- Расширение DSP: 16/32-битный MAC 8/16-бит за один цикл, двойной 16-битный MAC за один цикл, арифметика SIMD .

- От 1 до 240 прерываний плюс NMI .

- Задержка прерывания 12 циклов.

- Интегрированные режимы сна.

Варианты кремния:

- Дополнительный модуль с плавающей запятой (FPU): (одинарной точности) или (одинарной и двойной точности), оба совместимы с IEEE-754-2008. Это называется расширением FPv5.

- Дополнительный кэш ЦП : кэш инструкций от 0 до 64 КБ, кэш данных от 0 до 64 КБ, каждый с дополнительным ECC .

- Дополнительная тесно связанная память (TCM): от 0 до 16 МБ инструкций-TCM, от 0 до 16 МБ данных-TCM, каждая с дополнительным ECC.

- Дополнительный блок защиты памяти (MPU): 8 или 16 регионов.

- Дополнительная встроенная макроячейка трассировки (ETM): только инструкции или инструкции и данные.

- Дополнительный режим сохранения (с комплектом управления питанием руки) для спящих режимов.

- Дополнительный режим с двойным резервированием пошаговый .

Чипсы

[ редактировать ]На ядре Cortex-M7 созданы следующие микроконтроллеры:

Кортекс-М23

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | Базовый уровень ARMv8-M |

| Набор инструкций | Большой палец-1 (большинство) , Большой палец-2 (некоторые) , Разделить, TrustZone |

Ядро Cortex-M23 было анонсировано в октябре 2016 года. [39] и основан на архитектуре ARMv8-M , анонсированной ранее в ноябре 2015 года. [40] Концептуально Cortex-M23 аналогичен Cortex-M0+ плюс инструкции целочисленного деления и функции безопасности TrustZone, а также имеет двухэтапный конвейер инструкций . [8]

Ключевые особенности ядра Cortex-M23: [23] [39]

- Базовая архитектура ARMv8-M. [30]

- 2-ступенчатый трубопровод. (аналог Cortex-M0+)

- Инструкции по безопасности TrustZone .

- 32-битное аппаратное целочисленное деление (17 или 34 цикла). (медленнее, чем деление во всех других ядрах)

- Границы ограничения стека. (доступно только с опцией САУ)

Варианты кремния:

- Скорость аппаратного целочисленного умножения: 1 или 32 цикла.

- Скорость аппаратного целочисленного деления: максимум 17 или 34 цикла. В зависимости от делителя инструкция может выполняться за меньшее количество циклов.

- Дополнительный блок защиты памяти (MPU): 0, 4, 8, 12, 16 регионов.

- Дополнительный блок атрибуции безопасности (SAU): 0, 4, 8 регионов.

- Однотактный порт ввода-вывода (доступен в M0+/M23).

- Микробуфер трассировки (MTB)

Чипсы

[ редактировать ]На ядре Cortex-M23 созданы следующие микроконтроллеры:

- GigaDevice GD32E2xx

- Микрочип SAM L10, L11 и PIC 32CM-LE 32CM-LS

- Nuvoton M23xx, семейство M2xx, NUC1262, M2L31 Семейство

- Ренесас S1JA, RA2A1, RA2L1, RA2E1, RA2E2

Кортекс-М33

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | Основная линия ARMv8-M |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (СП), TrustZone , Сопроцессор |

Ядро Cortex-M33 было анонсировано в октябре 2016 года. [39] и основан на архитектуре ARMv8-M , анонсированной ранее в ноябре 2015 года. [40] Концептуально Cortex-M33 похож на смесь Cortex-M4 и Cortex-M23 и также имеет трехэтапный конвейер команд . [9]

Ключевые особенности ядра Cortex-M33: [24] [39]

- Основная архитектура ARMv8-M. [30]

- 3-ступенчатый трубопровод.

- Инструкции по безопасности TrustZone .

- 32-битное аппаратное целочисленное деление (максимум 11 циклов).

- Границы ограничения стека. (доступно только с опцией САУ)

Варианты кремния:

- Дополнительный модуль с плавающей запятой (FPU): соответствует только стандарту одинарной точности IEEE-754 . Это называется расширением FPv5.

- Дополнительный блок защиты памяти (MPU): 0, 4, 8, 12, 16 регионов.

- Дополнительный блок атрибуции безопасности (SAU): 0, 4, 8 регионов.

- Микробуфер трассировки (MTB)

Чипсы

[ редактировать ]На ядре Cortex-M33 созданы следующие микроконтроллеры:

- Аналоговые устройства ADUCM4

- Диалог DA1469x

- GigaDevice GD32E5, GD32W5

- Скандинавские nRF91, nRF5340, nRF54

- NXP LPC5500, i.MX RT600, MCX N94x/54x (двухъядерный)

- НА РГБ15

- Ренесас РА4, РА6

- СТ STM32 H5, L5, U5, WBA

- Silicon Labs Wireless Gecko Series 2

Следующие чипы имеют Cortex-M33 или M33F в качестве вторичного ядра:

Кортекс-М35П

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | Основная линия ARMv8-M |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (СП), TrustZone , Сопроцессор |

Ядро Cortex-M35P было анонсировано в мае 2018 года и основано на архитектуре Armv8-M . Концептуально это ядро Cortex-M33 с новым кэшем инструкций, а также новые концепции аппаратного обеспечения с защитой от несанкционированного доступа, заимствованные из семейства ARM SecurCore, а также настраиваемые функции четности и ECC. [10]

В настоящее время информация о Cortex-M35P ограничена, поскольку его техническое справочное руководство и общее руководство пользователя еще не выпущены.

Чипсы

[ редактировать ]На ядре Cortex-M35P созданы следующие микроконтроллеры:

- СТМикроэлектроника СТ33К

Кортекс-М52

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMv8.1-M Магистральный гелий |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (VFPv5), TrustZone , Сопроцессор, MVE |

Ядро Cortex-M52 было анонсировано в ноябре 2023 года и основано на архитектуре Armv8.1-M . Он имеет четырехэтапный конвейер инструкций. [11]

Ключевые особенности ядра Cortex-M52 включают в себя:

- Архитектура ARMv8.1-M Mainline/Helium. [30]

- 4-ступенчатый трубопровод.

- Границы ограничения стека (доступно только с опцией SAU).

Варианты кремния:

- Гелий (векторное расширение M-профиля, MVE)

- Числа с плавающей запятой одинарной и двойной точности.

- Поддержка расширения цифровой обработки сигналов (DSP)

- TrustZone Поддержка расширения безопасности

- Поддержка безопасности и надежности (RAS)

- Поддержка сопроцессора

- Безопасный и незащищенный MPU с 0, 4, 8, 12 или 16 областями.

- SAU с 0, 4 или 8 регионами

- Кэш инструкций размером до 64 КБ.

- Кэш данных размером до 64 КБ

- ECC для кэшей и TCM

- 1–480 прерываний

- 3–8 бит приоритета исключения

- Внутренние и внешние опции WIC, дополнительные CTI, ITM и DWT

- Пользовательские инструкции ARM

Чипсы

[ редактировать ]- По состоянию на декабрь 2023 года о чипах не сообщалось.

Кортекс-М55

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMv8.1-M Магистральный гелий |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (VFPv5), TrustZone , Сопроцессор, MVE |

Ядро Cortex-M55 было анонсировано в феврале 2020 года и основано на архитектуре Armv8.1-M . Он имеет четырех- или пятиэтапный конвейер инструкций. [12]

Ключевые особенности ядра Cortex-M55 включают в себя:

- Архитектура ARMv8.1-M Mainline/Helium. [30]

- 4-ступенчатый трубопровод.

- Границы ограничения стека (доступно только с опцией SAU).

Варианты кремния:

- Гелий (векторное расширение M-профиля, MVE)

- Числа с плавающей запятой одинарной и двойной точности.

- Поддержка расширения цифровой обработки сигналов (DSP)

- TrustZone Поддержка расширения безопасности

- Поддержка безопасности и надежности (RAS)

- Поддержка сопроцессора

- Безопасный и незащищенный MPU с 0, 4, 8, 12 или 16 областями.

- SAU с 0, 4 или 8 регионами

- Кэш инструкций размером 4 КБ, 8 КБ, 16 КБ, 32 КБ, 64 КБ.

- Кэш данных размером 4 КБ, 8 КБ, 16 КБ, 32 КБ, 64 КБ

- ECC для кэшей и TCM

- 1–480 прерываний

- 3–8 бит приоритета исключения

- Внутренние и внешние опции WIC, дополнительные CTI, ITM и DWT

- Пользовательские инструкции ARM

Чипсы

[ редактировать ]- Семейства микроконтроллеров Alif Semiconductor Ensemble предлагают одно или два ядра Cortex-M55, каждое из которых соединено с NPU Ethos-U55.

- Infineon PSoC Edge

Кортекс-М85

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMv8.1-M Магистральный гелий |

| Набор инструкций | Большой палец-1 , Большой палец-2 , Насыщенный , DSP , Разделить, ФПУ (VFPv5), TrustZone , Сопроцессор, MVE |

Ядро Cortex-M85 было анонсировано в апреле 2022 года и основано на архитектуре Armv8.1-M . Он имеет 7-этапный конвейер инструкций. [13]

Варианты кремния:

- Дополнительный кэш ЦП : кэш инструкций от 0 до 64 КБ, кэш данных от 0 до 64 КБ, каждый с дополнительным ECC .

- Дополнительная тесно связанная память (TCM): от 0 до 16 МБ инструкций-TCM, от 0 до 16 МБ данных-TCM, каждая с дополнительным ECC.

- Дополнительный блок защиты памяти (MPU): 16 регионов. Могут иметь отдельные режимы для безопасного и незащищенного режима, если TrustZone . реализован

- До 480 прерываний и NMI

- 3–8 бит приоритета исключения

- Дополнительный режим с двойным резервированием пошаговый .

Чипсы

[ редактировать ]- Ренесас RA8

Инструменты разработки

[ редактировать ]Документация

[ редактировать ]Документация по чипам ARM обширна. Раньше документация по 8-битным микроконтроллерам обычно помещалась в один документ, но по мере развития микроконтроллеров появилось и все необходимое для их поддержки. Пакет документации для чипов ARM обычно состоит из набора документов от производителя микросхемы, а также поставщика ядра ЦП ( ARM Limited ).

Типичное дерево документации сверху вниз:

- Дерево документации (сверху вниз)

- Сайт производителя микросхем.

- Маркетинговые слайды производителя микросхем.

- Спецификация производителя микросхемы для конкретного физического чипа.

- Справочное руководство производителя микросхем, в котором описываются общие периферийные устройства и аспекты семейства физических микросхем.

- Основной веб-сайт ARM.

- Общее руководство пользователя ядра ARM.

- Техническое справочное руководство по ядру ARM.

- Справочное руководство по архитектуре ARM.

Производители микросхем имеют дополнительные документы, такие как: руководства пользователя оценочной платы, рекомендации по применению, руководства по началу работы, документы библиотеки программного обеспечения, список ошибок и многое другое. см . в разделе «Внешние ссылки» Ссылки на официальные документы Arm .

См. также

[ редактировать ]- ARM-архитектура

- Список архитектур и ядер ARM

- Прерывание , Обработчик прерываний

- Операционная система реального времени , Сравнение операционных систем реального времени

Ссылки

[ редактировать ]- ^ Веб-сайт ARM Cortex-M; АРМ Лимитед.

- ^ Перейти обратно: а б «Кортекс-М0 Дом» . АРМ Лимитед .

- ^ «Кортекс-М0+ Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М1 Дом» . АРМ Лимитед .

- ^ «Кортекс-М3 Дом» . АРМ Лимитед .

- ^ «Кортекс-М4 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Кортекс-М7 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М23 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М33 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Кортекс-М35П Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М52 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М55 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б «Кортекс-М85 Дом» . АРМ Лимитед .

- ^ Перейти обратно: а б с д и ж г час я дж к л м н тот п д р «Справочное руководство по архитектуре ARMv6-M» . АРМ Лимитед .

- ^ Перейти обратно: а б с д и ж г час я дж к л м н тот п д р «Справочное руководство по архитектуре ARMv7-M» . АРМ Лимитед .

- ^ Перейти обратно: а б с д Разработка встроенного программного обеспечения Cortex-M3; Примечание приложения 179; АРМ Лимитед.

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M0» . АРМ Лимитед .

- ^ Перейти обратно: а б с д «Техническое справочное руководство Cortex-M0+» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M1» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M3» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M4» . АРМ Лимитед .

- ^ Перейти обратно: а б с д «Техническое справочное руководство Cortex-M7» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M23» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Техническое справочное руководство Cortex-M33» . АРМ Лимитед .

- ^ Перейти обратно: а б «Техническое справочное руководство Cortex-M52» . АРМ Лимитед .

- ^ Перейти обратно: а б «Техническое справочное руководство Cortex-M55» . АРМ Лимитед .

- ^ Перейти обратно: а б «Техническое справочное руководство Cortex-M85» . АРМ Лимитед .

- ^ Перейти обратно: а б с «Комплект проектирования системы Cortex-M (CMSDK)» . Арм Холдингс . Архивировано из оригинала 4 марта 2016 года.

- ^ Перейти обратно: а б с д и ж г час я дж Руководство по программированию ARM Cortex-M для инструкций с барьером памяти; Раздел 3.6 Требования к реализации системы; ПриложениеNote 321; АРМ Лимитед.

- ^ Перейти обратно: а б с д и ж г час я дж к л «Справочное руководство по архитектуре ARMv8-M» . АРМ Лимитед .

- ^ 32-битные микроконтроллеры PIC и SAM; Микрочип.

- ^ Фингас, Джон (25 февраля 2014 г.). «Freescale делает самый маленький в мире чип контроллера ARM еще меньше» . Проверено 2 октября 2014 г.

- ^ GOWIN Semiconductor присоединяется к ARM DesignStart, предлагая бесплатные процессоры ARM Cortex-M1 для своих семейств продуктов FPGA.

- ^ Cortex-M1 DesignStart FPGA XilinxEdition; АРМ Лимитед.

- ^ Садасиван, Шьям. «Введение в процессор ARM Cortex-M3» (PDF) . АРМ Лимитед. Архивировано из оригинала (PDF) 26 июля 2014 г.

- ^ «Глубокий обзор Samsung Exynos 7420 — внутри современной 14-нм SoC» . АнандТех . Проверено 15 июня 2015 г.

- ^ Cortex-M3 DesignStart FPGA XilinxEdition

- ^ «ARM расширяет рынок микроконтроллеров высокопроизводительным процессором Cortex-M7» . АРМ Лимитед (Пресс-релиз). 24 сентября 2014 г.

- ^ Перейти обратно: а б с д Новые процессоры ARM Cortex-M предлагают следующий отраслевой стандарт безопасного Интернета вещей; АРМ Лимитед; 25 октября 2016 г.

- ^ Перейти обратно: а б Архитектура ARMv8-M упрощает безопасность встраиваемых интеллектуальных устройств; АРМ Лимитед; 10 ноября 2015 г.

Дальнейшее чтение

[ редактировать ]- Руководство дизайнера по семейству процессоров Cortex-M ; 3-е изд.; Тревор Мартин; 648 страниц; 2022 год; ISBN 978-0323854948 .

- Полное руководство по процессорам ARM Cortex-M0 и Cortex-M0+ ; 2-е изд.; Джозеф Ю; 784 страницы; 2015 г.; ISBN 978-0128032770 .

- Полное руководство по процессорам ARM Cortex-M3 и Cortex-M4 ; 3-е изд.; Джозеф Ю; 864 страницы; 2013 г.; ISBN 978-0124080829 .

- Полное руководство по процессорам ARM Cortex-M23 и Cortex-M33 ; 1-е изд; Джозеф Ю; 928 страниц; 2020; ISBN 978-0128207352 .

- Микроконтроллеры с C: Cortex-M и выше ; 1-е изд; Клаус Элк; 227 страниц; 2023 год; ISBN 979-8862003437 .

- Встраиваемые системы с микроконтроллерами ARM Cortex-M на языке ассемблера и C ; 4-е изд; Ифэн Чжу; 730 страниц; 2023 год; ISBN 978-0982692677 .

- Сборка ARM для встраиваемых приложений ; 5-е изд; Дэниел Льюис; 379 страниц; 2019 год; ISBN 978-1092542234 .

- Программирование на языке ассемблера: ARM Cortex-M3 ; 1-е изд; Винсент Маут; 256 страниц; 2012 г.; ISBN 978-1848213296 .

- Цифровая обработка сигналов и приложения с использованием ARM Cortex-M4 ; 1-е изд; Дональд Рей; 320 страниц; 2015 г.; ISBN 978-1118859049 .

- Практическая работа с ОСРВ с микроконтроллерами ; 1-е изд; Брайан Эймос; 496 страниц; 2020; ISBN 978-1838826734 .

Внешние ссылки

[ редактировать ]- Официальные документы ARM Cortex-M

- Официальный сайт ARM Cortex-M

- Кортекс-М для начинающих Arm.com

- Расширения безопасности ARMv8-M Arm.com

- Стандарт программного интерфейса микроконтроллера Cortex (CMSIS) Arm.com

РУКА

основнойКусочек

ширинаРУКА

веб-сайтARM универсальный

руководство пользователяТехнические характеристики ARM

справочное руководствоARM-архитектура

справочное руководствоКортекс-М0 32 Связь Связь Связь АРМв6-М Кортекс-М0+ 32 Связь Связь Связь АРМв6-М Кортекс-М1 32 Связь Связь Связь АРМв6-М Кортекс-М3 32 Связь Связь Связь АРМв7-М Кортекс-М4 32 Связь Связь Связь ARMv7E-M Кортекс-М7 32 Связь Связь Связь ARMv7E-M Кортекс-М23 32 Связь Связь Связь АРМв8-М Кортекс-М33 32 Связь Связь Связь АРМв8-М Кортекс-М35П 32 Связь Н/Д Н/Д АРМв8-М Кортекс-М52 32 Связь Н/Д Связь ARMv8.1-М Кортекс-М55 32 Связь Связь Связь ARMv8.1-М Кортекс-М85 32 Связь Связь Связь ARMv8.1-М

- Краткие справочные карточки

- Инструкции: Thumb-1 ( 1 ), ARM и Thumb-2 ( 2 ), вектор с плавающей запятой ( 3 ) Arm.com

- Коды операций: Thumb-1 ( 1 , 2 ), ARM ( 3 , 4 ), Директивы ассемблера GNU ( 5 ).

- Миграция

- Миграция с 8051 на Cortex-M3 –arm.com

- Миграция с PIC на Cortex-M3 –arm.com

- Миграция с ARM7TDMI на Cortex-M3 – Arm.com

- Миграция с Cortex-M4 на Cortex-M7 – keil.com

- Другой