Сложное программируемое логическое устройство

Эта статья нуждается в дополнительных цитатах для проверки . ( ноябрь 2013 г. ) |

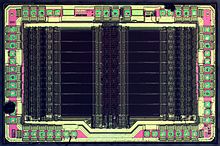

Сложное программируемое логическое устройство ( CPLD ) — это программируемое логическое устройство, сложность которого находится между PAL и FPGA , а также архитектурные особенности обоих. Основным строительным блоком CPLD является макроячейка , которая содержит логику, реализующую дизъюнктивные выражения нормальной формы и более специализированные логические операции.

Функции

[ редактировать ]Некоторые функции CPLD схожи с PAL :

- Энергонезависимая память конфигурации. В отличие от многих FPGA, внешнее ПЗУ конфигурации не требуется, и CPLD может функционировать сразу при запуске системы.

- Для многих устаревших устройств CPLD маршрутизация ограничивает большинство логических блоков подключением входных и выходных сигналов к внешним контактам, что сокращает возможности внутреннего хранения состояний и глубокой многоуровневой логики. Обычно это не имеет значения для более крупных CPLD и новых семейств продуктов CPLD.

Другие функции являются общими с FPGA :

- Наличие большого количества ворот. CPLD обычно имеют эквивалент от тысяч до десятков тысяч логических вентилей , что позволяет реализовать устройства обработки данных средней сложности. PAL обычно имеют максимум несколько сотен эквивалентов вентилей, тогда как FPGA обычно варьируются от десятков тысяч до нескольких миллионов.

- Некоторые положения для более гибкой логики, чем выражения суммы произведений , включая сложные пути обратной связи между макроячейками и специализированную логику для реализации различных часто используемых функций, таких как целочисленная арифметика .

Наиболее заметной разницей между большим CPLD и маленькой FPGA является наличие внутрикристальной энергонезависимой памяти в CPLD, что позволяет использовать CPLD для функций « загрузчика », прежде чем передать управление другим устройствам, не имеющим их. собственное постоянное хранилище программ. Хорошим примером является использование CPLD для загрузки данных конфигурации FPGA из энергонезависимой памяти. [1]

Отличия

[ редактировать ]CPLD были эволюционным шагом по сравнению с предшествовавшими им еще меньшими устройствами: PLA (впервые выпущенными Signetics ) и PAL . Им, в свою очередь, предшествовали стандартные логические продукты, которые не допускали программирования и использовались для создания логических функций путем физического соединения нескольких стандартных логических микросхем (или сотен их) вместе (обычно с подключением на печатной плате или платах, но иногда, особенно для прототипирования с использованием проволочной проводки).

Основное различие между архитектурами устройств FPGA и CPLD заключается в том, что CPLD внутренне основаны на наборе PLD, сопровождаемых программируемой структурой межсоединений, тогда как FPGA используют логические блоки .

См. также

[ редактировать ]- Язык:

- Производители:

- Альтера (теперь Intel)

- Кипарисовый полупроводник

- Решетка полупроводника

- Microchip Technology (ранее Actel )

- Xilinx (теперь AMD)

- Технология:

- Интегральная схема специального назначения (ASIC)

- Стираемое программируемое логическое устройство (EPLD)

- Простое программируемое логическое устройство (SPLD)

- Массив макроячеек

- Программируемая логика массива (PAL)

- Программируемая логическая матрица (PLA)

- Программируемое логическое устройство (ПЛД)

- Общая логика массива (GAL)

- Программируемая электрически стираемая логика (PEEL)

- Программируемая пользователем вентильная матрица (FPGA)

Ссылки

[ редактировать ]- ^ «Сложное программируемое логическое устройство» . blogspot.com. Май 2008 года . Проверено 17 ноября 2013 г.