Arm Cortex-M

24 MHz ARM Cortex-M3 microcontroller with 16 KB flash memory, 4 KB RAM. Manufactured by STMicroelectronics.

Arm Cortex-M представляет собой группу 32-битных процессоров RISC ARM -процессора, лицензированных ARM Limited . Эти ядра оптимизированы для недорогих и энергоэффективных интегрированных цепей, которые были включены в десятки миллиардов потребительских устройств. [ 1 ] Хотя они чаще всего являются основным компонентом чипов микроконтроллера , иногда они также встроены в другие типы чипов. Семейство Cortex-M состоит из Cortex-M0, [ 2 ] Cortex-M0+, [ 3 ] Кора-м1, [ 4 ] Кора-м3, [ 5 ] Кора-м4, [ 6 ] Кора-м7, [ 7 ] Cortex-M23, [ 8 ] Cortex-M33, [ 9 ] Cortex-M35p, [ 10 ] Cortex-M52, [ 11 ] Cortex-M55, [ 12 ] Cortex-M85. [ 13 ] M35P / M52 / M55 / M85, а также Для Cortex-M4 / M7 / M33 / M35P / M52 / M55 / M85 / M33 / включен в кремний, иногда эти ядра иногда называют 'это основной вариант.

Обзор

[ редактировать ]| 32-bit | |

|---|---|

| Year | Core |

| 2004 | Cortex-M3 |

| 2007 | Cortex-M1 |

| 2009 | Cortex-M0 |

| 2010 | Cortex-M4 |

| 2012 | Cortex-M0+ |

| 2014 | Cortex-M7 |

| 2016 | Cortex-M23 |

| 2016 | Cortex-M33 |

| 2018 | Cortex-M35P |

| 2020 | Cortex-M55 |

| 2022 | Cortex-M85 |

| 2023 | Cortex-M52 |

The ARM Cortex-M family are ARM microprocessor cores that are designed for use in microcontrollers, ASICs, ASSPs, FPGAs, and SoCs. Cortex-M cores are commonly used as dedicated microcontroller chips, but also are "hidden" inside of SoC chips as power management controllers, I/O controllers, system controllers, touch screen controllers, smart battery controllers, and sensor controllers.

The main difference from Cortex-A cores is that Cortex-M cores have no memory management unit (MMU) for virtual memory, considered essential for "full-fledged" operating systems. Cortex-M programs instead run bare metal or on one of the many real-time operating systems which support a Cortex-M.

Though 8-bit microcontrollers were very popular in the past, Cortex-M has slowly been chipping away at the 8-bit market as the prices of low-end Cortex-M chips have moved downward. Cortex-M have become a popular replacements for 8-bit chips in applications that benefit from 32-bit math operations, and replacing older legacy ARM cores such as ARM7 and ARM9.

License

[edit]ARM Limited neither manufactures nor sells CPU devices based on its own designs, but rather licenses the processor architecture to interested parties. Arm offers a variety of licensing terms, varying in cost and deliverables. To all licensees, Arm provides an integratable hardware description of the ARM core, as well as complete software development toolset and the right to sell manufactured silicon containing the ARM CPU.

Silicon customization

[edit]Integrated Device Manufacturers (IDM) receive the ARM Processor IP as synthesizable RTL (written in Verilog). In this form, they have the ability to perform architectural level optimizations and extensions. This allows the manufacturer to achieve custom design goals, such as higher clock speed, very low power consumption, instruction set extensions (including floating point), optimizations for size, debug support, etc. To determine which components have been included in a particular ARM CPU chip, consult the manufacturer datasheet and related documentation.

Some of the silicon options for the Cortex-M cores are:

- SysTick timer: A 24-bit system timer that extends the functionality of both the processor and the Nested Vectored Interrupt Controller (NVIC). When present, it also provides an additional configurable priority SysTick interrupt.[14][15][16] Though the SysTick timer is optional for the M0/M0+/M1/M23, it is extremely rare to find a Cortex-M microcontroller without it. If a Cortex-M33/M35P/M52/M55/M85 microcontroller has the Security Extension option, then it optionally can have two SysTicks (one Secure, one Non-secure).

- Bit-Band: Maps a complete word of memory onto a single bit in the bit-band region. For example, writing to an alias word will set or clear the corresponding bit in the bit-band region. This allows every individual bit in the bit-band region to be directly accessible from a word-aligned address. In particular, individual bits can be set, cleared, or toggled from C/C++ without performing a read-modify-write sequence of instructions.[14][15][16] Though the bit-band is optional, it is less common to find a Cortex-M3 and Cortex-M4 microcontroller without it. Some Cortex-M0 and Cortex-M0+ microcontrollers have bit-band.

- Memory Protection Unit (MPU): Provides support for protecting regions of memory through enforcing privilege and access rules. It supports up to sixteen different regions, each of which can be split further into equal-size sub-regions.[14][15][16]

- Tightly-Coupled Memory (TCM): Low-latency (zero wait state) SRAM that can be used to hold the call stack, RTOS control structures, interrupt data structures, interrupt handler code, and speed critical code. Other than CPU cache, TCM is the fastest memory in an ARM Cortex-M microcontroller. Since TCM isn't cached and accessible at the same speed as the processor and cache, it could be conceptually described as "addressable cache". There is an ITCM (Instruction TCM) and a DTCM (Data TCM) to allow a Harvard architecture processor to read from both simultaneously. The DTCM can't contain any instructions, but the ITCM can contain data. Since TCM is tightly connected to the processor core, DMA engines might not be able to access TCM on some implementations.

| ARM Core | Cortex M0 [17] |

Cortex M0+ [18] |

Cortex M1 [19] |

Cortex M3 [20] |

Cortex M4 [21] |

Cortex M7 [22] |

Cortex M23 [23] |

Cortex M33 [24] |

Cortex M35P [10] |

Cortex M52 [25] |

Cortex M55 [26] |

Cortex M85 [27] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SysTick 24-bit Timer | Optional (0,1) |

Optional (0, 1) |

Optional (0,1) |

Yes (1) |

Yes (1) |

Yes (1) |

Optional (0, 1, 2) |

Yes (1, 2) |

Yes (1, 2) |

Yes (1, 2) |

Yes (1, 2) |

Yes (1, 2) |

| Single-cycle I/O port | No | Optional | No | No | No | No | Optional | No | No | No | No | No |

| Bit-Band memory | No[28] | No[28] | No* | Optional | Optional | Optional | No | No | No | No | No | No |

| Memory Protection Unit (MPU) |

No | Optional (0, 8) |

No | Optional (0,8) |

Optional (0, 8) |

Optional (0, 8, 16) |

Optional (0, 4, 8, 12, 16) |

Optional (0, 4, 8, 12, 16) |

Optional (up to 16)* |

Optional (0, 4, 8, 12, 16) |

Optional (0, 4, 8, 12, 16) |

Optional (0, 4, 8, 12, 16) |

| Security Attribution Unit (SAU) and Stack Limits |

No | No | No | No | No | No | Optional (0, 4, 8) |

Optional (0, 4, 8) |

Optional (up to 8)* |

Optional (0, 4, 8) |

Optional (0, 4, 8) |

Optional (0, 4, 8) |

| Instruction Cache | No[29] | No[29] | No[29] | No[29] | No[29] | Optional (up to 64 KB) |

No | No | Optional (up to 16 KB) |

Optional (up to 64 KB) |

Optional (up to 64 KB) |

Optional (up to 64 KB) |

| Data Cache | No[29] | No[29] | No[29] | No[29] | No[29] | Optional (up to 64 KB) |

No | No | No | Optional (up to 64 KB) |

Optional (up to 64 KB) |

Optional (up to 64 KB) |

| Instruction TCM (ITCM) Memory |

No | No | Optional (up to 1 MB) |

No | No | Optional (up to 16 MB) |

No | No | No | Optional (up to 16 MB) |

Optional (up to 16 MB) |

Optional (up to 16 MB) |

| Data TCM (DTCM) Memory |

No | No | Optional (up to 1 MB) |

No | No | Optional (up to 16 MB) |

No | No | No | Optional (up to 16 MB) |

Optional (up to 16 MB) |

Optional (up to 16 MB) |

| ECC for TCM and Cache |

No | No | No | No | No | No | No | No | Optional | Optional | Optional | Optional |

| Vector Table Offset Register (VTOR) |

No | Optional (0,1) |

Optional (0,1) |

Optional (0,1) |

Optional (0,1) |

Optional (0,1) |

Optional (0,1,2) |

Yes (1,2) |

Yes (1,2) |

Yes (1,2) |

Yes (1,2) |

Yes (1,2) |

- Note: Most Cortex-M3 and M4 chips have bit-band and MPU. The bit-band option can be added to the M0/M0+ using the Cortex-M System Design Kit.[28]

- Note: Software should validate the existence of each feature before attempting to use it.[16]

- Note: Limited public information is available for the Cortex-M35P until its Technical Reference Manual is released.

Additional silicon options:[14][15]

- Data endianness: Little-endian or big-endian. Unlike legacy ARM cores, the Cortex-M is permanently fixed in silicon as one of these choices.

- Interrupts: 1 to 32 (M0/M0+/M1), 1 to 240 (M3/M4/M7/M23), 1 to 480 (M33/M35P/M52/M55/M85).

- Wake-up interrupt controller: Optional.

- Vector Table Offset Register: Optional. (not available for M0).

- Instruction fetch width: 16-bit only, or mostly 32-bit.

- User/privilege support: Optional.

- Reset all registers: Optional.

- Single-cycle I/O port: Optional. (M0+/M23).

- Debug Access Port (DAP): None, SWD, JTAG and SWD. (optional for all Cortex-M cores)

- Halting debug support: Optional.

- Number of watchpoint comparators: 0 to 2 (M0/M0+/M1), 0 to 4 (M3/M4/M7/M23/M33/M35P/M52/M55/M85).

- Number of breakpoint comparators: 0 to 4 (M0/M0+/M1/M23), 0 to 8 (M3/M4/M7/M33/M35P/M52/M55/M85).

Instruction sets

[edit]The Cortex-M0 / M0+ / M1 implement the ARMv6-M architecture,[14] the Cortex-M3 implements the ARMv7-M architecture,[15] the Cortex-M4 / Cortex-M7 implements the ARMv7E-M architecture,[15] the Cortex-M23 / M33 / M35P implement the ARMv8-M architecture,[30] and the Cortex-M52 / M55 / M85 implements the ARMv8.1-M architecture.[30] The architectures are binary instruction upward compatible from ARMv6-M to ARMv7-M to ARMv7E-M. Binary instructions available for the Cortex-M0 / Cortex-M0+ / Cortex-M1 can execute without modification on the Cortex-M3 / Cortex-M4 / Cortex-M7. Binary instructions available for the Cortex-M3 can execute without modification on the Cortex-M4 / Cortex-M7 / Cortex-M33 / Cortex-M35P.[14][15] Only Thumb-1 and Thumb-2 instruction sets are supported in Cortex-M architectures; the legacy 32-bit ARM instruction set isn't supported.

All Cortex-M cores implement a common subset of instructions that consists of most Thumb-1, some Thumb-2, including a 32-bit result multiply. The Cortex-M0 / Cortex-M0+ / Cortex-M1 / Cortex-M23 were designed to create the smallest silicon die, thus having the fewest instructions of the Cortex-M family.

The Cortex-M0 / M0+ / M1 include Thumb-1 instructions, except new instructions (CBZ, CBNZ, IT) which were added in ARMv7-M architecture. The Cortex-M0 / M0+ / M1 include a minor subset of Thumb-2 instructions (BL, DMB, DSB, ISB, MRS, MSR).[14] The Cortex-M3 / M4 / M7 / M33 / M35P have all base Thumb-1 and Thumb-2 instructions. The Cortex-M3 adds three Thumb-1 instructions, all Thumb-2 instructions, hardware integer divide, and saturation arithmetic instructions. The Cortex-M4 adds DSP instructions and an optional single-precision floating-point unit (VFPv4-SP). The Cortex-M7 adds an optional double-precision FPU (VFPv5).[22][15] The Cortex-M23 / M33 / M35P / M52 / M55 / M85 add TrustZone instructions.

| Arm Core | Cortex M0[17] |

Cortex M0+[18] |

Cortex M1[19] |

Cortex M3[20] |

Cortex M4[21] |

Cortex M7[22] |

Cortex M23[23] |

Cortex M33[24] |

Cortex M35P |

Cortex M52[25] |

Cortex M55[26] |

Cortex M85[27] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ARM architecture | ARMv6-M [14] |

ARMv6-M [14] |

ARMv6-M [14] |

ARMv7-M [15] |

ARMv7E-M [15] |

ARMv7E-M [15] |

ARMv8-M Baseline[30] |

ARMv8-M Mainline[30] |

ARMv8-M Mainline[30] |

Armv8.1-M Mainline[30] |

Armv8.1-M Mainline[30] |

Armv8.1-M Mainline[30] |

| Computer architecture | Von Neumann |

Von Neumann |

Von Neumann |

Harvard | Harvard | Harvard | Von Neumann |

Harvard | Harvard | Harvard | Harvard | Harvard |

| Instruction pipeline | 3 stages | 2 stages | 3 stages | 3 stages | 3 stages | 6 stages | 2 stages | 3 stages | 3 stages | 4 stages | 4-5 stages | 7 stages |

| Interrupt latency (zero wait state memory) |

16 cycles | 15 cycles | 23 for NMI, 26 for IRQ |

12 cycles | 12 cycles | 12 cycles, 14 worst case |

15 cycles, 24 secure to NS IRQ |

12 cycles, 21 secure to NS IRQ |

TBD | TBD | TBD | TBD |

| Thumb-1 instructions | Most | Most | Most | Entire | Entire | Entire | Most | Entire | Entire | Entire | Entire | Entire |

| Thumb-2 instructions | Some | Some | Some | Entire | Entire | Entire | Some | Entire | Entire | Entire | Entire | Entire |

| Multiply instructions 32×32 = 32-bit result |

Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Multiply instructions 32×32 = 64-bit result |

No | No | No | Yes | Yes | Yes | No | Yes | Yes | Yes | Yes | Yes |

| Divide instructions 32/32 = 32-bit quotient |

No | No | No | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Saturated math instructions | No | No | No | Some | Yes | Yes | No | Yes | Yes | Yes | Yes | Yes |

| DSP instructions | No | No | No | No | Yes | Yes | No | Optional | Optional | Yes | Yes | Yes |

| Half-Precision (HP) floating-point instructions |

No | No | No | No | No | No | No | No | No | Optional | Optional | Optional |

| Single-Precision (SP) floating-point instructions |

No | No | No | No | Optional | Optional | No | Optional | Optional | Optional | Optional | Optional |

| Double-Precision (DP) floating-point instructions |

No | No | No | No | No | Optional | No | No | No | Optional | Optional | Optional |

| Helium vector instructions | No | No | No | No | No | No | No | No | No | Optional | Optional | Optional |

| TrustZone security instructions | No | No | No | No | No | No | Optional | Optional | Optional | Optional | Optional | Yes |

| Co-processor instructions | No | No | No | No | No | No | No | Optional | Optional | Optional | Optional | Optional |

| ARM Custom Instructions (ACI) | No | No | No | No | No | No | No | Optional | No | Optional | Optional | Optional |

| Pointer Authentication and Branch Target Identification (PACBTI) instructions |

No | No | No | No | No | No | No | No | No | Optional | No | Optional |

- Note: Interrupt latency cycle count assumes: 1) stack located in zero-wait state RAM, 2) another interrupt function not currently executing, 3) Security Extension option doesn't exist, because it adds additional cycles. The Cortex-M cores with a Harvard computer architecture have a shorter interrupt latency than Cortex-M cores with a Von Neumann computer architecture.

- Note: The Cortex-M series includes three new 16-bit Thumb-1 instructions for sleep mode: SEV, WFE, WFI.

- Note: The Cortex-M0 / M0+ / M1 doesn't include these 16-bit Thumb-1 instructions: CBZ, CBNZ, IT.[14][15]

- Note: The Cortex-M0 / M0+ / M1 only include these 32-bit Thumb-2 instructions: BL, DMB, DSB, ISB, MRS, MSR.[14][15]

- Note: The Cortex-M0 / M0+ / M1 / M23 only has 32-bit multiply instructions with a lower-32-bit result (32 bit × 32 bit = lower 32 bit), where as the Cortex-M3 / M4 / M7 / M33 / M35P includes additional 32-bit multiply instructions with 64-bit results (32 bit × 32 bit = 64 bit). The Cortex-M4 / M7 (optionally M33 / M35P) include DSP instructions for (16 bit × 16 bit = 32 bit), (32 bit × 16 bit = upper 32 bit), (32 bit × 32 bit = upper 32 bit) multiplications.[14][15]

- Note: The number of cycles to complete multiply and divide instructions vary across ARM Cortex-M core designs. Some cores have a silicon option for the choice of fast speed or small size (slow speed), so cores have the option of using less silicon with the downside of higher cycle count. An interrupt occurring during the execution of a divide instruction or slow-iterative multiply instruction will cause the processor to abandon the instruction, then restart it after the interrupt returns.

- Multiply instructions "32-bit result" – Cortex-M0/M0+/M23 is 1 or 32 cycle silicon option, Cortex-M1 is 3 or 33 cycle silicon option, Cortex-M3/M4/M7/M33/M35P is 1 cycle.

- Multiply instructions "64-bit result" – Cortex-M3 is 3–5 cycles (depending on values), Cortex-M4/M7/M33/M35P is 1 cycle.

- Divide instructions – Cortex-M3/M4 is 2–12 cycles (depending on values), Cortex-M7 is 3–20 cycles (depending on values), Cortex-M23 is 17 or 34 cycle option, Cortex-M33 is 2–11 cycles (depending on values), Cortex-M35P is TBD.

- Note: Some Cortex-M cores have silicon options for various types of floating point units (FPU). The Cortex-M55 / M85 has an option for half-precision (HP), the Cortex-M4 / M7 / M33 / M35P / M52 / M55 / M85 has an option for single-precision (SP), the Cortex-M7 / M52 / M55 / M85 has an option for double-precision (DP). When an FPU is included, the core is sometimes referred as "Cortex-MxF", where 'x' is the core variant, such as Cortex-M4F.[14][15]

| Group | Instr bits |

Instructions | Cortex M0, M0+, M1 |

Cortex M3 |

Cortex M4 |

Cortex M7 |

Cortex M23 |

Cortex M33 |

Cortex M35P |

Cortex M52 |

Cortex M55 |

Cortex M85 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Thumb-1 | 16 | ADC, ADD, ADR, AND, ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSB, LDRSH, LSL, LSR, MOV, MUL, MVN, NOP, ORR, POP, PUSH, REV, REV16, REVSH, ROR, RSB, SBC, SEV, STM, STR, STRB, STRH, SUB, SVC, SXTB, SXTH, TST, UXTB, UXTH, WFE, WFI, YIELD | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-1 | 16 | CBNZ, CBZ | No | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-1 | 16 | IT | No | Yes | Yes | Yes | No | Yes | Yes | Yes | Yes | Yes |

| Thumb-2 | 32 | BL, DMB, DSB, ISB, MRS, MSR | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-2 | 32 | SDIV, UDIV, MOVT, MOVW, B.W, LDREX, LDREXB, LDREXH, STREX, STREXB, STREXH | No | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Thumb-2 | 32 | ADC, ADD, ADR, AND, ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ, CMN, CMP, DBG, EOR, LDC, LDM, LDR, LDRB, LDRBT, LDRD, LDRH, LDRHT, LDRSB, LDRSBT, LDRSH, LDRSHT, LDRT, LSL, LSR, MCR, MCRR, MLA, MLS, MRC, MRRC, MUL, MVN, NOP, ORN, ORR, PLD, PLDW, PLI, POP, PUSH, RBIT, REV, REV16, REVSH, ROR, RRX, RSB, SBC, SBFX, SEV, SMLAL, SMULL, SSAT, STC, STM, STR, STRB, STRBT, STRD, STRH, STRHT, STRT, SUB, SXTB, SXTH, TBB, TBH, TEQ, TST, UBFX, UMLAL, UMULL, USAT, UXTB, UXTH, WFE, WFI, YIELD | No | Yes | Yes | Yes | No | Yes | Yes | Yes | Yes | Yes |

| DSP | 32 | PKH, QADD, QADD16, QADD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB16, QSUB8, SADD16, SADD8, SASX, SEL, SHADD16, SHADD8, SHASX, SHSAX, SHSUB16, SHSUB8, SMLABB, SMLABT, SMLATB, SMLATT, SMLAD, SMLALBB, SMLALBT, SMLALTB, SMLALTT, SMLALD, SMLAWB, SMLAWT, SMLSD, SMLSLD, SMMLA, SMMLS, SMMUL, SMUAD, SMULBB, SMULBT, SMULTT, SMULTB, SMULWT, SMULWB, SMUSD, SSAT16, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHADD8, UHASX, UHSAX, UHSUB16, UHSUB8, UMAAL, UQADD16, UQADD8, UQASX, UQSAX, UQSUB16, UQSUB8, USAD8, USADA8, USAT16, USAX, USUB16, USUB8, UXTAB, UXTAB16, UXTAH, UXTB16 | No | No | Yes | Yes | No | Optional | Optional | Yes | Yes | Yes |

| SP Float | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMSR, VMUL, VNEG, VNMLA, VNMLS, VNMUL, VPOP, VPUSH, VSQRT, VSTM, VSTR, VSUB | No | No | Optional | Optional | No | Optional | Optional | Optional | Optional | Optional |

| DP Float | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | No | No | No | Optional | No | No | No | Optional | Optional | Optional |

| Acquire/Release | 32 | LDA, LDAB, LDAH, LDAEX, LDAEXB, LDAEXH, STL, STLB, STLH, STLEX, STLEXB, STLEXH | No | No | No | No | Yes | Yes | Yes | Yes | Yes | Yes |

| TrustZone | 16 | BLXNS, BXNS | No | No | No | No | Optional | Optional | Optional | Optional | Optional | Yes |

| 32 | SG, TT, TTT, TTA, TTAT | |||||||||||

| Co-processor | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRRC, MRRC2 | No | No | No | No | No | Optional | Optional | Optional | Optional | Optional |

| ACI | 32 | CX1, CX1A, CX2, CX2A, CX3, CX3A, CX1D, CX1DA, CX2D, CX2DA, CX3D, CX3DA, VCX1, VCX1A, VCX2, VCX2A, VCX3, VCX3A | No | No | No | No | No | Optional | No | Optional | Optional | Optional |

| PACBTI | 32 | AUT, AUTG, BTI, BXAUT, PAC, PACBTI, PACG | No | No | No | No | No | No | No | Optional | No | Optional |

- Note: MOVW is an alias that means 32-bit "wide" MOV instruction.

- Note: B.W is a long-distance unconditional branch (similar in encoding, operation, and range to BL, minus setting of the LR register).

- Note: For Cortex-M1, WFE / WFI / SEV instructions exist, but execute as a NOP instruction.

- Note: The half-precision (HP) FPU instructions are valid in the Cortex-M52 / M55 / M85 only when the HP FPU option exists in the silicon.

- Note: The single-precision (SP) FPU instructions are valid in the Cortex-M4 / M7 / M33 / M35P / M52 / M55 / M85 only when the SP FPU option exists in the silicon.

- Note: The double-precision (DP) FPU instructions are valid in the Cortex-M7 / M52 / M55 / M85 only when the DP FPU option exists in the silicon.

Deprecations

[edit]The ARM architecture for ARM Cortex-M series removed some features from older legacy cores:[14][15]

- The 32-bit ARM instruction set is not included in Cortex-M cores.

- Endianness is chosen at silicon implementation in Cortex-M cores. Legacy cores allowed "on-the-fly" changing of the data endian mode.

- Co-processors were not supported on Cortex-M cores, until the silicon option was reintroduced in "ARMv8-M Mainline" for ARM Cortex-M33/M35P cores.

The capabilities of the 32-bit ARM instruction set is duplicated in many ways by the Thumb-1 and Thumb-2 instruction sets, but some ARM features don't have a similar feature:

- The SWP and SWPB (swap) ARM instructions don't have a similar feature in Cortex-M.

The 16-bit Thumb-1 instruction set has evolved over time since it was first released in the legacy ARM7T cores with the ARMv4T architecture. New Thumb-1 instructions were added as each legacy ARMv5 / ARMv6 / ARMv6T2 architectures were released. Some 16-bit Thumb-1 instructions were removed from the Cortex-M cores:

- The "BLX <immediate>" instruction doesn't exist because it was used to switch from Thumb-1 to ARM instruction set. The "BLX <register>" instruction is still available in the Cortex-M.

- SETEND doesn't exist because on-the-fly switching of data endian mode is no longer supported.

- Co-processor instructions were not supported on Cortex-M cores, until the silicon option was reintroduced in "ARMv8-M Mainline" for ARM Cortex-M33/M35P cores.

- The SWI instruction was renamed to SVC, though the instruction binary coding is the same. However, the SVC handler code is different from the SWI handler code, because of changes to the exception models.

Cortex-M0

[edit]| Architecture and classification | |

|---|---|

| Instruction set | ARMv6-M (Thumb-1 (most), Thumb-2 (some)) |

The Cortex-M0 core is optimized for small silicon die size and use in the lowest price chips.[2]

Key features of the Cortex-M0 core are:[17]

- ARMv6-M architecture[14]

- 3-stage pipeline

- Instruction sets:

- Thumb-1 (most), missing CBZ, CBNZ, IT

- Thumb-2 (some), only BL, DMB, DSB, ISB, MRS, MSR

- 32-bit hardware integer multiply with 32-bit result

- 1 to 32 interrupts, plus NMI

Silicon options:

- Аппаратное целочисленное множество скорости: 1 или 32 цикла.

Чипсы

[ редактировать ]

Следующие микроконтроллеры основаны на ядре Cortex-M0:

- ABOV AC30M1X64

- Cypress PSOC 4000, 4100, 4100 м, 4200, 4200ds, 4200L, 4200M

- Infineon XMC1100 , XMC1200, XMC1300, XMC1400, TLE984X

- Диалог DA1458X, DA1468X

- Северный NRF51

- NXP LPC1100 , LPC1200

- Nuvoton Numicro

- Sonix SN32F700

- ST STM32 F0

- Toshiba TX00

- Vorago VA10800 (экстремальная температура), VA10820 (излучение излучения)

Следующие фишки имеют кору-мг в качестве вторичного ядра:

- NXP LPC4300 (одна Cortex-M4F + One Cortex-M0)

- Texas Instruments SimpleLink Wireless MCUS CC1310 и CC2650 (одна программируемая сетевая процессор Cortex-M3 + One Cortex-M0 + один проприетарный двигатель контроллера датчика)

Cortex-M0+

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV6-M |

| Набор инструкций | Thumb-1 (большинство) , Thumb-2 (некоторые) |

Cortex-M0+ является оптимизированным суперсетом Cortex-M0. Cortex-M0+ имеет полную совместимость набора инструкций с Cortex-M0, что позволяет использовать те же инструменты компилятора и отладки. Конвейер Cortex-M0+ был уменьшен с 3 до 2 этапов, что снижает использование мощности и повышает производительность (более высокий средний IPC из-за ветвей, занимающих меньше цикла). В дополнение к функциям отладки в существующей Cortex-M0, в кремниевую опцию может быть добавлена в Cortex-M0+, называемый буфером Micro Trace (MTB), который обеспечивает простой буфер с трассировкой инструкции. Cortex-M0+ также получила функции Cortex-M3 и Cortex-M4, которые могут быть добавлены в виде опций кремния, таких как блок защиты памяти (MPU) и перемещение векторной таблицы. [ 18 ]

Ключевые особенности Cortex-M0+ Core: [ 18 ]

- Архитектура ARMV6-M [ 14 ]

- 2-стадный трубопровод (на один меньше, чем кора-мг)

- Наборы инструкций: (так же, как Cortex-M0)

- Thumb-1 (большинство), отсутствующий CBZ, CBNZ, IT

- Thumb-2 (некоторые), только BL, DMB, DSB, ISB, MRS, MSR

- 32-разрядное аппаратное целое число умножается с 32-разрядным результатом

- От 1 до 32 прерываний плюс NMI

Силиконовые варианты:

- Аппаратное целочисленное множественная скорость: 1 или 32 цикла

- 8-регионский блок защиты памяти (MPU) (так же, как M3 и M4)

- Перемещение векторной таблицы (так же, как M3, M4)

- Одноциклевый порт ввода/вывода (доступен в M0+/M23)

- Micro Trace Buffer (MTB) (доступен в M0+/M23/M33/M35P)

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M0+:

- ABOV Semiconductor A31G11X, A31G12X, A31G314

- Cypress PSOC 4000S, 4100S, 4100S+, 4100PS, 4700S, FM0+

- Epson S1C31W74, S1C31D01, S1C31D50

- Holtek HT32F52000

- Microchip Sam C2, D0, D1, D2, DA, L2, R2, R3; и PIC32CM JH и MC [ 31 ]

- NXP LPC800 , LPC11E60, LPC11U60

- NXP ( Freescale ) Kinetis E, EA, L, M, V1, W0, S32K11X

- Raspberry Pi RP2040 (два ядра M0+)

- Renesas S124, S128, Re, RE01

- Силиконовые лаборатории ( Energy Micro ) EFM32 Zero, Happy

- ST STM32 L0 , G0 , C0 , WL (одна кора-M4 + одна кора-мг +)

Следующие фишки имеют кору-мг+ как вторичное ядро:

Наименьшие микроконтроллеры ARM имеют тип Cortex-M0+ (по состоянию на 2014 год, наименьший при 1,6 мм на 2 мм в упаковке SIP-масштаба Kinetis KL03). [ 32 ]

21 июня 2018 года было объявлено « Самый маленький компьютер» в мире »или компьютерное устройство-на основе ARM Cortex-M0+ (а также в том числе RAM и беспроводные передатчики и приемники на основе фотоэлектрических исследователей )-исследователей Университета Мичигана на симпозии 2018 Технология и схемы VLSI с бумагой «0,04 мм 3 16NW Беспроводная и без батарея система сенсорной системы со встроенной процессором Cortex-M0+ и оптической связи для измерения температуры сотовой связи ». Устройство на одну десятую размера ранее претендуемого компьютера IBM в мировом рекорде с месяцами назад, что меньше, чем, чем меньше, чем чем зерно соли.

Кора-м1

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV6-M |

| Набор инструкций | Thumb-1 (большинство) , Thumb-2 (некоторые) |

Cortex-M1 является оптимизированным ядром, специально предназначенным для загрузки в чипы FPGA . [ 4 ]

Ключевые особенности ядра Cortex-M1: [ 19 ]

- Архитектура ARMV6-M [ 14 ]

- 3-ступенчатый трубопровод .

- Наборы инструкций:

- Thumb-1 (большинство), отсутствующий CBZ, CBNZ, IT.

- Thumb-2 (некоторые), только BL, DMB, DSB, ISB, MRS, MSR.

- 32-разрядное аппаратное целое число умножается с 32-разрядным результатом.

- От 1 до 32 прерываний плюс NMI .

Силиконовые варианты:

- Аппаратное целочисленное множество скорости: 3 или 33 цикла.

- Дополнительная плотно связанная память (TCM): от 0 до 1 МБ

- Внешние прерывания: 0, 1, 8, 16, 32.

- Отладка: нет, не уменьшен, полная.

- Данные эндианство: маленький или Be-8 Big-Endian.

- Расширение ОС: настоящее или отсутствует.

Чипсы

[ редактировать ]Следующие поставщики поддерживают Cortex-M1 в качестве мягких ядер на своих чипах FPGA:

- Altera Cyclone-II, Cyclone-III, Stratix-II, Stratix-III

- Говин М1 [ 33 ]

- Actel / Microsemi / Microchip Fusion, Igloo / E, Proasic3L, Proasic3 / E

- Xilinx Spartan-3, Virtex-2, Virtex-3, Virtex-4, Artix-7 [ 34 ]

Кора-м3

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV7-M |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенные (некоторые), разделите |

Ключевые особенности Cortex-M3 Core: [ 20 ] [ 35 ]

- Архитектура ARMV7-M [ 15 ]

- 3-стабильный трубопровод с спекуляциями ветвей .

- Наборы инструкций:

- Thumb-1 (целый).

- Thumb-2 (весь).

- 32-разрядное аппаратное целое число умножается с 32-разрядным или 64-битным результатом, подписанным или без знака, добавить или вычесть после умножения. 32-разрядная умножение составляет 1 цикл, но 64-разрядные инструкции Multiply и MAC требуют дополнительных циклов.

- 32-битное аппаратное разрыв (2–12 циклов).

- арифметическая поддержка насыщения.

- От 1 до 240 прерываний плюс NMI .

- 12 Цикла -задержка прерывания.

- Интегрированные режимы сна.

Силиконовые варианты:

- Необязательный блок защиты памяти (MPU): 0 или 8 областей.

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M3:

- ABOV AC33MX128, AC33MX064

- Actel / Microsemi / Microchip Smartfusion, SmartFusion 2 (FPGA)

- Аналоговые устройства ADUCM360, ADUCM361, ADUCM3029

- Broadcom Wi-Fi Chip BCM4319XKUBG

- Cypress PSOC 5000, 5000LP, FM3

- Holtek ht32f

- Infineon TLE9860, TLE987X

- Microchip (Atmel) Sam 3a, 3n, 3s, 3u, 3x

- NXP LPC1300 , LPC1700 , LPC1800

- На Q32M210

- Realtek RTL8710

- Силиконовые лаборатории Precision32

- Кремниевые лаборатории ( Energy Micro ) EFM32 Tiny, Gecko, Leopard, Giant

- ST STM32 F1, F2, L1, W

- TDK-MICRONAS HVC4223F

- Texas Instruments F28, LM3, TMS470, OMAP 4 , беспроводные MCU SimpleLink (CC1310 Sub-GHZ и CC2650 BLE + Zigbee + 6lowpan )

- Toshiba TX03

- MindMotion MindMotion MM32

Следующие фишки имеют кору-м3 в качестве вторичного ядра:

- Apple A9 (Cortex-M3 в качестве интегрированного M9 Motion Co-Processor )

- CSR Four 5300 (Cortex-M3 в качестве соавтора)

- Samsung Exynos 7420 (Cortex-M3 в качестве микроконтроллера DVS ) [ 36 ]

- Texas Instruments F28, LM3, TMS470, OMAP 4470 (одна Cortex-A9 + Two Cortex-M3)

- Xs1 -xa (семь xcoore + me courtx -m3)

Следующие FPGA включают ядро Cortex-M3:

- Microsemi SmartFusion2 Soc

Следующие поставщики поддерживают Cortex-M3 в качестве мягких ядер на своих чипах FPGA:

- Altera Cyclone-II, Cyclone-III, Stratix-II, Stratix-III

- Xilinx Spartan-3, Virtex-2, Virtex-3, Virtex-4, Artix-7 [ 37 ]

Кора-м4

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | Armv7e-m |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделите, FPU (SP) |

Концептуально Cortex-M4 представляет собой инструкции Cortex-M3 Plus DSP и необязательный блок с плавающей точкой (FPU). Ядро с FPU известно как Cortex-M4F.

Ключевые особенности Cortex-M4 Core: [ 21 ]

- Архитектура ARMV7E-M [ 15 ]

- 3-стабильный трубопровод с спекуляциями ветвей .

- Наборы инструкций:

- Thumb-1 (целый).

- Thumb-2 (весь).

- 32-разрядное аппаратное целое число умножается с 32-разрядным или 64-битным результатом, подписанным или без знака, добавить или вычесть после умножения. 32-битный умножение и Mac-1 цикл.

- 32-битное аппаратное разрыв (2–12 циклов).

- Арифметическая поддержка насыщения.

- Расширение DSP: один цикл 16/32-битный Mac , одно цикл двойной 16-битный Mac, 8/16-битный SIMD- арифметика.

- От 1 до 240 прерываний плюс NMI .

- 12 Цикла -задержка прерывания.

- Интегрированные режимы сна.

Силиконовые варианты:

- Необязательный блок с плавающей запятой (FPU): только однооперационное соответствие IEEE-754 . Это называется расширением FPV4-SP.

- Необязательный блок защиты памяти (MPU): 0 или 8 областей.

Чипсы

[ редактировать ]

Следующие микроконтроллеры основаны на ядре Cortex-M4:

- Аналоговые устройства ADSP-CM40X

- Microchip (Atmel) Sam 4l, 4n, 4s

- NXP ( Freescale ) Kinetis K, W2

- ST ( STM32 ) WL (одна кора-м4 + одна кора-мг +)

- Texas Instruments SimpleLink Wi-Fi CC32XX, CC32XXMOD

Следующие микроконтроллеры основаны на ядре Cortex-M4F (M4 + FPU ):

- Аналоговые устройства ADUCM4050

- Cypress 6200 (одна Cortex-M4F + One Cortex-M0 +), FM4

- Наконец XMC4000

- Максим Дарвин

- Microchip (Atmel) Sam4c (двойная ядра: одна кора Cortex-M4F + One Cortex-M4), SAM4E, SAM4L, SAM4N, SAM4S, SAMG5, SAMD5/E5X

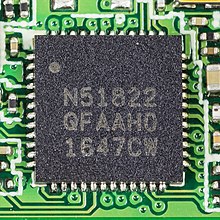

- Северный NRF52

- Numicoton Numicro M480

- NXP LPC4000 , LPC4300 (одна Cortex-M4F + One Cortex-M0), LPC54000

- NXP ( Freescale ) Kinetis K, V3, V4, S32K14X

- Renesas S3, S5, S7, RA4, RA6

- Силиконовые лаборатории ( Energy Micro ) EFM32 Wonder

- ST STM32 F3, F4, L4, L4+, G4, WB (одна Cortex-M4F+One Cortex-M0+)

- Texas Instruments LM4F, TM4C, MSP432 , CC13X2R, CC1352P, CC26X2RR

- Toshiba TX04

Следующие фишки имеют либо кору-М4, либо M4F в качестве вторичного ядра:

- Nxp ( freescale ) vybrid vf6 (одна Cortex-A5 + One Cortex-M4F)

- Nxp ( freescale ) i.mx 6 Solox (одна кора-A9 + одна кора-м4ф)

- Nxp ( freescale ) i.mx 7 Solo/Dual (одна или две Cortex-A7 + One Cortex-M4F)

- Nxp ( freescale ) i.mx 8 (две Cortex-A72 + Четыре Cortex-A53 + Two Cortex-M4F)

- Nxp ( freescale ) i.mx 8m и 8m mini (четыре коры-A53 + One Cortex-M4F)

- Nxp ( freescale ) i.mx 8x (четыре коры-A35 + One Cortex-M4F)

- ST STM32MP1 (одна или две Cortex-A7 + One Cortex-M4)

- Texas Instruments OMAP 5 (две Cortex-A15S + Two Cortex-M4)

- Texas Instruments Sitara AM5700 (одна или две коры Cortex-A15S + две коры-м4 в качестве единиц обработки изображений + две коры-м4 в качестве единиц общего назначения)

Кора-м7

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | Armv7e-m |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделение, FPU (SP & DP) |

Cortex-M7 представляет собой высокопроизводительное ядро почти вдвое превышает эффективность мощности более старой Cortex-M4. [ 7 ] Он оснащен 6-ступенчатым суперкаларным трубопроводом с прогнозированием ветвей и дополнительным блоком с плавающей точкой, способным к однооценке и опционально двойным операциям. [ 7 ] [ 38 ] Шины инструкций и данных были увеличены до 64-разрядной ширины по сравнению с предыдущими 32-разрядными шинами. Если ядро содержит FPU, оно известно как кора-M7F, в противном случае это кора-M7.

Ключевые особенности Cortex-M7 Core: [ 22 ]

- Архитектура ARMV7E-M.

- 6-стабильный трубопровод с спекуляциями ветвей . Второе место из всех сердечников Arm Cortex-M, первым из которых является Cortex-M85.

- Наборы инструкций:

- Thumb-1 (целый).

- Thumb-2 (весь).

- 32-разрядное аппаратное целое число умножается с 32-разрядным или 64-битным результатом, подписанным или без знака, добавить или вычесть после умножения. 32-битный умножение и Mac-1 цикл.

- 32-битное аппаратное разрыв (2–12 циклов).

- Арифметическая поддержка насыщения.

- Расширение DSP: один цикл 16/32-битный Mac , одно цикл двойной 16-битный Mac, 8/16-битный SIMD- арифметика.

- От 1 до 240 прерываний плюс NMI .

- 12 Цикла -задержка прерывания.

- Интегрированные режимы сна.

Силиконовые варианты:

- Необязательный блок с плавающей точкой (FPU): (единственная точность) или (одиночная и двойная задача), оба AEEE-754-2008. Это называется расширением FPV5.

- Необязательный кэш ЦП : от 0 до 64 КБ, с 0 до 64 КБ, каждый с дополнительным ECC .

- Дополнительная плотно связанная память (TCM): от 0 до 16 МБ

- Необязательный блок защиты памяти (MPU): 8 или 16 областей.

- Необязательный встроенный трассировка макроселла (ETM): только для инструкции или инструкции и данные.

- Необязательный режим удержания (с набором управления питание ARM) для режимов сна.

- Необязательная операция с двойным восстановлением блокировки .

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M7:

Кора-м23

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8-M BASELINE |

| Набор инструкций | Thumb-1 (большинство) , Thumb-2 (некоторые) , Разделите, доверие |

Cortex-M23 Core было объявлено в октябре 2016 года [ 39 ] и на основе архитектуры ARMV8-M , которая ранее была объявлена в ноябре 2015 года. [ 40 ] Концептуально Cortex-M23 похож на инструкции Cortex-M0+ Plus Integer Divide и функции безопасности доверия, а также имеет двухступенчатый конвейер инструкций . [ 8 ]

Ключевые особенности ядра Cortex-M23: [ 23 ] [ 39 ]

- ARMV8-M Базовая архитектура. [ 30 ]

- 2-стадный трубопровод. (Аналогично коре-мг+)

- доверия . Инструкции по безопасности

- 32-разрядное аппаратное разрыв (17 или 34 циклов). (Медленнее, чем разделите во всех других ядрах)

- Границы ограничения стека. (Доступно только с опцией SAU)

Силиконовые варианты:

- Аппаратное целочисленное множество скорости: 1 или 32 цикла.

- Аппаратное целочисленное разделение скорости: 17 или 34 циклов максимум. В зависимости от делителя, инструкция может завершить за счет меньшего количества циклов.

- Необязательный блок защиты памяти (MPU): 0, 4, 8, 12, 16 регионов.

- Необязательный блок атрибуции безопасности (SAU): 0, 4, 8 регионов.

- Одноциклевый порт ввода/вывода (доступен в M0+/M23).

- Micro Trace Buffer (MTB)

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M23:

- Gigadevice GD32E2XX

- Microchip Sam L10, L11 и PIC 32CM-LE 32CM-LS

- Nuvoton M23XX Family, M2XX Family, NUC1262, M2L31

- Renesas S1JA, RA2A1, RA2L1, RA2E1, RA2E2

Cortex-M33

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8-M Mainline |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделить, fpu (sp), Trustzone , соавтор |

Cortex-M33 Core было объявлено в октябре 2016 года [ 39 ] и на основе архитектуры ARMV8-M , которая ранее была объявлена в ноябре 2015 года. [ 40 ] Концептуально Cortex-M33 похож на крест Cortex-M4 и Cortex-M23, а также имеет 3-ступенчатый конвейер инструкций . [ 9 ]

Ключевые особенности ядра Cortex-M33: [ 24 ] [ 39 ]

- ARMV8-M Mainline Architecture. [ 30 ]

- 3-ступенчатый трубопровод.

- доверия . Инструкции по безопасности

- 32-разрядное аппаратное разрыв (максимум 11 циклов).

- Границы ограничения стека. (Доступно только с опцией SAU)

Силиконовые варианты:

- Необязательный блок с плавающей запятой (FPU): только однооперационное соответствие IEEE-754 . Это называется расширением FPV5.

- Необязательный блок защиты памяти (MPU): 0, 4, 8, 12, 16 регионов.

- Необязательный блок атрибуции безопасности (SAU): 0, 4, 8 регионов.

- Micro Trace Buffer (MTB)

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M33:

- Аналоговые устройства ADUCM4

- Диалог DA1469X

- Gigadevice GD32E5, GD32W5

- Nordic NRF91, NRF5340, NRF54

- NXP LPC5500, I.MX RT600, MCX N94X/54X (Dual Core)

- На RSL15

- RENESAS RA4, RA6

- ST STM32 H5, L5, U5, WBA

- Silicon Labs беспроводная серия Gecko Series 2

- Raspberry Pi RP2350

Следующие фишки имеют кору-М33 или M33F в качестве вторичного ядра:

Cortex-M35p

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8-M Mainline |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделить, fpu (sp), Trustzone , соавтор |

Ядро Cortex-M35P было объявлено в мае 2018 года и на основе архитектуры ARMV8-M . Это концептуально ядро Cortex-M33 с новым кэшем инструкций, а также новые устойчивые к фирменным аппаратным концепциям, заимствованные в семействе ARM Securcore, и настраиваемые функции и функции ECC. [ 10 ]

В настоящее время информация о Cortex-M35P ограничена, потому что ее техническое справочное руководство и общее руководство пользователя еще не было выпущено.

Чипсы

[ редактировать ]Следующие микроконтроллеры основаны на ядре Cortex-M35p:

- Stmicroelectronics ST33K

Кора-М52

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8.1-M Mainline Helium |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделить, FPU (VFPV5), Trustzone , Coprocessor, MVE |

Ядро Cortex-M52 было объявлено в ноябре 2023 года и основано на архитектуре ARMV8.1-M . Он имеет 4 -ступенчатый трубопровод. [ 11 ]

Ключевые особенности ядра Cortex-M52 включают:

- ARMV8.1-M Mainline/Гелийская архитектура. [ 30 ]

- 4-ступенчатый трубопровод.

- Границы ограничения стека (доступны только с опцией SAU).

Силиконовые варианты:

- Гелий (M-профиль векторный расширение, MVE)

- С плавающей точкой с одной рецепцией и двойной рецепцией

- Поддержка расширения цифровой обработки сигналов (DSP)

- доверия Поддержка продления безопасности

- Поддержка безопасности и надежности (RAS)

- Поддержка совместного

- Безопасные и небезопасные MPU с 0, 4, 8, 12 или 16 регионами

- Сау с 0, 4 или 8 регионами

- Кэш инструкций с размером до 64 кб

- Кэш данных с размером до 64 кб

- ECC на кэшах и TCMS

- 1–480 прерывания

- 3–8 приоритетных битов исключения

- Внутренние и внешние параметры WIC, необязательные CTI, ITM и DWT

- АРМАНСКИЕ ИНСТРУКЦИИ

Чипсы

[ редактировать ]- По состоянию на декабрь 2023 года чипы не было объявлено.

Cortex-M55

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8.1-M Mainline Helium |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделить, FPU (VFPV5), Trustzone , Coprocessor, MVE |

Ядро Cortex-M55 было объявлено в феврале 2020 года и на основе архитектуры ARMV8.1-M . Он имеет 4 или 5 -ступенчатый трубопровод. [ 12 ]

Ключевые особенности ядра Cortex-M55 включают в себя:

- ARMV8.1-M Mainline/Гелийская архитектура. [ 30 ]

- 4-ступенчатый трубопровод.

- Границы ограничения стека (доступны только с опцией SAU).

Силиконовые варианты:

- Гелий (M-профиль векторный расширение, MVE)

- С плавающей точкой с одной рецепцией и двойной рецепцией

- Поддержка расширения цифровой обработки сигналов (DSP)

- доверия Поддержка продления безопасности

- Поддержка безопасности и надежности (RAS)

- Поддержка совместного

- Безопасные и небезопасные MPU с 0, 4, 8, 12 или 16 регионами

- Сау с 0, 4 или 8 регионами

- Кэш инструкции с размером 4 КБ, 8 КБ, 16 КБ, 32 КБ, 64 КБ

- Кэш данных с размером 4 КБ, 8 КБ, 16 КБ, 32 КБ, 64 КБ

- ECC на кэшах и TCMS

- 1–480 прерывания

- 3–8 приоритетных битов исключения

- Внутренние и внешние параметры WIC, необязательные CTI, ITM и DWT

- АРМАНСКИЕ ИНСТРУКЦИИ

Чипсы

[ редактировать ]- Семьи полупроводникового ансамбля ALIF предлагают однократные или двойные ядра коры-M55, каждая из которых в сочетании с NTOS-U55 NPU

- Infineon Psoc Edge

Cortex-M85

[ редактировать ]| Архитектура и классификация | |

|---|---|

| Микроархитектура | ARMV8.1-M Mainline Helium |

| Набор инструкций | Thumb-1 , Thumb-2 , Насыщенный , DSP , Разделить, FPU (VFPV5), Trustzone , Coprocessor, MVE |

Ядро Cortex-M85 было объявлено в апреле 2022 года и основано на архитектуре ARMV8.1-M . Он имеет 7-ступенчатый трубопровод. [ 13 ]

Силиконовые варианты:

- Необязательный кэш ЦП : от 0 до 64 КБ, с 0 до 64 КБ, каждый с дополнительным ECC .

- Дополнительная плотно связанная память (TCM): от 0 до 16 МБ

- Необязательный блок защиты памяти (MPU): 16 регионов. Могут иметь отдельные для безопасного и небезопасного режима, если rustzone . внедрент

- До 480 прерываний и NMI

- 3–8 приоритетных битов исключения

- Необязательная операция с двойным восстановлением блокировки .

Чипсы

[ редактировать ]- RENEAS RA8

Инструменты разработки

[ редактировать ]Документация

[ редактировать ]Документация для чипсов Arm является обширной. В прошлом 8-битная документация по микроконтроллеру, как правило, вписывалась в один документ, но по мере развития микроконтроллеров, поэтому необходимо их поддержать все. Пакет документов для чипов ARM обычно состоит из коллекции документов от производителя IC, а также поставщика CPU Core ( ARM Limited ).

Типичное дерево документации сверху вниз:

- Дерево документации (сверху вниз)

- Веб -сайт производителя IC.

- ИС производитель маркетинговых слайдов.

- Производитель IC DataSheet для точного физического чипа.

- Справочное руководство по производителю IC, которое описывает общие периферийные устройства и аспекты физического семейства чипов.

- Arm Core сайт.

- Руководство пользователя Arm Core Generic.

- ARM CORE TECHNAL REDURNECTIENT.

- Руководство по архитектуре ARM.

Производители IC имеют дополнительные документы, такие как: Руководство пользователя оценки, примечания к применению, руководства по началу работы, документы библиотеки программного обеспечения, ошибки и многое другое. См. Раздел внешних ссылок для ссылок на официальные документы ARM.

Смотрите также

[ редактировать ]- Архитектура рук

- Список архитектур и ядер рук

- Прерывать , обработчик прерываний

- Операционная система в реальном времени , сравнение операционных систем в реальном времени

Ссылки

[ редактировать ]- ^ Arm Cortex-M Веб-сайт; Arm Limited.

- ^ Jump up to: а беременный «Дом коры-м0» . Arm Limited .

- ^ "Cortex-M0+ дом" . Arm Limited .

- ^ Jump up to: а беременный "Кора-м1 дом" . Arm Limited .

- ^ "Кора-м3 дома" . Arm Limited .

- ^ "Кора-м4 дом" . Arm Limited .

- ^ Jump up to: а беременный в "Кора-м7 дом" . Arm Limited .

- ^ Jump up to: а беременный "Кора-м23 дома" . Arm Limited .

- ^ Jump up to: а беременный «Кора-м33 дома» . Arm Limited .

- ^ Jump up to: а беременный в "Cortex-M35p Home" . Arm Limited .

- ^ Jump up to: а беременный "Кора-м52 дом" . Arm Limited .

- ^ Jump up to: а беременный "Кора-м55 дом" . Arm Limited .

- ^ Jump up to: а беременный "Кора-м85 дом" . Arm Limited .

- ^ Jump up to: а беременный в дюймовый и фон глин час я Дж k л м не а п Q. ведущий «Руководство по архитектуре ARMV6-M» . Arm Limited .

- ^ Jump up to: а беременный в дюймовый и фон глин час я Дж k л м не а п Q. ведущий «Руководство по справочной архитектуре ARMV7-M» . Arm Limited .

- ^ Jump up to: а беременный в дюймовый Cortex-M3 встроенная разработка программного обеспечения; Приложение примечание 179; Arm Limited.

- ^ Jump up to: а беременный в «Техническое руководство по техническому справочнику Cortex-M0» . Arm Limited .

- ^ Jump up to: а беременный в дюймовый "Cortex-M0+ техническое справочное руководство" . Arm Limited .

- ^ Jump up to: а беременный в "Техническое справочное руководство Cortex-M1" . Arm Limited .

- ^ Jump up to: а беременный в «Техническое руководство по коре-м3» . Arm Limited .

- ^ Jump up to: а беременный в «Техническое руководство по техническому справочнику Cortex-M4» . Arm Limited .

- ^ Jump up to: а беременный в дюймовый «Техническое справочное руководство Cortex-M7» . Arm Limited .

- ^ Jump up to: а беременный в «Техническое руководство Cortex-M23» . Arm Limited .

- ^ Jump up to: а беременный в «Техническое руководство по контролю Cortex-M33» . Arm Limited .

- ^ Jump up to: а беременный «Техническое справочное руководство Cortex-M52» . Arm Limited .

- ^ Jump up to: а беременный «Техническое справочное руководство Cortex-M55» . Arm Limited .

- ^ Jump up to: а беременный «Техническое справочное руководство Cortex-M85» . Arm Limited .

- ^ Jump up to: а беременный в «Комплект Cortex-M System Design Kit (CMSDK)» . Рукоопании . Архивировано с оригинала 4 марта 2016 года.

- ^ Jump up to: а беременный в дюймовый и фон глин час я Дж Руководство по программированию ARM Cortex-M к инструкциям по барьеру памяти; Раздел 3.6 Требования к реализации системы; Приложение 321; Arm Limited.

- ^ Jump up to: а беременный в дюймовый и фон глин час я Дж k л «Руководство по архитектуре ARMV8-M» . Arm Limited .

- ^ 32-битный рис и микроконтроллеры SAM; Микрочип.

- ^ Фингас, Джон (25 февраля 2014 г.). «Freescale делает самый маленький в мире чип контроллера Arm еще более крошечным» . Получено 2 октября 2014 года .

- ^ Gowin Semiconductor объединяет Arm Designstart, предлагая бесплатные процессоры Arm Cortex-M1 для своих семейств продуктов FPGA

- ^ Cortex-M1 Designstart FPGA Xilinxedition; Arm Limited.

- ^ Садасиван, Шьям. «Введение в процессор Arm Cortex-M3» (PDF) . Arm Limited. Архивировано из оригинала (PDF) 26 июля 2014 года.

- ^ «Samsung Exynos 7420 Deep Dive - Внутри современного 14 -нм SOC» . Anandtech . Получено 2015-06-15 .

- ^ Cortex-M3 Designstart fpga xilinxedition

- ^ «Рынок MCU ARM с высокой производительностью Cortex-M7 процессор» . Arm Limited (пресс -релиз). 24 сентября 2014 года.

- ^ Jump up to: а беременный в дюймовый Новые процессоры Arm Cortex-M предлагают следующий отраслевой стандарт для безопасного IoT; Arm Limited; 25 октября 2016 г.

- ^ Jump up to: а беременный Архитектура ARMV8-M упрощает безопасность для интеллектуальных устройств; Arm Limited; 10 ноября 2015 г.

Дальнейшее чтение

[ редактировать ]- Руководство дизайнера по семейству процессоров Cortex-M ; 3 -е изд; Тревор Мартин; 648 страниц; 2022; ISBN 978-0323854948.

- Окончательное руководство по процессорам ARM Cortex-M0 и Cortex-M0+ ; 2 -е изд; Джозеф Иу; 784 страницы; 2015; ISBN 978-0128032770.

- Окончательное руководство по процессорам ARM Cortex-M3 и Cortex-M4 ; 3 -е изд; Джозеф Иу; 864 страницы; 2013; ISBN 978-0124080829 .

- Окончательное руководство по процессорам ARM Cortex-M23 и Cortex-M33 ; 1 -е изд; Джозеф Иу; 928 страниц; 2020; ISBN 978-0128207352 .

- Микроконтроллеры с C: Cortex-M и Heaven ; 1 -е изд; Клаус Элк; 227 страниц; 2023; ISBN 979-8862003437 .

- Встроенные системы с микроконтроллерами ARM Cortex-M на языке сборки и C ; 4 -е изд; Ифенг Чжу; 730 страниц; 2023; ISBN 978-0982692677 .

- Сборка ARM для встроенных применений ; 5 -е изд; Даниэль Льюис; 379 страниц; 2019; ISBN 978-1092542234 .

- Программирование языка сборки: ARM Cortex-M3 ; 1 -е изд; Винсент Махоут; 256 страниц; 2012; ISBN 978-1848213296 .

- Цифровая обработка сигналов и приложения с использованием коры ARM Cortex-M4 ; 1 -е изд; Дональд Рей; 320 страниц; 2015; ISBN 978-1118859049.

- Практические RTO с микроконтроллерами ; 1 -е изд; Брайан Амос; 496 страниц; 2020; ISBN 978-1838826734 .

Внешние ссылки

[ редактировать ]- Официальные документы Arm Cortex-M

- Официальный сайт ARM Cortex-M

- Cortex-m для начинающих arm.com

- ARMV8-M Security Advensions Arm.com

- Cortex Microcontroller Software Interface Standard (CMSIS) ARM.com

РУКА

основнойКусочек

ширинаРУКА

веб -сайтРука общая

Руководство пользователяARM Technical

справочное руководствоАрхитектура рук

справочное руководствоКорка-Мст 32 Связь Связь Связь ARMV6-M Cortex-M0+ 32 Связь Связь Связь ARMV6-M Кора-м1 32 Связь Связь Связь ARMV6-M Кора-м3 32 Связь Связь Связь ARMV7-M Кора-м4 32 Связь Связь Связь Armv7e-m Кора-м7 32 Связь Связь Связь Armv7e-m Кора-м23 32 Связь Связь Связь ARMV8-M Cortex-M33 32 Связь Связь Связь ARMV8-M Cortex-M35p 32 Связь N/a N/a ARMV8-M Кора-М52 32 Связь N/a Связь ARMV8.1-M Cortex-M55 32 Связь Связь Связь ARMV8.1-M Cortex-M85 32 Связь Связь Связь ARMV8.1-M

- Быстрые справочные карты

- Инструкции: THUMP-1 ( 1 ), ARM и THUMP-2 ( 2 ), вектор с плавающей точкой ( 3 ) ARM.com

- ОПКОДЫ: THUMP-1 ( 1 , 2 ), ARM ( 3 , 4 ), Директивы Assembler GNU ( 5 ).

- Мигрируя

- Мигрирование с 8051 в Cortex-M3-Arm.com

- Переход с картины в Cortex-M3-arm.com

- Мигрирование из ARM7TDMI в Cortex-M3-ARM.com

- Мигрирование из коры-м4 в Cortex-M7-keil.com

- Другой