Архитектура клипера

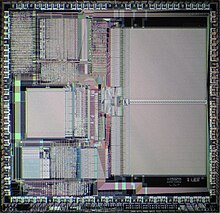

Intergraph Clipper C4 (C400) Процессор | |

| Дизайнер | |

|---|---|

| Биты | 32-битный |

| Представлено | 1986 |

| Дизайн | RISC -подобный |

Архитектура Clipper представляет собой 32-битную RISC -подобную архитектуру набора команд, разработанную Fairchild Semiconductor . Архитектура никогда не пользовалась большим успехом на рынке, и единственными производителями компьютеров , создавшими основные линейки продуктов с использованием процессоров Clipper, были Intergraph и High Level Hardware , хотя Opus Systems предлагала продукт на основе Clipper как часть своей линейки персональных мейнфреймов. [1] Первые процессоры, использующие архитектуру Clipper, были разработаны и проданы компанией Fairchild, но ответственное за них подразделение впоследствии было продано компании Intergraph в 1987 году; Intergraph продолжила работу над процессорами Clipper для использования в своих системах. [2]

В архитектуре Clipper использовался упрощенный набор инструкций по сравнению с более ранними архитектурами CISC , но она включала в себя некоторые более сложные инструкции, чем в других современных RISC-процессорах. Эти инструкции были реализованы в так называемом ПЗУ макроинструкций внутри ЦП Clipper. Эта схема позволила Clipper иметь несколько более высокую плотность кода, чем другие RISC-процессоры.

Версии

[ редактировать ]

Первым микропроцессором Clipper, произведенным Fairchild, был C100, который стал доступен в 1986 году. За ним последовал более быстрый C300 от Intergraph в 1988 году. Последней моделью Clipper стал C400, выпущенный в 1990 году, который был значительно переработан, чтобы стать более быстрым. и добавлено больше регистров с плавающей запятой. Процессор C400 объединил два ключевых архитектурных метода для достижения нового уровня производительности — суперскалярную диспетчеризацию инструкций и суперконвейерную работу.

Хотя многие процессоры того времени использовали либо суперскалярную отправку инструкций, либо суперконвейерную операцию, Clipper C400 был первым процессором, который использовал оба этих метода. [3]

Intergraph начала работу над следующей конструкцией процессора Clipper, известной как C5, но она так и не была завершена и выпущена. Тем не менее, для C5 были разработаны некоторые передовые методы проектирования процессоров, и Intergraph получила патенты на них . Эти патенты, наряду с оригинальными патентами Clipper, легли в основу исков Intergraph о нарушении патентных прав против Intel и других компаний. [4]

В отличие от многих других микропроцессоров, процессоры Clipper фактически представляли собой набор из нескольких отдельных микросхем. C100 и C300 состоят из трёх микросхем: одного центрального процессора, содержащего как целочисленный блок, так и блок с плавающей запятой , а также два кэшем и управления блока памятью (CAMMU), один из которых отвечает за данные, а другой — за инструкции. CAMMU содержали кэши, резервные буферы трансляции и поддержку защиты памяти и виртуальной памяти . C400 состоит из четырех основных блоков: целочисленного процессора, FPU, MMU и блока кэша. В первоначальной версии использовалось по одному чипу для ЦП и FPU, а также дискретные элементы для MMU и блока кэша, но в более поздних версиях MMU и блок кэша были объединены в один чип CAMMU.

Регистры и набор команд

[ редактировать ]Clipper имеет 16 целочисленных регистров (R15 используется в качестве указателя стека), 16 регистров с плавающей запятой (ограничено до 8 в ранних реализациях), а также программный счетчик (PC), слово состояния процессора (PSW), содержащее состояние ALU и FPU. флаги и разрешения ловушек, а также слово состояния системы (SSW), содержащее разрешение внешнего прерывания, режим пользователя/супервизора и биты управления трансляцией адресов.

Режимы пользователя и супервизора имеют отдельные банки целочисленных регистров. Обработка прерываний заключалась в сохранении PC, PSW и SSW в стеке, очистке PSW и загрузке PC и SSW из вектора ловушки памяти.

Clipper — это архитектура загрузки/сохранения , в которой арифметические операции могут указывать только регистр или непосредственные операнды. Базовая инструкция «посылка» имеет 16 бит: 8 бит кода операции, 4 бита регистра источника и 4 бита регистра назначения. Формы с непосредственными операндами позволяют 1 или 2 следующим пакетам инструкций указывать 16-битный (расширенный знаком) или 32-битный непосредственный операнд. Процессор имеет прямой порядок байтов, включая непосредственные операнды.

Специальная «быстрая» кодировка с 4-битным беззнаковым операндом предусмотрена для сложения, вычитания, загрузки (быстрое перемещение для регистрации) и нет (перемещение дополнения для быстрой регистрации).

Режимы адресации для инструкций загрузки/сохранения и перехода следующие. Все смещения являются знакопродолжительными.

- (Rn), d12(Rn), d32(Rn): Относительный регистр со смещением 0, 12 или 32 бита.

- d16(ПК), d32(ПК): относительно ПК

- d16, d32: абсолютный

- [Rx](Rn), [Rx](PC): Регистр или индексация относительно ПК. Индексный регистр не масштабируется.

Помимо обычных логических и арифметических операций процессор поддерживает:

- 32×32→32-битное умножение, деление и остаток (со знаком и без знака)

- 64-битные сдвиги и вращения, работающие с парами четных/нечетных регистров.

- 32×32→64-битное расширенное умножение

- Целочисленный регистр push/pop (сохранение с предварительным декрементом, загрузка с пост-инкрементом)

- Вызов подпрограммы (нажать ПК, переместить адрес операнда на ПК)

- Возврат из подпрограммы (извлечение ПК из стека)

- Атомная загрузка памяти и установка мсбита

- Ловушка супервизора

Более сложные макрокоманды позволяют:

- Нажмите/извлеките несколько целочисленных регистров R n –R14

- Нажмите/извлеките несколько регистров с плавающей запятой D n –D7

- Пользовательские регистры push/pop R0–R15

- Возврат из прерывания (выталкивание SSW, PSW и ПК)

- Инициализировать строку байтов (сохранить копии R0 R2 в памяти, начиная с R1)

- Перемещайте символы и сравнивайте символы (длина в R0, источник в R1, место назначения в R2).

Большинство инструкций позволяют указать произвольный регистр указателя стека, но за исключением сохранения/восстановления пользовательского регистра, операции с несколькими регистрами могут использовать только R15.

Системы Clipper компании Intergraph

[ редактировать ]

Intergraph продала несколько поколений систем Clipper, включая как серверы , так и рабочие станции . Эти системы включали линейки продуктов InterAct, InterServe и InterPro и были ориентированы в основном на рынок САПР .

Fairchild продвигала операционную систему CLIX , версию UNIX System V , для использования с Clipper. Intergraph внедрила CLIX в свои системы на базе Clipper и продолжила его развитие; это была единственная операционная система, доступная для этих систем. Intergraph действительно работала над версией Microsoft Windows NT для систем Clipper и публично продемонстрировала ее, но эта работа была отменена еще до выпуска. [5] Intergraph решила прекратить выпуск линейки Clipper и вместо этого начала продавать системы x86 с Windows NT.

Ссылки

[ редактировать ]- ^ «Opus Systems представляет рабочие станции Unix Series 300» . Компьютерный мир . 4 марта 1987 г. с. 41 . Проверено 23 июня 2022 г.

- ^ Вайсберг, Дэвид (2008). «Революция инженерного дизайна: люди, компании и компьютерные системы, которые навсегда изменили практику проектирования» (PDF) . Глава 14. Архивировано (PDF) из оригинала 4 марта 2016 года . Проверено 26 июня 2016 г.

- ^ Коллекция процессоров. «Интерграф Клипер С4» .

- ^ Флинн, Лори (31 марта 2004 г.). «Intergraph и Intel урегулировали спор о чипах» . Нью-Йорк Таймс . Архивировано из оригинала 19 июня 2015 года . Проверено 26 июня 2016 г.

- ^ Симпсон, Ник (15 января 2000 г.). «Re: Intergraph Interact 340» . Группа новостей : comp.sys.intergraph . Usenet: [электронная почта защищена] .

- Корпорация Fairchild Semiconductor (1987). CLIPPER 32-битный микропроцессор: Руководство пользователя . Прентис-Холл. ISBN 0-13-138058-3 .

- Уолтер Холлингсворт; Говард Сакс; Алан Джей Смит (1989). «Процессор CLIPPER: архитектура и реализация набора команд» . Коммуникации АКМ . 32 (2): 200–219. дои : 10.1145/63342.63346 . S2CID 13239029 .

- Уолтер Холлингсворт; Говард Сакс; Алан Джей Смит (11 февраля 1987 г.). Fairchild CLIPPER: Архитектура набора команд и реализация процессора (PDF) (Технический отчет). УКБ/ЦД. 87/329 . Проверено 22 марта 2011 г.

- Джеймс Чо; Алан Джей Смит; Говард Сакс (апрель 1986 г.). Архитектура памяти и блок управления кэшем и памятью для процессора Fairchild CLIPPER (PDF) (технический отчет). УКБ/ЦД. 86/289 . Проверено 22 марта 2011 г.

- Говард Сакс; Харлан МакГэн; Ли Хэнсон; Натан Бруквуд (1991). «Компромиссы при проектировании и реализации в архитектуре Clipper C400». IEEE микро . 11 (3): 18–21, 74–80. дои : 10.1109/40.87566 . S2CID 8895269 .

- История Интерграфа

- Набор инструкций для 32-битного микропроцессорного модуля Clipper™ (PDF) , Fairchild, октябрь 1985 г. , получено 11 июля 2020 г.

- 32-битный микропроцессор Clipper™: введение в архитектуру CLIPPER (PDF) , Fairchild, май 1986 г. , получено 11 июля 2020 г.

- Техническое описание 32-битного вычислительного процессора Clipper™ C100 (PDF) , Intergraph, декабрь 1987 г. , получено 11 июля 2020 г.