ПА-РИСК

| |

| Дизайнер | Хьюлетт-Паккард |

|---|---|

| Биты | 64-битный (32 → 64) |

| Представлено | 1986 (1996 PA-RISC 2.0) |

| Версия | 2.0 (1996) |

| Дизайн | РИСК |

| Кодирование | Зафиксированный |

| Ветвление | Сравнить и разветвить |

| Порядок байтов | Большой |

| Расширения | Расширения ускорения мультимедиа (MAX), MAX-2 |

| Открыть | Нет |

| Преемник | PA-WideWord → Итаниум [ 1 ] |

| Регистры | |

| общего назначения | 32 |

| Плавающая точка | 32 64-битных (16 64-битных в PA-RISC 1.0) |

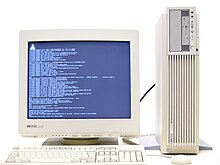

Прецизионная архитектура RISC ( PA-RISC ) или прецизионная архитектура Hewlett Packard ( HP/PA или просто HPPA ) — это компьютерных команд общего назначения архитектура набора (ISA), разработанная Hewlett-Packard с 1980-х по 2000-е годы .

Архитектура была представлена 26 февраля 1986 года, когда HP 3000 Series 930 и HP 9000 Model 840 были выпущены компьютеры с первой реализацией - TS1. [ 2 ] [ 3 ] HP прекратила продажу систем HP 9000 на базе PA-RISC в конце 2008 года, но поддерживала серверы с чипами PA-RISC до 2013 года. [ 4 ] На смену PA-RISC пришла Itanium (первоначально IA-64) ISA, совместно разработанная HP и Intel . [ 5 ]

История

[ редактировать ]В конце 1980-х годов HP производила четыре серии компьютеров, все на базе процессоров CISC . Одной из линий была , совместимая с IBM PC серия Vectra на базе Intel i286 , выпущенная в 1986 году. Все остальные были системами сторонних производителей . HP Series 300 на Motorola 68000 базе Одной из них была рабочая станция , другая линейка технических рабочих станций Series 200, основанная на специальной конструкции чипа кремния на сапфире (SOS), 16-разрядная серия HP 3000 Classic на базе SOS и, наконец, HP 9000 Series 500 Миникомпьютеры на базе собственного (16- и 32-битного) микропроцессора FOCUS .

Precision Architecture — это результат того, что внутри Hewlett-Packard называлось программой Spectrum . [ 6 ] HP планировала использовать Spectrum для перевода всех своих несовместимых с ПК компьютеров на одно семейство процессоров RISC.

В начале 1982 года в лабораториях HP началась работа над прецизионной архитектурой, определявшая набор команд и систему виртуальной памяти. Разработка первой реализации TTL началась в апреле 1983 года. После завершения моделирования процессора в 1983 году окончательная конструкция процессора была передана разработчикам программного обеспечения в июле 1984 года. Затем последовало прототипирование систем, при этом в 1985 году были созданы «лабораторные прототипы» и прототипы продуктов. в 1986 году. [ 7 ]

Первые процессоры были представлены в продуктах в 1986 году. Он имеет тридцать два 32-битных целочисленных регистра и шестнадцать 64-битных регистров с плавающей запятой. Архитектура HP Precision имеет один слот задержки ветвления . Это означает, что инструкция, следующая сразу за инструкцией ветвления, выполняется до того, как поток управления программой будет передан целевой инструкции ветвления. [ 8 ] [ 9 ] Процессор HP Precision также включает в себя регистр слова состояния процессора (PSW). Регистр PSW содержит различные флаги, которые включают виртуальную адресацию, защиту, прерывания и другую информацию о состоянии. [ 10 ] Количество регистров с плавающей запятой было удвоено в версии 1.1 до 32, когда стало очевидно, что 16 неадекватны и ограничивают производительность. В число архитекторов входили Аллен Баум, Ханс Джинс, Майкл Дж. Махон, Руби Бей-Ло Ли , Рассел Као, Стив Мучник , Терренс К. Миллер, Дэвид Фотланд и Уильям С. Уорли. [ 11 ]

Первой реализацией был TS1, центральный процессор, построенный на основе устройств дискретной транзисторно-транзисторной логики ( 74F TTL ). Более поздние реализации представляли собой многокристальные конструкции СБИС, изготовленные по процессам NMOS (NS1 и NS2) и CMOS (CS1 и PCX). [ 12 ] Впервые они были использованы в новой серии машин HP 3000 в конце 1980-х годов — 930 и 950, широко известных в то время как системы Spectrum, название, данное им в лабораториях разработки. Эти машины работали под управлением MPE-XL . Машины HP 9000 вскоре были также оснащены процессором PA-RISC и работали под управлением HP-UX версии UNIX .

Другие операционные системы, перенесенные на архитектуру PA-RISC, включают Linux , OpenBSD , NetBSD , OSF/1 , NeXTSTEP и ChorusOS . [ 13 ]

Интересным аспектом линейки PA-RISC является то, что большинство ее поколений не имеют кэша второго уровня . Вместо этого используются большие кэши первого уровня, первоначально в виде отдельных микросхем, соединенных шиной, а затем интегрированных в кристалл. Только PA-7100LC и PA-7300LC имеют кэш L2. Еще одним нововведением PA-RISC является добавление векторных инструкций ( SIMD ) в форме MAX , которые впервые были представлены на PA-7100LC.

Precision RISC Organization , отраслевая группа под руководством HP, была основана в 1992 году для продвижения архитектуры PA-RISC. В число членов вошли Convex , Hitachi , Hughes Aircraft , Mitsubishi , NEC , OKI , Prime , Stratus , Yokogawa , Red Brick Software и Allegro Consultants, Inc.

В 1996 году ISA была расширена до 64 бит, при этом эта версия получила название PA-RISC 2.0. В PA-RISC 2.0 также добавлены объединенные инструкции умножения-сложения , которые помогают некоторым алгоритмам с интенсивным использованием плавающей запятой, и расширение MAX-2 SIMD, которое предоставляет инструкции для ускорения мультимедийных приложений. Первой реализацией PA-RISC 2.0 был PA-8000 , представленный в январе 1996 года.

Характеристики процессора

[ редактировать ]| Изображение | Модель | Маркетинг имя |

Год | Частота [МГц] |

Шина памяти [МБ/с] |

Процесс [мкм] |

Транзисторы [миллионы] |

Размер матрицы [мм²] |

Власть [В] |

Дкэш [КБ] |

Икэш [КБ] |

Кэш L2 [МБ] |

ОДИН | Примечания |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ТС-1 | ? | 1986 | 8 | ? | ? | — | — | ? | 64 | 64 | — | 1.0 | [ 14 ] | |

| КС-1 | ? | 1987 | 8 | ? | 1.6 | 0.164 | 72.93 | 1 | — | 0.25 | — | 1.0 | [ 15 ] | |

| НС-1 | ? | 1987 | 25/30 | ? | 1.7 | 0.144 | 70.56 | ? | 16-128 | 16-128 | — | 1.0 | [ 14 ] [ 16 ] Единый кэш L1 | |

|

НС-2 | ? | 1989 | 25/30 | ? | 1.5 | 0.183 | 196 | 27 | 512 | 512 | — | 1.0 | [ 17 ] |

| ПКХ | ? | 1990 | 50/60 | ? | 1.0 | 0.196 | ? | ? | ? | ? | ? | 1.0 | [ 14 ] | |

|

PCX-S | ПА-7000 | 1991 | 66 | ? | 1.0 | 0.58 | 201.6 | ? | 256 | 256 | — | 1.1а | |

|

PCX-T | ПА-7100 | 1992 | 33–100 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | — | 1.1б | |

|

PCX-T | ПА-7150 | 1994 | 125 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | — | 1.1б | |

|

PCX-T' | ПА-7200 | 1994 | 120 | 960 | 0.55 | 1.26 | 210 | 30 | 1024 | 2048 | — | 1.1с | |

|

PCX-L | ПА-7100LC | 1994 | 60–100 | ? | 0.75 | 0.9 | 201.6 | 7–11 | — | 1 | 2 | 1.1д | |

|

PCX-L2 | ПА-7300LC | 1996 | 132–180 | ? | 0.5 | 9.2 | 260.1 | ? | 64 | 64 | 0–8 | 1.1е | |

|

PCX-U | ПА-8000 | 1996 | 160–180 | 960 | 0.5 | 3.8 | 337.68 | ? | 1024 | 1024 | — | 2.0 | |

|

PCX-U+ | ПА-8200 | 1997 | 200–240 | 960 | 0.5 | 3.8 | 337.68 | ? | 2048 | 2048 | — | 2.0 | |

|

PCX-W | ПА-8500 | 1998 | 300–440 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | — | 2.0 | [ 18 ] |

|

PCX-W+ | ПА-8600 | 2000 | 360–550 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | — | 2.0 | [ 18 ] |

|

PCX-W2 | ПА-8700 (+) | 2001 | 625–875 | 1920 | 0.18 | 186 | 304 | < [адрес электронной почты защищен] В. | 1536 | 768 | — | 2.0 | |

|

Неделя | ПА-8800 | 2003 | 800–1000 | 6400 | 0.13 | 300 | 361 | ? | 768/ядро | 768/ядро | 0 или 32 | 2.0 | |

|

Короткоплавник | ПА-8900 | 2005 | 800–1100 | 6400 | 0.13 | ? | ? | ? | 768/ядро | 768/ядро | 0 или 64 | 2.0 |

См. также

[ редактировать ]- Набор микросхем Amiga Hombre - набор микросхем на базе PA-7150 с полноценной мультимедийной системой для Commodore Amiga.

- Другие чипы PA-RISC сторонних производителей были созданы Hitachi , Oki и Winbond . [ 19 ]

Ссылки

[ редактировать ]- ^ «Изобретение Itanium: как лаборатории HP помогли создать архитектуру чипов следующего поколения» . Лаборатории HP . 01.06.2001. Архивировано из оригинала 7 февраля 2002 г. Проверено 24 марта 2024 г.

- ^ «Год назад». (26 февраля 1987 г.). Обзор компьютерного бизнеса .

- ^ Розенбладт, Питер (сентябрь 1987 г.). «В этом выпуске» (PDF) . Журнал Hewlett-Packard . 38 (9): 3. Архивировано (PDF) из оригинала 26 апреля 2019 г. Проверено 8 июня 2018 г.

... В мартовском выпуске 1987 года мы описали компьютеры HP 3000 Series 930 и HP 9000 Model 840, которые были первыми реализациями HP Precision Architecture в стандартной технологии TTL. ...

- ^ «Как долго HP будет продолжать поддерживать системы HP 9000?» . Архивировано из оригинала 19 февраля 2012 г. Проверено 29 февраля 2008 г.

- ^ «HP завершает дорожную карту PA-RISC окончательным обновлением процессора» . Архивировано из оригинала 13 февраля 2008 г. Проверено 24 июля 2007 г.

- ^ Уорли, Уильям С. (август 1986 г.). «Прецизионная архитектура Hewlett-Packard: процессор» (PDF) . Журнал Hewlett-Packard . 37 (8): 4–22.

Программа разработки HP Precision Architecture, известная в HP как программа Spectrum,...

- ^ Фотланд, Дэвид А.; Шелтон, Джон Ф.; Бриг, Уильям Р.; Ла Фетра, Росс В.; Бошма, Симин И.; Да, Аллан С.; Джейкобс, Эдвард М. (март 1987 г.). «Аппаратное проектирование первых компьютеров HP с прецизионной архитектурой» . Журнал Hewlett-Packard . 38 (3): 4–17 . Проверено 6 октября 2020 г.

- ^ «Точная архитектура Hewlett-Packard: процессор» (PDF) . п. 10 . Проверено 2 декабря 2023 г.

- ^ ДеРоса, Джон А.; Леви, Генри М. (1987). «Оценка отраслевых архитектур» . Материалы 14-го ежегодного международного симпозиума по архитектуре компьютеров . стр. 10–16. дои : 10.1145/30350.30352 . ISBN 0-8186-0776-9 . Проверено 27 января 2024 г.

- ^ «Прецизионная архитектура Hewlett-Packard: процессор» (PDF) . п. 6 . Проверено 7 декабря 2023 г.

- ↑ Смотерман, Марк (2 июля 2009 г.). Недавние архитекторы процессоров. Архивировано 10 сентября 2012 г. в Wayback Machine .

- ^ Пол Вайсманн. «Ранние системы PA-RISC». Архивировано 2 октября 2014 г. в Wayback Machine .

- ^ Уолпол, Джонатан; Хакансон, Мэрион; Иноуе, Джон; Конуру, Рави (январь 1992 г.). Портирование хора в PA-RISC: обзор проекта (PDF) (отчет). Орегонский аспирантский институт науки и технологий. Архивировано из оригинала 12 июня 2023 года.

- ^ Jump up to: а б с «ПА-РИСК Процессоры»

- ^ Марстон, А.; и др. (1987). «Однокристальный RISC-процессор CMOS 32b». 1987 Международная конференция IEEE по твердотельным схемам. Сборник технических статей . стр. 28–29. дои : 10.1109/ISSCC.1987.1157145 . S2CID 61007482 .

- ^ Йеттер, Дж.; и др. (1987). «Микропроцессор 32b производительностью 15 MIPS». МКССС 1987 . стр. 26–27. дои : 10.1109/ISSCC.1987.1157220 . S2CID 58782915 .

- ^ Бошма, Брайан Д.; и др. (1989). «Процессор VLSI 30 MIPS». Международная конференция IEEE по твердотельным схемам, 1989 г. ISSCC. Сборник технических статей . стр. 82–83, 299. doi : 10.1109/ISSCC.1989.48191 . S2CID 53932361 .

- ^ Jump up to: а б «Серверы HP L1000 и L2000 (rp5400/rp5450)». Архивировано 2 января 2018 г. на Wayback Machine , openpa.net.

- ^ «Процессоры PA-RISC сторонних производителей от Hitachi, Winbond, OKI – OpenPA.net» .

Внешние ссылки

[ редактировать ]- LostCircuits Hewlett Packard PA8800 Обзор RISC-процессора

- Документация HP — страница вниз для PA-RISC, доступны PDF-файлы по архитектуре.

- OpenPA.net Полная информация о чипе PA-RISC и компьютере.

- Chipdb.org Изображения различных процессоров PA-RISC