ДЭК Альфа

Логотип Alpha Generation, используемый Digital | |

| Дизайнер | Корпорация цифрового оборудования |

|---|---|

| Биты | 64-битная |

| Представлено | 1992 год |

| Дизайн | РИСК |

| Тип | Загрузка-сохранение |

| Кодирование | Зафиксированный |

| Порядок байтов | С |

| Расширения | Расширение байтов/слов (BWX), расширение преобразования квадратного корня и чисел с плавающей запятой (FIX), расширение счета (CIX), инструкции видеоизображения (MVI) |

| Открыть | Да [1] |

| Регистры | |

| общего назначения | 31 плюс всегда ноль R31 |

| Плавающая точка | 31 плюс всегда-0,0 F31 |

Alpha (первоначальное название Alpha AXP ) — это 64-битная набора команд компьютера (ISA) архитектура с сокращенным набором команд (RISC), разработанная Digital Equipment Corporation (DEC). Alpha был разработан, чтобы заменить 32-битные VAX компьютеры со сложным набором команд (CISC) и стать высококонкурентным RISC-процессором для рабочих станций Unix и аналогичных рынков.

Alpha реализована в серии микропроцессоров, первоначально разработанных и изготовленных DEC. Эти микропроцессоры наиболее широко используются в различных рабочих станциях и серверах DEC, которые в конечном итоге легли в основу почти всей их линейки среднего и высшего уровня. Несколько сторонних поставщиков также производили системы Alpha, включая материнские платы форм-фактора ПК .

Операционные системы , поддерживающие Alpha, включали OpenVMS (ранее называвшуюся OpenVMS AXP), Tru64 UNIX (ранее называвшуюся DEC OSF/1 AXP и Digital UNIX), Windows NT (прекращение выпуска которой прекращено после NT 4.0 ; и предварительную версию Windows 2000 RC2 ), [2] Linux ( Debian , SUSE , [3] Gentoo и Red Hat ), BSD UNIX ( NetBSD , OpenBSD и FreeBSD до 6.x), Plan 9 от Bell Labs и ядро L4Ka::Pistachio . Порт Ultrix на Alpha был осуществлен во время первоначальной разработки архитектуры Alpha, но так и не был выпущен как продукт. [4]

Архитектура Alpha была продана вместе с большей частью DEC компании Compaq в 1998 году. [5] Compaq, уже являвшаяся клиентом Intel x86, объявила о постепенном отказе от Alpha в пользу будущей архитектуры Hewlett-Packard /Intel Itanium , и продала всю интеллектуальную собственность Alpha компании Intel в 2001 году. [6] эффективно убивая продукт. Hewlett-Packard приобрела Compaq в 2002 году, продолжая развитие существующей линейки продуктов до 2004 года и продавая системы на базе Alpha, в основном существующей клиентской базе, до апреля 2007 года. [7]

История

[ редактировать ]ПРИЗМА

[ редактировать ]Alpha возникла из более раннего проекта RISC под названием Parallel Reduced Instruction Set Machine ( PRISM ), который сам по себе является продуктом нескольких более ранних проектов. PRISM задумывался как гибкая конструкция, поддерживающая Unix-подобные приложения и существующее программное обеспечение VAX/VMS от Digital после незначительного преобразования. Новая операционная система под названием MICA будет поддерживать интерфейсы ULTRIX и VAX/VMS на одном ядре , что позволит легко переносить программное обеспечение для обеих платформ на архитектуру PRISM. [8]

Начавшаяся в 1985 году конструкция PRISM постоянно менялась в ходе ее разработки в ответ на изменения на компьютерном рынке, что приводило к длительным задержкам ее внедрения. Лишь летом 1987 года было решено, что это будет 64-битная конструкция, одна из первых подобных конструкций в формате микропроцессора . В октябре 1987 года Sun Microsystems представила Sun-4 , свою первую рабочую станцию , использующую новый процессор SPARC . Sun-4 работает примерно в три-четыре раза быстрее, чем их последние разработки Sun-3 , использующие Motorola 68020 и любые Unix-предложения от DEC. Планы снова изменились; PRISM снова была переработана как 32-битная часть и нацелена непосредственно на рынок Unix. Это еще больше задержало разработку. [9]

Наблюдая за тем, как сроки поставки PRISM продолжают откладываться, и столкнувшись с возможностью новых задержек, команда в офисе в Пало-Альто решила разработать собственную рабочую станцию с использованием другого RISC-процессора. После комплексной проверки они выбрали MIPS R2000 и построили рабочую станцию под управлением Ultrix за 90 дней. [10] Это вызвало острую дискуссию внутри компании, которая достигла кульминации на собрании руководства в июле 1988 года. PRISM оказалась быстрее, чем R2000, но машины R2000 могли появиться на рынке к январю 1989 года, на год раньше, чем PRISM. Когда это предложение было принято, одна из двух первоначальных ролей PRISM исчезла. К этому моменту решение о создании VMS PRISM уже было принято, так что роли уже не оставалось. PRISM был отменен на встрече. [11]

РИСК ВАКС

[ редактировать ]Когда встреча закончилась, к Бобу Супнику подошел Кен Олсен и заявил, что чипы RISC, похоже, представляют собой будущую угрозу их линии VAX. Он попросил Супника подумать, что можно сделать с VAX, чтобы сохранить его конкурентоспособность по сравнению с будущими RISC-системами. [9]

Это привело к формированию команды «RISCy VAX». Первоначально они рассматривали три концепции. Одна из них представляла собой урезанную версию архитектуры набора команд VAX (ISA), которая могла работать в RISC-подобной системе и оставлять более сложные инструкции VAX для системных подпрограмм. Другой концепцией была чистая RISC-система, которая могла бы «на лету» транслировать существующий код VAX в собственную ISA и сохранять его в кэше ЦП . Наконец, оставалась возможность использовать гораздо более быстрый CISC-процессор, работающий на полной версии VAX ISA. К сожалению, все эти подходы сопряжены с накладными расходами и не могут конкурировать с машиной, работающей на чистом RISC и использующей собственный RISC-код. [12]

Затем группа рассмотрела гибридные системы, сочетающие в себе одно из существующих однокристальных решений VAX и чип RISC в качестве сопроцессора, используемого для обеспечения высокой производительности. Эти исследования показали, что система неизбежно будет ограничена частью с более низкой производительностью и не будет давать убедительных преимуществ. Именно в этот момент Нэнси Кроненберг отметила, что люди используют VMS, а не VAX, и что VMS имеет лишь несколько аппаратных зависимостей, основанных на моделировании прерываний и подкачке памяти. Похоже, не было веской причины, по которой VMS нельзя было бы портировать на RISC-чип, пока сохранялись эти небольшие части модели. Дальнейшая работа над этой концепцией показала, что это работоспособный подход. [12]

Супник представил итоговый отчет Рабочей группе по стратегии в феврале 1989 года. Было поднято два вопроса: может ли полученная в результате конструкция RISC также стать лидером по производительности на рынке Unix и должна ли машина быть открытым стандартом? При этом было принято решение принять архитектуру PRISM с соответствующими модификациями. Это стало концепцией «EVAX», продолжением успешной реализации CMOS CVAX . Когда руководство приняло выводы, они решили дать проекту более нейтральное название, удалив «VAX», и в конечном итоге остановились на «Альфе». [13] Название было вдохновлено использованием «Omega» в качестве кодового названия NVAX на базе модели VAX 4000 ; «Альфа» должна была обозначать начало новой линии (применительно к Альфе и Омеге ). [14] Вскоре после этого начались работы по порту VMS на новую архитектуру . [15]

Альфа

[ редактировать ]В новом дизайне используется большинство основных концепций PRISM, но он был перенастроен, чтобы позволить VMS и программам VMS работать с разумной скоростью без каких-либо преобразований. Основными разработчиками набора команд Alpha были Ричард Л. Сайтс и Ричард Т. Витек. [16] Epicode PRISM был преобразован в PALcode Alpha , предоставляя абстрактный интерфейс для функций, специфичных для реализации платформы и процессора.

Основной вклад Alpha в микропроцессорную индустрию и основная причина ее производительности — это не столько архитектура, сколько ее реализация. [17] В то время (как и сейчас) в индустрии микрочипов доминировали инструменты автоматизированного проектирования и компоновки. Разработчики микросхем Digital продолжали заниматься сложным ручным проектированием схем, чтобы справиться со сложной архитектурой VAX. Чипы Alpha показывают, что ручное проектирование схем, примененное к более простой и чистой архитектуре, позволяет добиться гораздо более высоких рабочих частот, чем те, которые возможны с помощью более автоматизированных систем проектирования. Эти микросхемы вызвали возрождение проектирования нестандартных схем в сообществе разработчиков микропроцессоров.

Первоначально процессоры Alpha имели обозначение серии DECchip 21x64 . [18] с «DECchip», замененным в середине 1990-х на «Альфу». Первые две цифры «21» означают 21 век, а последние две цифры «64» означают 64 бита. [18] Alpha с самого начала разрабатывалась как 64-битная, и 32-битной версии не существует. Средняя цифра соответствует поколению архитектуры Alpha. Внутри процессоры Alpha также обозначались номерами EV , официально EV означает «Extended VAX», но имело альтернативное юмористическое значение «Electric Vlasic », отдавая дань уважения эксперименту Electric Pickle в Western Research Lab. [19]

В мае 1997 года DEC подала в суд на Intel за якобы нарушение ее патентов Alpha при разработке оригинальных чипов Pentium , Pentium Pro и Pentium II . [20] В рамках мирового соглашения большая часть бизнеса DEC по разработке и производству микросхем была продана Intel. DEC StrongARM Сюда входила реализация компьютерной архитектуры ARM , которую Intel продавала как процессоры XScale, обычно используемые в карманных ПК . Ядро Digital Semiconductor, группа микропроцессоров Alpha, осталась за DEC, а связанные с ней офисные здания перешли к Intel как часть завода в Хадсоне. [21]

Улучшенные модели

[ редактировать ]Первые несколько поколений чипов Alpha были одними из самых инновационных в свое время.

- Предсерийная модель, получившая обозначение EV3 , использовалась в прототипе системы под названием Alpha Demonstration Unit (ADU). ADU использовались для переноса операционных систем на архитектуру Alpha. Одним из ключевых отличий между EV3 и более поздними моделями было отсутствие блока с плавающей запятой. [22]

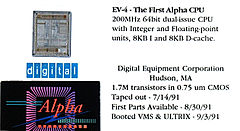

- Первая версия, Alpha 21064 или EV4 , является первым CMOS- микропроцессором, рабочая частота которого конкурирует с более мощными ECL . мини-компьютерами и мейнфреймами

- Второй, 21164 или EV5 , является первым микропроцессором, разместившим на кристалле большой вторичный кэш. [23]

- Третий, 21264 или EV6 , является первым микропроцессором, сочетающим в себе как высокую рабочую частоту, так и более сложную микроархитектуру внеочередного исполнения .

- 21364 или — первый высокопроизводительный EV7 процессор со встроенным контроллером памяти . [24]

- Невыпущенный 21464 или EV8 был первым процессором, поддерживающим одновременную многопоточность , но эта версия была отменена после продажи DEC компании Compaq . Исследовательский проект Tarantula векторный , который, скорее всего, назывался бы EV9 , стал бы первым процессором Alpha, в котором использовался процессор . [25]

Постоянные сообщения, приписываемые инсайдерам DEC, предполагают, что выбор тега AXP для процессора был сделан юридическим отделом DEC, который все еще переживал фиаско с торговой маркой VAX . [26] После долгих поисков тег «AXP» оказался совершенно свободным. В компьютерной индустрии пошла шутка о том, что аббревиатура AXP означает «Почти точно ПРИЗМА». [ нужна ссылка ]

Принципы проектирования

[ редактировать ]Архитектура Alpha задумывалась как высокопроизводительная конструкция. Digital планировала, что архитектура обеспечит тысячекратное увеличение производительности за двадцать пять лет. Чтобы обеспечить это, были удалены все архитектурные особенности, которые препятствовали выпуску нескольких инструкций, тактовой частоте или многопроцессорной обработке. В результате в Альфе нет:

- Слоты задержки ответвления

- Подавленные инструкции [ нужны разъяснения ]

- Инструкции по загрузке или сохранению байтов (позже добавленные с помощью расширений байтовых слов (BWX)) [27] [28]

Коды условий

[ редактировать ]В Alpha нет кодов условий для целочисленных инструкций. [29] чтобы устранить потенциальное узкое место в регистре состояния состояния. Инструкции, приводящие к переполнению, например, сложение двух чисел, результат которых не умещается в 64 бита, записывают 32 или 64 младших бита в регистр назначения. Перенос генерируется путем выполнения беззнакового сравнения результата с любым операндом, чтобы определить, меньше ли результат любого операнда. Если проверка была верной, значение единицы записывается в младший бит регистра назначения, чтобы указать условие.

Регистры

[ редактировать ]

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Архитектура определяет набор из 32 целочисленных регистров и набор из 32 регистров с плавающей запятой в дополнение к программному счетчику , двум регистрам блокировки и регистру управления с плавающей запятой (FPCR). Он также определяет регистры, которые были необязательными и реализовывались только в том случае, если они были необходимы для реализации. регистры для PALcode Наконец, определяются .

Целочисленные регистры обозначаются от R0 до R31, а регистры с плавающей запятой обозначаются от F0 до F31. Регистры R31 и F31 жестко запрограммированы на ноль, и запись в эти регистры по инструкциям игнорируется. В цифровом формате рассматривалось использование комбинированного файла регистров, но было решено, что разделенный файл регистров лучше, поскольку он позволяет двухчиповым реализациям иметь файл регистров, расположенный на каждом чипе, а реализациям только с целыми числами опускать файл регистров с плавающей запятой, содержащий регистры с плавающей запятой. Также было установлено, что файл разделенного регистра более подходит для выполнения нескольких команд из-за меньшего количества портов чтения и записи. Также учитывалось количество регистров в файле регистров: претендентами были 32 и 64. Компания Digital пришла к выводу, что 32 регистра более подходят, поскольку требуют меньше места на кристалле , что повышает тактовую частоту. Такое количество регистров не считалось серьезной проблемой с точки зрения производительности и будущего роста, поскольку тридцать два регистра могли поддерживать как минимум восьмиканальную инструкцию.

Счетчик программ представляет собой 64-битный регистр, который содержит адрес виртуального байта, выровненный по длинному слову, то есть два младших бита счетчика программ всегда равны нулю. PC увеличивается на четыре до адреса следующей инструкции, когда инструкция декодируется. Флаг блокировки и регистр заблокированного физического адреса используются инструкциями с блокировкой загрузки и сохранением для поддержки многопроцессорности. Регистр управления плавающей запятой (FPCR) — это 64-битный регистр, определенный архитектурой, предназначенной для использования реализациями Alpha с IEEE 754 аппаратным обеспечением с плавающей запятой, совместимым со стандартом .

Типы данных

[ редактировать ]В архитектуре Alpha байт определяется как 8-битное значение (октет), слово как 16-битное значение, длинное слово как 32-битное значение, четверное слово как 64-битное значение, а октаслово как данные 32-битное значение. 128-битные .

Архитектура Alpha изначально определяла шесть типов данных:

- Четверное слово (64-битное) целое число

- Длинное слово (32-битное) целое число

- IEEE T-с плавающей запятой (двойной точности, 64 бита)

- IEEE S-с плавающей запятой (одинарная точность, 32 бита)

Чтобы поддерживать уровень совместимости с VAX , 32-битной архитектурой, предшествовавшей Alpha, включены два других типа данных с плавающей запятой:

- VAX G-с плавающей запятой (двойной точности, 64 бита)

- VAX F-с плавающей запятой (одинарная точность, 32 бита)

VAX H-с плавающей запятой (четверенная точность, 128 бит) не поддерживался, [30] но еще один 128-битный вариант с плавающей запятой, X-floating point, доступен в Alpha, но не в VAX. [31]

H и X были описаны как похожие, но не идентичные. Программная эмуляция H-floating доступна от DEC, как и преобразователь уровней исходного кода под названием DECmigrate.

Память

[ редактировать ]Alpha имеет 64-битное линейное виртуальное адресное пространство без сегментации памяти. Реализации могут реализовать меньшее виртуальное адресное пространство с минимальным размером 43 бита. Хотя неиспользуемые биты не были реализованы в аппаратном обеспечении, таком как TLB , архитектура требовала, чтобы реализации проверяли, равны ли они нулю, чтобы обеспечить совместимость программного обеспечения с реализациями с большим (или полным) виртуальным адресным пространством.

Форматы инструкций

[ редактировать ]Alpha ISA имеет фиксированную длину команды 32 бита. Он имеет шесть форматов инструкций.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Тип |

| Код операции | Солнце | руб. | Неиспользованный | 0 | Функция | Rc | Целочисленная операция | |||||||||||||||||||||||||

| Код операции | Солнце | Буквальный | 1 | Функция | Rc | Целочисленная операция, буквальная | ||||||||||||||||||||||||||

| Код операции | Солнце | руб. | Функция | Rc | Работа с плавающей запятой | |||||||||||||||||||||||||||

| Код операции | Солнце | руб. | Смещение | Формат памяти | ||||||||||||||||||||||||||||

| Код операции | Солнце | Смещение | Формат филиала | |||||||||||||||||||||||||||||

| Код операции | Функция | Формат CALL_PAL | ||||||||||||||||||||||||||||||

Целочисленный формат операции используется целочисленными инструкциями. Он содержит 6-битное поле кода операции, за которым следует поле Ra, указывающее регистр, содержащий первый операнд, и поле Rb, указывающее регистр, содержащий второй операнд. Далее идет 3-битное поле, которое не используется и зарезервировано. 1-битное поле содержит «0», что отличает этот формат от формата целочисленных литералов. Далее следует 7-битное функциональное поле, которое используется вместе с кодом операции для указания операции. Последнее поле — это поле Rc, которое определяет регистр, в который должен быть записан результат вычисления. Все поля регистров имеют длину 5 бит и необходимы для адресации 32 уникальных ячеек, 32 целочисленных регистров.

Формат целочисленного литерала используется целочисленными инструкциями, которые используют литерал в качестве одного из операндов. Формат такой же, как формат целочисленной операции, за исключением замены 5-битного поля Rb и 3 битов неиспользуемого пространства 8-битным литеральным полем, которое расширяется нулями до 64-битного операнда.

Формат операций с плавающей запятой используется инструкциями с плавающей запятой. Он похож на формат целочисленной операции, но имеет 11-битное функциональное поле, что стало возможным благодаря использованию литеральных и неиспользуемых битов, которые зарезервированы в целочисленном формате операции.

Формат памяти используется в основном инструкциями загрузки и сохранения. Он имеет 6-битное поле кода операции, 5-битное поле Ra, 5-битное поле Rb и 16-битное поле смещения.

Инструкции ветвления имеют 6-битное поле кода операции, 5-битное поле Ra и 21-битное поле смещения. Поле Ra указывает регистр, который будет проверяться командой условного перехода, и если условие выполняется, счетчик программы обновляется путем добавления содержимого поля смещения к счетчику программы. Поле смещения содержит целое число со знаком, и если значение целого числа положительное, то при выборе перехода счетчик программы увеличивается. Если значение целого числа отрицательное, то счетчик программы уменьшается, если ветвь выбрана. Таким образом, диапазон ветвления составляет ±1 Mi инструкций или ±4 MiB. Архитектура Alpha была разработана с широким диапазоном возможностей как часть дальновидной цели архитектуры.

Формат CALL_PAL используется CALL_PAL инструкция, которая используется для вызова подпрограмм PALcode . В этом формате сохраняется поле кода операции, но остальные заменяются 26-битным функциональным полем, которое содержит целое число, определяющее подпрограмму PAL.

Набор инструкций

[ редактировать ]Инструкции по управлению

[ редактировать ]Инструкции управления состоят из условных и безусловных переходов и переходов. Инструкции условного и безусловного перехода используют формат инструкций перехода, тогда как инструкции перехода используют формат инструкций памяти.

Условные переходы проверяют, установлен или очищен младший бит регистра, или сравнивают регистр как знаковое четверное слово с нулем и выполняют переход, если указанное условие истинно. Условиями сравнения регистра с нулем являются равенство, неравенство, меньше, меньше или равно, больше или равно и больше. Новый адрес вычисляется путем выравнивания длинного слова и расширения знака 21-битного смещения и добавления его к адресу инструкции, следующей за условной ветвью.

Безусловные переходы обновляют программный счетчик новым адресом, вычисляемым так же, как и условные переходы. Они также сохраняют в регистре адрес инструкции, следующей за безусловным переходом. Таких инструкций две, и они отличаются только подсказками, предусмотренными для аппаратуры предсказания ветвлений.

Имеется четыре инструкции прыжка. Все они выполняют одну и ту же операцию, сохраняя адрес инструкции после перехода и предоставляя счетчику программы новый адрес из регистра. Они отличаются подсказками, предоставляемыми оборудованию прогнозирования ветвлений. Для этой цели используется неиспользуемое поле смещения.

Целочисленная арифметика

[ редактировать ]Инструкции целочисленной арифметики выполняют сложение, умножение и вычитание длинных слов и четверных слов; и сравнение четверных слов. Инструкций по разделению нет, поскольку архитекторы считали, что аппаратная реализация разделения противоречит простоте. Помимо стандартных инструкций сложения и вычитания, существуют масштабированные версии. Эти версии сдвигают второй операнд влево на два или три бита перед добавлением или вычитанием. Инструкции Multiply Longword и Multiply Quadword записывают младшие 32 или 64 бита 64- или 128-битного результата в регистр назначения соответственно. Поскольку полезно получить старшую половину, Unsigned Multiply Quadword High предусмотрена инструкция (UMULH). UMULH используется для реализации алгоритмов арифметики и деления с высокой точностью. Концепция отдельной инструкции умножения, возвращающей старшую половину результата, была взята из PRISM .

Инструкции, работающие с длинными словами, игнорируют старшую половину регистра, и 32-битный результат расширяется по знаку перед записью в регистр назначения. По умолчанию инструкции сложения, умножения и вычитания, за исключением UMULH и масштабированных версий сложения и вычитания, не перехватывают переполнение. Когда такая функциональность требуется, предоставляются версии этих инструкций, которые выполняют обнаружение переполнения и перехватывают переполнение.

Инструкции сравнения сравнивают два регистра или регистр и литерал и записывают «1» в регистр назначения, если указанное условие истинно, или «0», если нет. Условиями являются равенство, неравенство, меньше или равно и меньше. За исключением инструкций, определяющих первые два условия, существуют версии, выполняющие знаковые и беззнаковые сравнения.

Инструкции целочисленной арифметики используют форматы инструкций целочисленной операции.

Логично и сдвиг

[ редактировать ]Логические инструкции состоят из инструкций для выполнения поразрядных логических операций и условных перемещений в целочисленных регистрах. Побитовые логические инструкции выполняют AND , NAND , NOR , OR , XNOR и XOR между двумя регистрами или регистром и литералом. Инструкции условного перемещения проверяют регистр как четверное слово со знаком на ноль и перемещают, если указанное условие истинно. Указанными условиями являются равенство, неравенство, меньше или равно, меньше, больше или равно и больше. Инструкции сдвига выполняют арифметический сдвиг вправо , а также логические сдвиги влево и вправо . Сумма сдвига задается регистром или литералом. Логические инструкции и инструкции сдвига используют форматы инструкций целочисленной операции.

Расширения

[ редактировать ]Расширения байтовых слов (BWX)

[ редактировать ]Более поздние версии Alpha включают расширения байтовых слов — набор инструкций для управления 8-битными и 16-битными типами данных. Эти инструкции впервые были представлены в микропроцессоре 21164А (EV56) и присутствуют во всех последующих реализациях. Эти инструкции выполняют операции, для реализации которых раньше требовалось несколько инструкций, что повышает плотность кода и производительность некоторых приложений. BWX также упрощает эмуляцию машинного кода x86 и написание драйверов устройств . [32]

| Мнемоника | Инструкция |

|---|---|

LDBU | Загрузить расширенный нулем байт из памяти в регистр |

LDWU | Загрузить слово с нулевым расширением из памяти в регистр |

SEXTB | Знак расширения байта |

SEXTW | Знак «Расширить слово» |

STB | Сохранение байта из регистра в память |

STW | Сохранение слова из регистра в память |

Видеоинструкции по перемещению (МВИ)

[ редактировать ]Инструкции Motion Video (MVI) представляли собой расширение набора команд Alpha ISA, которое добавляло инструкции для операций с одной командой и несколькими данными (SIMD). [33] Реализации Alpha, реализующие MVI, в хронологическом порядке: Alpha 21164PC (PCA56 и PCA57), Alpha 21264 (EV6) и Alpha 21364 (EV7). В отличие от большинства других наборов команд SIMD того же периода, таких как MIPS MDMX . или SPARC ( Visual Instruction Set , но, как и -RISC PA расширения мультимедийного ускорения MAX-1, MAX-2), MVI представлял собой простой набор команд состоит из нескольких инструкций, которые оперируют целочисленными типами данных, хранящимися в существующих целочисленных регистрах.

Простота MVI обусловлена двумя причинами. Во-первых, Digital определила, что Alpha 21164 уже способен выполнять декодирование DVD с помощью программного обеспечения, поэтому не требует для этой цели аппаратного обеспечения, но неэффективен при MPEG-2 кодировании . Вторая причина — необходимость сохранить короткие сроки внедрения. Добавление большого количества инструкций усложнило бы и расширило бы логику декодирования инструкций, уменьшив тактовую частоту реализации.

MVI состоит из 13 инструкций:

| Мнемоника | Инструкция |

|---|---|

MAXSB8 | Максимальный векторный байт со знаком |

MAXSW4 | Максимум векторного подписанного слова |

MAXUB8 | Максимум векторного беззнакового байта |

MAXUW4 | Максимум векторного беззнакового слова |

MINSB8 | Минимум векторного байта со знаком |

MINSW4 | Минимум векторного подписанного слова |

MINUB8 | Минимум векторного беззнакового байта |

MINUW4 | Минимум векторного беззнакового слова |

PERR | Ошибка пикселя |

PKLB | Упакуйте длинные слова в байты |

PKWB | Упаковать слова в байты |

UNPKBL | Распаковать байты в длинные слова |

UNPKBW | Распаковать байты в слова |

Расширения с плавающей запятой (FIX)

[ редактировать ]Расширения с плавающей запятой (FIX) являются расширением архитектуры Alpha. Он вводит девять инструкций для извлечения квадратного корня с плавающей запятой и для передачи данных в и из целочисленных регистров и регистров с плавающей запятой. Alpha 21264 (EV6) — первый микропроцессор, реализующий эти инструкции.

| Мнемоника | Инструкция |

|---|---|

FTOIS | Перемещение регистра с плавающей запятой в целое число, S_floating |

FTOIT | Перемещение регистра с плавающей запятой в целое число, T_floating |

ITOFF | Перемещение регистра из целого числа в число с плавающей запятой, F_floating |

ITOFS | Перемещение регистра из целого числа в число с плавающей запятой, S_floating |

ITOFT | Перемещение регистра из целого числа в число с плавающей запятой, T_floating |

SQRTF | Квадратный корень F_floating |

SQRTG | Квадратный корень G_floating |

SQRTS | Квадратный корень S_floating |

SQRTT | Квадратный корень T_floating |

Расширения подсчета (CIX)

[ редактировать ]Count Extensions (CIX) — это расширение архитектуры, которое вводит три инструкции для подсчета битов. Эти инструкции относятся к категории инструкций целочисленной арифметики. Впервые они были реализованы на Alpha 21264A (EV67).

| Мнемоника | Инструкция |

|---|---|

CTLZ | Считаем ведущий ноль |

CTPOP | Подсчитать население |

CTTZ | Считать конечный ноль |

Реализации

[ редактировать ]На момент анонса Alpha была объявлена архитектурой на следующие 25 лет. Хотя этого не произошло, Альфа, тем не менее, прожила достаточно долгую жизнь. Первая версия, Alpha 21064 (также называемая EV4 ), была представлена в ноябре 1992 года и работала на частоте до 192 МГц; небольшое уменьшение кристалла ( EV4S , уменьшенное с 0,75 мкм до 0,675 мкм) несколько месяцев спустя работало на частоте 200 МГц. 64-битный процессор представлял собой суперконвейерную и суперскалярную конструкцию, как и другие конструкции RISC, но, тем не менее, превосходил их все, и DEC рекламировала его как самый быстрый процессор в мире. Пристальное внимание к проектированию схем, отличительная черта команды разработчиков Hudson, такая как огромная централизованная схема тактирования, позволило им запускать процессор на более высоких скоростях, хотя микроархитектура была довольно похожа на другие RISC-чипы. Для сравнения, менее дорогой Intel Pentium , когда он был выпущен следующей весной, работал на частоте 66 МГц.

Alpha 21164 или EV5 стал доступен в 1995 году с частотой процессора до 333 МГц. В июле 1996 года скорость линии была увеличена до 500 МГц, в марте 1998 года - до 666 МГц. Также в 1998 году была выпущена Alpha 21264 ( EV6 ) с частотой 450 МГц, которая в конечном итоге достигла (в 2001 году с 21264C / EV68CB ) 1,25 ГГц. В 2003 году был выпущен Alpha 21364 или EV7 Marvel , по сути, с ядром EV68 с четырьмя процессорами по 1,6 ГБ/с. [а] каналы межпроцессорной связи для повышения производительности многопроцессорной системы, работающие на частоте 1 или 1,15 ГГц.

В 1996 году лицензия на производство чипов Alpha была передана компании Samsung Electronics . После покупки Digital компанией Compaq большая часть продуктов Alpha была передана API NetWorks , Inc. (ранее Alpha Processor Inc.), частной компании, финансируемой Samsung и Compaq. В октябре 2001 года Microway стала эксклюзивным поставщиком продаж и услуг линейки продуктов API NetWorks на базе Alpha.

25 июня 2001 года Compaq объявила, что к 2004 году Alpha будет прекращена в пользу Intel Itanium , отменила запланированный чип EV8 и продала всю интеллектуальную собственность Alpha компании Intel . [6] Hewlett-Packard объединилась с Compaq в 2002 году; HP объявила, что разработка серии Alpha продолжится еще несколько лет, включая выпуск варианта EV7 с тактовой частотой 1,3 ГГц, получившего название EV7z . Это будет последняя итерация Alpha, EV79 с толщиной 0,13 мкм также будет отменена.

Alpha также реализована в Piranha , исследовательском прототипе, разработанном группами корпоративных исследований и непрерывной разработки оборудования Compaq в Западной исследовательской лаборатории и Центре системных исследований. Piranha — это многоядерная конструкция для рабочих нагрузок обработки транзакций , содержащая восемь простых ядер. Он был описан на 27-м ежегодном международном симпозиуме по компьютерной архитектуре в июне 2000 года. [34]

Утверждается, что ранние версии архитектуры Sunway основаны на Alpha, однако, начиная с SW26010 , Sunway использует новую архитектуру набора команд, не связанную с Alpha. [35] [36]

История модели

[ редактировать ]| Модель | Номер модели | Год | Частота [МГц] | Процесс [мкм] | Транзисторы [миллионы] | Размер матрицы [мм 2 ] | я прикалываю | Мощность [Вт] | Напряжение | Дкэш [КБ] [б] | Икэш [КБ] | Скеш | Бкэш | ОДИН | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ЭВ4 | 21064 | 1992 | 100–200 | 0.75 | 1.68 | 234 | 290 | 30 | 3.3 | 8 | 8 | – | 128 КБ–16 МБ | ||

| EV4S | 21064 | 1993 | 100–200 | 0.675 | 1.68 | 186 | 290 | 27 | 3.3 | 8 | 8 | – | 128 КБ–16 МБ | ||

| ЕВ45 | 21064А | 1994 | 200–300 | 0.5 | 2.85 | 164 | 33 | 3.3 | 16 | 16 | – | 256 КБ–16 МБ | |||

| LCA4 | 21066 | 1993 | 100–166 | 0.675 | 1.75 | 209 | 21 | 3.3 | 8 | 8 | – | ||||

| LCA4 | 21068 | 1994 | 66 | 0.675 | 1.75 | 209 | 9 | 3.3 | 8 | 8 | – | ||||

| ДМС45 | 21066А | 1994 | 100–266 | 0.5 | 1.8 | 161 | 23 | 3.3 | 8 | 8 | – | ||||

| ДМС45 | 21068А | 1994 | 100 | 0.5 | 1.8 | 161 | 3.3 | 8 | 8 | – | |||||

| ЕВ5 | 21164 | 1995 | 266–500 | 0.5 | 9.3 | 299 | 296 | 56 | 3.3/2.5 | 8 | 8 | 96 КБ | До 64 МБ | Р | |

| ЕВ56 | 21164А | 1996 | 366–666 [1] | 0.35 | 9.66 [1] | 209 | 31–55 [1] | 3.3/2.5 [1] | 8 | 8 | 96 КБ | До 64 МБ | Р, Б | ||

| PCA56 | 21164ПК | 1997 | 400–533 | 0.35 | 3.5 | 141 | 264 | 26–35 | 3.3/2.5 | 8 | 16 | – | 512 КБ–4 МБ | Р,Б,М | |

| PCA57 | 21164ПК | 600–666 | 0.28 | 5.7 | 101 | 283 | 18–23 | 2.5/2.0 | 16 | 32 [1] | – | 512 КБ–4 МБ | Р,Б,М | ||

| ЕВ6 | 21264 | 1998 | 450–600 | 0.35 | 15.2 | 314 | 389 | 73 | 2.0 | 64 | 64 | – | 2–8 МБ | Р, Б, М, Ф | |

| ЕВ67 | 21264А | 1999 | 600–750 | 0.25 | 15.2 | 210 | 389 | 2.0 | 64 | 64 | – | 2–8 МБ | Р, Б, М, Ж, Ц | ||

| ЭВ68АЛ | 21264Б | 2001 | 800–833 | 0.18 | 15.2 | 125 | 1.7 | 64 | 64 | – | 2–8 МБ | Р, Б, М, Ж, К, Т | |||

| EV68CB | 21264C | 2001 | 1000–1250 | 0.18 | 15.2 | 125 | 65–75 | 1.65 | 64 | 64 | – | 2–8 МБ | Р, Б, М, Ж, К, Т | ||

| EV68CX | 21264D | 1.65 | 64 | 64 | – | 2–8 МБ | Р, Б, М, Ж, К, Т | ||||||||

| ЕВ7 | 21364 | 2003 | 1000–1150 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1,75 МБ | – | Р, Б, М, Ж, К, Т | ||

| EV7z | 21364 | 2004 | 1300 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1,75 МБ | – | Р, Б, М, Ж, К, Т | ||

| Отменено | |||||||||||||||

| ЭВ78/ЭВ79 | 21364А | Запланировано на 2004 год | 1700 | 0.13 | 152 | 300 | 120 | 1.2 | 64 | 64 | 1,75 МБ | – | Р, Б, М, Ж, К, Т | ||

| ЕВ8 | 21464 | Запланировано на 2003 год | 1200–2000 | 0.125 | 250 | 420 | 1800 | ?? | 1.2 | 64 | 64 | 3 МБ | – | Р, Б, М, Ж, К, Т | |

- ISA-расширения

- R — Аппаратная поддержка округления до бесконечности и отрицательной бесконечности. [37]

- B – BWX, «Расширение байта/слова», добавляющее инструкции, позволяющие выполнять 8- и 16-битные операции из памяти и ввода-вывода.

- М – МВИ, «мультимедийные» инструкции.

- F – FIX, инструкции для перемещения данных между целочисленными регистрами и регистрами с плавающей запятой, а также для извлечения квадратного корня.

- C – CIX, инструкции по подсчету и поиску битов.

- T — поддержка предварительной выборки с намерением изменения для повышения производительности первой попытки получить блокировку.

Производительность

[ редактировать ]Чтобы проиллюстрировать сравнительную производительность систем на базе Alpha, Standard Performance Evaluation Corporation ниже приведены некоторые показатели производительности (SPEC) (SPECint95, SPECfp95). Обратите внимание, что результаты SPEC сообщают об измеренной производительности всей компьютерной системы (ЦП, шина, память, оптимизатор компилятора), а не только ЦП. Также обратите внимание, что эталонный тест и масштаб менялись с 1992 по 1995 год. Однако цифры дают приблизительное представление о производительности архитектуры Alpha (64-разрядной версии) по сравнению с современными предложениями HP (64-разрядной версии) и Intel ( 32-битная). Возможно, наиболее очевидная тенденция заключается в том, что, хотя Intel всегда могла приблизиться к Alpha по производительности целых чисел, в производительности с плавающей запятой разница была значительной. С другой стороны, HP ( PA-RISC ) также достаточно близок к Alpha, но эти процессоры работают на значительно более низких тактовых частотах (МГц). В таблицах отсутствуют два важных значения: энергопотребление и цена процессора.

|

|

Системы на базе Альфа

[ редактировать ]Первое поколение систем на базе DEC Alpha включает DEC 3000 AXP рабочие станции и серверы начального уровня DEC 4000 AXP , серверы среднего класса DEC 7000 AXP и 10000 AXP и высокопроизводительные серверы . Системы DEC 3000 AXP используют ту же шину TURBOchannel , что и предыдущие модели DECstation на базе MIPS , тогда как система 4000 основана на Futurebus +, а системы 7000/10000 разделяют архитектуру с соответствующими моделями VAX .

DEC также выпустила персонального компьютера рабочую станцию Alpha конфигурации (ПК) с шиной расширенной отраслевой стандартной архитектуры (EISA), DECpc AXP 150 (кодовое имя Jensen , также называемое DEC 2000 AXP). Это первая система Alpha, поддерживающая Windows NT . Позже DEC выпустила альфа-версии своих линеек ПК Celebris XL и Digital Personal Workstation с процессорами 21164.

Digital также производила одноплатные компьютеры на базе VMEbus для встраиваемого и промышленного использования. Первое поколение включает AXPvme 64 и AXPvme 64LC на базе 21068, а также AXPvme 160 на базе 21066. Они были представлены 1 марта 1994 года. Более поздние модели, такие как AXPvme 100, AXPvme 166 и AXPvme 230, основаны на процессоре 21066A. , а Alpha VME 4/224 и Alpha VME 4/288 основаны на процессоре 21064A. Последние модели Alpha VME 5/352 и Alpha VME 5/480 основаны на процессоре 21164.

Чип 21066 используется в компактной рабочей станции DEC Multia VX40/41/42 и ноутбуке ALPHAbook 1 от Tadpole Technology.

В 1994 году DEC выпустила новую линейку систем AlphaStation и AlphaServer . В них используются процессоры 21064 или 21164, имеется шина PCI , VGA -совместимые буферы кадров , а также клавиатуры и мыши в стиле PS/2 . Серия AlphaServer 8000 заменяет DEC 7000/10000 AXP и также использует шины XMI и FutureBus+.

AlphaStation XP1000 — первая рабочая станция на базе процессора 21264. Более поздние модели AlphaServer/Station, основанные на 21264, делятся на семейства DS (сервер подразделения), ES (корпоративный сервер) или GS (глобальный сервер).

Последний чип 21364 используется в моделях AlphaServer ES47, ES80 и GS1280 и AlphaStation ES47.

DEC произвела ряд OEM- материнских плат , таких как AXPpci 33 «NoName» на базе 21066 и 21068, что стало частью серьезного продвижения компании на OEM-рынок. [38] AlphaPC 164 и AlphaPC 164LX на базе 21164, AlphaPC 164SX и AlphaPC 164RX на базе 21164PC и AlphaPC 264DP на базе 21264. Несколько третьих сторон, таких как Samsung и API, также производили материнские платы OEM, такие как API UP1000 и UP2000.

Чтобы помочь третьим сторонам в разработке аппаратного и программного обеспечения для платформы, DEC выпустила оценочные платы, такие как EB64+ и EB164 для микропроцессоров Alpha 21064A и 21164 соответственно.

Процессоры 21164 и 21264 использовались NetApp в различных сетевых системах хранения данных, а процессоры 21064 и 21164 использовались компанией Cray в их T3D и T3E суперкомпьютерах с массовым параллелизмом .

Суперкомпьютеры

[ редактировать ]Самым быстрым суперкомпьютером на базе процессоров Alpha стал ASCI Q в Национальной лаборатории Лос-Аламоса. Машина была построена как кластер HP AlphaServer SC45/GS. Он имел 4096 процессоров Alpha (21264 EV-68, 1,25 ГГц) и достигал максимальной производительности 7,727 терафлопс . [39]

Примечания

[ редактировать ]Ссылки

[ редактировать ]- ^ Перейти обратно: а б с д и ж Пол В. Болотов (21 апреля 2007 г.). «Альфа: История в фактах и комментариях» . Архивировано из оригинала 3 декабря 2013 года . Проверено 22 ноября 2008 г.

- ^ Аарон Сакович (2001). «Виндовс 2000?» . Источник AlphaNT. Архивировано из оригинала 8 июля 2008 г. Проверено 1 января 2007 г.

- ^ «SUSE Linux 7.0 Альфа-версия» . СУЗЕ. 2000. Архивировано из оригинала 8 января 2014 г. Проверено 8 января 2014 г.

- ^ Джордж А. Дарси III; Рональд Ф. Брендер; Стивен Дж. Моррис; Майкл В. Айлс (1992). «Использование моделирования для разработки и портирования программного обеспечения» (PDF) . Цифровой технический журнал . 4 (4): 181–192.

- ^ «Призрак DEC Alpha – вот почему Windows плохо справляется со сжатием файлов» . TheRegister.co.uk . 2 ноября 2016 г. Архивировано из оригинала 20 сентября 2018 г. Проверено 20 сентября 2018 г.

- ^ Перейти обратно: а б Попович, Кен (28 июня 2001 г.). «Альфа оказалась дорогостоящей для Compaq» . ЗДНет . Архивировано из оригинала 3 марта 2016 г. Проверено 2 марта 2016 г.

- ^ «Преобразование среды AlphaServer» . ХП. Архивировано из оригинала 8 февраля 2007 г. Проверено 11 января 2007 г.

- ^ Кэтрин Ричардсон; Терри Моррис; Рокки Морган; Рид Браун; Донна Мейкле (март 1987 г.). «Бизнес-план программного обеспечения MICA» (PDF) . bitsavers.org . Архивировано (PDF) из оригинала 07 января 2021 г. Проверено 4 января 2021 г.

- ^ Перейти обратно: а б Супник, Боб (24 февраля 2008 г.). «Микропризма» . Проект моделирования компьютерной истории . Архивировано из оригинала 3 апреля 2021 года . Проверено 26 апреля 2021 г.

- ^ Болотов, Павел V (22 апреля 2007 г.). «Альфа: История в фактах и комментариях» . Архивировано из оригинала 29 сентября 2019 г. Проверено 9 сентября 2019 г.

- ^ Марк Смотерман. "Эскиз DEC PRISM" . Архивировано из оригинала 04 апреля 2020 г. Проверено 20 сентября 2018 г.

PRISM (Параллельная машина с сокращенным набором команд) ... первый проект архитектуры PRISM в августе 1985 года; DEC отменяет проект в 1988 году в пользу системы на базе MIPS...

- ^ Перейти обратно: а б Комерфорд, Ричард (июль 1992 г.). «Как DEC разработала Alpha» . IEEE-спектр . 29 (7): 28. дои : 10.1109/6.144508 . Архивировано из оригинала 20 июня 2018 г. Проверено 23 октября 2021 г.

- ^ Супник, Боб (1992). «Предисловие» . Цифровой технический журнал . 4 (4). Архивировано из оригинала 3 мая 2021 г. Проверено 03 мая 2021 г.

- ^ Супник, Роберт (2 мая 2017 г.). «Устная история Роберта Супника» (PDF) . Computerhistory.org (Интервью). Беседовал Гарднер Хендри. Музей истории компьютеров . Проверено 6 апреля 2024 г.

- ^ «Управление технологическими скачками: исследование группы разработчиков Alpha Alpha» (PDF) . Апрель 1993 г. Архивировано (PDF) из оригинала 7 февраля 2021 г. Проверено 26 апреля 2021 г.

- ^ Ричард Л. Сайтс; Ричард Т. Витек (16 мая 2014 г.). Справочное руководство по архитектуре Alpha AXP – 2-е издание . Цифровая пресса. ISBN 978-1-4831-8403-6 . Архивировано из оригинала 20 сентября 2018 г. Проверено 20 сентября 2018 г.

- ^ Уорнер, В. (22 декабря 2004 г.). «Великие моменты в истории микропроцессоров» . ИБМ . Архивировано из оригинала 19 января 2018 года . Проверено 18 января 2018 г.

- ^ Перейти обратно: а б «cpu-collection.de – DEC Alpha AXP» . Архивировано из оригинала 20 сентября 2018 г. Проверено 20 сентября 2018 г.

Первые процессоры семейства Alpha получили обозначение серии DECchip 21064 («21» означает 21 век).

- ^ Билл Гамбурген; Джефф Могул; Брайан Рид ; Алан Юстас ; Ричард Свон; Мэри Джо Доэрти; Джоэл Бартлетт (1989). «Техническое примечание WRL TN-13: Характеристика систем органического освещения» . Корпорация цифрового оборудования. Архивировано из оригинала ( PDF ) 12 мая 2008 г. . Проверено 4 октября 2007 г.

{{cite journal}}: Для цитирования журнала требуется|journal=( помощь ) - ^ Брэдли, Гейл; ДеТар, Джим (19 мая 1997 г.). «DEC и Cyrix подают в суд на Intel» . Электронные новости . Том. 43, нет. 2168. С. 1, 60. ISSN 1061-6624 .

- ^ Баум, Аллан (18 июля 2018 г.). «Устная история Аллена Баума» (PDF) (интервью). Беседовал Дэвид Брок. п. 60. Архивировано (PDF) из оригинала 7 февраля 2021 г.

- ^ Чарльз П. Такер; Дэвид Дж. Конрой; Лоуренс К. Стюарт (1992). «Демонстрационный блок Alpha: высокопроизводительный мультипроцессор для разработки программного обеспечения и микросхем» (PDF) . Цифровой технический журнал . 4 (4): 51 . Проверено 6 апреля 2024 г.

- ^ Джон Х. Эдмондсон; Пол И. Рубинфельд; Питер Дж. Бэннон; Брэдли Дж. Беншнайдер; Дебра Бернштейн; Рубен В. Кастелино; Элизабет М. Купер; Дэниел Э. Девер; Дейл Р. Дончин; Тимоти К. Фишер; Анил К. Джайн; Шекхар Мехта; Жанна Э. Мейер; Рональд П. Престон; Видья Раджагопалан; Чандрасекхара Соманатан; Скотт А. Тейлор; Гилберт М. Уолрич (1995). «Внутренняя организация Alpha 21164, 64-битного четырехканального CMOS RISC-микропроцессора с частотой 300 МГц». Цифровой технический журнал . 7 (1): 119–135. CiteSeerX 10.1.1.38.9551 .

большой встроенный кэш второго уровня с обратной записью

- ^ Обзоры, CTI (2016). Структурированная компьютерная организация . ISBN 978-1478426738 .

21364 ... первый высокопроизводительный процессор со встроенным контроллером памяти.

- ^ Роджер Эспаса; Федерико Арданаз; Хулио Гаго; Роджер Грамунт; Исаак Эрнандес; Тони Хуан; Джоэл Эмер ; Стивен Феликс; Джефф Лоуни; Мэтью Маттина; Андре Сезнец (2002). «Тарантул: векторное расширение альфа-архитектуры» . В Даниэль К. Мартин (ред.). Материалы: 29-й ежегодный международный симпозиум по компьютерной архитектуре (ISCA '02) . 29-й ежегодный международный симпозиум по компьютерной архитектуре (ISCA '02) . Джо Дэйгл/Studio Productions. Лос Аламитос, Калифорния: Компьютерное общество IEEE. стр. 281–292. дои : 10.1109/ISCA.2002.1003586 . ISBN 0-7695-1605-Х . Архивировано из оригинала 4 октября 2007 г. Проверено 4 октября 2007 г.

- ^ «Вакс-вакуум» .

... с юридической точки зрения, если бы DEC до этого использовала VAX в США ..... «разумному человеку» не составит труда провести различие между этими двумя видами использования.

- ^ «Альфа AXP, часть 8: Доступ к памяти, хранение байтов, слов и невыровненных данных» . 16 августа 2017 г. Проверено 18 июля 2022 г.

Работа с невыровненной памятью на Alpha AXP очень раздражает.

- ^ «Технические данные микропроцессора Alpha 21264» (PDF) . Архивировано (PDF) из оригинала 30 августа 2017 г. Проверено 20 сентября 2018 г.

Инструкции, составляющие расширение BWX,...

- ^ «Инструкция МИПС» .

DEC Alpha ... , нет целочисленного кода условия.

[ постоянная мертвая ссылка ] - ^ «Альфа-биты – миграция в будущее». ДЭК Профессионал . Август 1992. с. 62.

Плавающие типы данных H недоступны в Alpha.

- ^ «Миграция приложения с OpenVMS VAX на OpenVMS Alpha» . 2.5.2 Типы данных.

- ^ Гроновски, ЧП; Боухилл, штат Вашингтон; Дончин, Д.Р.; Блейк-Кампос, РП; Карлсон, Д.А.; Экви, скорая помощь; Лафлин, Би Джей; Мехта, С.; Мюллер, Р.О.; Олесин А.; Нурлаг, DJW; Престон, Р.П. (1996). «Счетверенный RISC-микропроцессор с частотой 433 МГц, 64 бита». Журнал IEEE твердотельных схем . 31 (11): 1687–1696. Бибкод : 1996IJSSC..31.1687G . дои : 10.1109/JSSC.1996.542313 . S2CID 39280205 .

- ↑ Гвеннап, Линли (18 ноября 1996 г.). «Цифровые, MIPS добавляют мультимедийные расширения». Отчет микропроцессора .

- ^ Луис Андре Баррозу; Курош Гарачорлоо; Роберт Макнамара; Андреас Новачик; Шаз Кадир; Бартон Сано; Скотт Смит; Роберт Стетс; Бен Вергезе (2000). Piranha: масштабируемая архитектура, основанная на однокристальной многопроцессорной обработке . 27-й ежегодный международный симпозиум по компьютерной архитектуре. дои : 10.1145/339647.339696 .

- ^ Хун-Шэн Цао (29 октября 2011 г.). «SW1600 и Альфа 21164» . Блог ЛаоЦао . Проверено 29 октября 2011 г.

- ^ Донгарра, Джек (20 июня 2016 г.). «Отчет о системе Sunway TaihuLight» (PDF) . www.netlib.org . Проверено 20 июня 2016 г.

- ^ Дэвид Мосбергер. «Обзор семьи Альфа» . Архивировано из оригинала 20 января 2009 года . Проверено 9 декабря 2009 г.

- ^ Рейнхардт Краузе. «DEC запускает кампанию Alpha Board» . Электронные новости, 4 апреля 1994 г.

- ^ Национальные лаборатории Лос-Аламоса (2002). «Система ASCI Q: возможности 30 TeraOPS в Национальной лаборатории Лос-Аламоса» (PDF) . Архивировано из оригинала (PDF) 12 января 2011 г. Проверено 6 июня 2010 г.

Внешние ссылки

[ редактировать ]- Справочник по архитектуре Alpha, версия 4

- Справочник по архитектуре Alpha, версия 3

- Цифровой технический журнал, том 4, номер 4, специальный выпуск 1992 г. Alpha AXP Architecture and Systems. Архивировано 23 января 2023 г. в Wayback Machine. Этот выпуск содержит несколько статей Alpha's Architects.

- Архивная библиотека технической документации. По этой ссылке можно найти справочные руководства по аппаратному обеспечению и технические описания для микропроцессоров Alpha, наборов микросхем и материнских плат OEM. Включает справочник Alpha Architecture и различные руководства по программированию.

- Разговор с Дэном Добберпулом (1 октября 2003 г.)

- Конспекты лекций доктора Брюса Хаттона по компьютерной архитектуре