Семейство архитектуры ARM

| |

| Дизайнер | |

|---|---|

| Биты | 32-bit , 64-bit |

| Представлено | 1985 год |

| Дизайн | РИСК |

| Тип | Загрузка-сохранение |

| Ветвление | Код состояния , сравнение и ветвление |

| Открыть | Собственный |

| Introduced | 2011 |

|---|---|

| Version | ARMv8-R, ARMv8-A, ARMv8.1-A, ARMv8.2-A, ARMv8.3-A, ARMv8.4-A, ARMv8.5-A, ARMv8.6-A, ARMv8.7-A, ARMv8.8-A, ARMv8.9-A, ARMv9.0-A, ARMv9.1-A, ARMv9.2-A, ARMv9.3-A, ARMv9.4-A |

| Encoding | AArch64/A64 and AArch32/A32 use 32-bit instructions, AArch32/T32 (Thumb-2) uses mixed 16- and 32-bit instructions[1] |

| Endianness | Bi (little as default) |

| Extensions | SVE, SVE2, SME, AES, SHA, TME; All mandatory: Thumb-2, Neon, VFPv4-D16, VFPv4; obsolete: Jazelle |

| Registers | |

| General-purpose | 31 × 64-bit integer registers[1] |

| Floating point | 32 × 128-bit registers[1] for scalar 32- and 64-bit FP or SIMD FP or integer; or cryptography |

| Version | ARMv9-R, ARMv9-M, ARMv8-R, ARMv8-M, ARMv7-A, ARMv7-R, ARMv7E-M, ARMv7-M, ARMv6-M |

|---|---|

| Encoding | 32-bit, except Thumb-2 extensions use mixed 16- and 32-bit instructions. |

| Endianness | Bi (little as default) |

| Extensions | Thumb-2, Neon, Jazelle, AES, SHA, DSP, Saturated, FPv4-SP, FPv5, Helium |

| Registers | |

| General-purpose | 15 × 32-bit integer registers, including R14 (link register), but not R15 (PC) |

| Floating point | Up to 32 × 64-bit registers,[2] SIMD/floating-point (optional) |

| Version | ARMv6, ARMv5, ARMv4T, ARMv3, ARMv2 |

|---|---|

| Encoding | 32-bit, except Thumb extension uses mixed 16- and 32-bit instructions. |

| Endianness | Bi (little as default) in ARMv3 and above |

| Extensions | Thumb, Jazelle |

| Registers | |

| General-purpose | 15 × 32-bit integer registers, including R14 (link register), but not R15 (PC, 26-bit addressing in older) |

| Floating point | None |

ARM (стилизованное в нижнем регистре как «arm» , ранее аббревиатура от Advanced RISC Machines и первоначально Acorn RISC Machine ) — это семейство RISC архитектур набора команд (ISA) для компьютерных процессоров . Arm Ltd. разрабатывает ISA и лицензирует их другим компаниям, которые создают физические устройства, использующие этот набор команд. Он также разрабатывает и лицензирует ядра , реализующие эти ISA.

Благодаря низкой стоимости, низкому энергопотреблению и низкому выделению тепла процессоры ARM полезны для легких портативных устройств с батарейным питанием, включая смартфоны , ноутбуки и планшетные компьютеры , а также встраиваемых систем . [ 3 ] [ 4 ] [ 5 ] Однако процессоры ARM также используются для настольных компьютеров и серверов , включая самый быстрый в мире суперкомпьютер ( Fugaku ) 2020 года. [ 6 ] до 2022 года. Произведено более 230 миллиардов чипов ARM, [ 7 ] [ 8 ] [ 9 ] по состоянию на 2022 год [update]ARM — наиболее широко используемое семейство архитектур набора команд. [ 10 ] [ 4 ] [ 11 ] [ 12 ] [ 13 ]

There have been several generations of the ARM design. The original ARM1 used a 32-bit internal structure but had a 26-bit address space that limited it to 64 MB of main memory. This limitation was removed in the ARMv3 series, which has a 32-bit address space, and several additional generations up to ARMv7 remained 32-bit. Released in 2011, the ARMv8-A architecture added support for a 64-bit address space and 64-bit arithmetic with its new 32-bit fixed-length instruction set.[14] Arm Ltd. has also released a series of additional instruction sets for different rules; the "Thumb" extension adds both 32- and 16-bit instructions for improved code density, while Jazelle added instructions for directly handling Java bytecode. More recent changes include the addition of simultaneous multithreading (SMT) for improved performance or fault tolerance.[15]

History

[edit]BBC Micro

[edit]Acorn Computers' first widely successful design was the BBC Micro, introduced in December 1981. This was a relatively conventional machine based on the MOS Technology 6502 CPU but ran at roughly double the performance of competing designs like the Apple II due to its use of faster dynamic random-access memory (DRAM). Typical DRAM of the era ran at about 2 MHz; Acorn arranged a deal with Hitachi for a supply of faster 4 MHz parts.[16]

Machines of the era generally shared memory between the processor and the framebuffer, which allowed the processor to quickly update the contents of the screen without having to perform separate input/output (I/O). As the timing of the video display is exacting, the video hardware had to have priority access to that memory. Due to a quirk of the 6502's design, the CPU left the memory untouched for half of the time. Thus by running the CPU at 1 MHz, the video system could read data during those down times, taking up the total 2 MHz bandwidth of the RAM. In the BBC Micro, the use of 4 MHz RAM allowed the same technique to be used, but running at twice the speed. This allowed it to outperform any similar machine on the market.[17]

Acorn Business Computer

[edit]1981 was also the year that the IBM Personal Computer was introduced. Using the recently introduced Intel 8088, a 16-bit CPU compared to the 6502's 8-bit design, it offered higher overall performance. Its introduction changed the desktop computer market radically: what had been largely a hobby and gaming market emerging over the prior five years began to change to a must-have business tool where the earlier 8-bit designs simply could not compete. Even newer 32-bit designs were also coming to market, such as the Motorola 68000[18] and National Semiconductor NS32016.[19]

Acorn began considering how to compete in this market and produced a new paper design named the Acorn Business Computer. They set themselves the goal of producing a machine with ten times the performance of the BBC Micro, but at the same price.[20] This would outperform and underprice the PC. At the same time, the recent introduction of the Apple Lisa brought the graphical user interface (GUI) concept to a wider audience and suggested the future belonged to machines with a GUI.[21] The Lisa, however, cost $9,995, as it was packed with support chips, large amounts of memory, and a hard disk drive, all very expensive then.[22]

The engineers then began studying all of the CPU designs available. Their conclusion about the existing 16-bit designs was that they were a lot more expensive and were still "a bit crap",[23] offering only slightly higher performance than their BBC Micro design. They also almost always demanded a large number of support chips to operate even at that level, which drove up the cost of the computer as a whole. These systems would simply not hit the design goal.[23] They also considered the new 32-bit designs, but these cost even more and had the same issues with support chips.[24] According to Sophie Wilson, all the processors tested at that time performed about the same, with about a 4 Mbit/s bandwidth.[25][a]

Two key events led Acorn down the path to ARM. One was the publication of a series of reports from the University of California, Berkeley, which suggested that a simple chip design could nevertheless have extremely high performance, much higher than the latest 32-bit designs on the market.[26] The second was a visit by Steve Furber and Sophie Wilson to the Western Design Center, a company run by Bill Mensch and his sister, which had become the logical successor to the MOS team and was offering new versions like the WDC 65C02. The Acorn team saw high school students producing chip layouts on Apple II machines, which suggested that anyone could do it.[27][28] In contrast, a visit to another design firm working on modern 32-bit CPU revealed a team with over a dozen members who were already on revision H of their design and yet it still contained bugs.[b] This cemented their late 1983 decision to begin their own CPU design, the Acorn RISC Machine.[29]

Design concepts

[edit]The original Berkeley RISC designs were in some sense teaching systems, not designed specifically for outright performance. To the RISC's basic register-heavy and load/store concepts, ARM added a number of the well-received design notes of the 6502. Primary among them was the ability to quickly serve interrupts, which allowed the machines to offer reasonable input/output performance with no added external hardware. To offer interrupts with similar performance as the 6502, the ARM design limited its physical address space to 64 MB of total addressable space, requiring 26 bits of address. As instructions were 4 bytes (32 bits) long, and required to be aligned on 4-byte boundaries, the lower 2 bits of an instruction address were always zero. This meant the program counter (PC) only needed to be 24 bits, allowing it to be stored along with the eight bit processor flags in a single 32-bit register. That meant that upon receiving an interrupt, the entire machine state could be saved in a single operation, whereas had the PC been a full 32-bit value, it would require separate operations to store the PC and the status flags. This decision halved the interrupt overhead.[30]

Another change, and among the most important in terms of practical real-world performance, was the modification of the instruction set to take advantage of page mode DRAM. Recently introduced, page mode allowed subsequent accesses of memory to run twice as fast if they were roughly in the same location, or "page", in the DRAM chip. Berkeley's design did not consider page mode and treated all memory equally. The ARM design added special vector-like memory access instructions, the "S-cycles", that could be used to fill or save multiple registers in a single page using page mode. This doubled memory performance when they could be used, and was especially important for graphics performance.[31]

The Berkeley RISC designs used register windows to reduce the number of register saves and restores performed in procedure calls; the ARM design did not adopt this.

Wilson developed the instruction set, writing a simulation of the processor in BBC BASIC that ran on a BBC Micro with a second 6502 processor.[32][33] This convinced Acorn engineers they were on the right track. Wilson approached Acorn's CEO, Hermann Hauser, and requested more resources. Hauser gave his approval and assembled a small team to design the actual processor based on Wilson's ISA.[34] The official Acorn RISC Machine project started in October 1983.

ARM1

[edit]

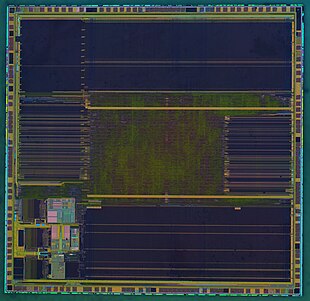

Acorn chose VLSI Technology as the "silicon partner", as they were a source of ROMs and custom chips for Acorn. Acorn provided the design and VLSI provided the layout and production. The first samples of ARM silicon worked properly when first received and tested on 26 April 1985.[3] Known as ARM1, these versions ran at 6 MHz.[35]

The first ARM application was as a second processor for the BBC Micro, where it helped in developing simulation software to finish development of the support chips (VIDC, IOC, MEMC), and sped up the CAD software used in ARM2 development. Wilson subsequently rewrote BBC BASIC in ARM assembly language. The in-depth knowledge gained from designing the instruction set enabled the code to be very dense, making ARM BBC BASIC an extremely good test for any ARM emulator.

ARM2

[edit]The result of the simulations on the ARM1 boards led to the late 1986 introduction of the ARM2 design running at 8 MHz, and the early 1987 speed-bumped version at 10 to 12 MHz.[c] A significant change in the underlying architecture was the addition of a Booth multiplier, whereas formerly multiplication had to be carried out in software.[37] Further, a new Fast Interrupt reQuest mode, FIQ for short, allowed registers 8 through 14 to be replaced as part of the interrupt itself. This meant FIQ requests did not have to save out their registers, further speeding interrupts.[38]

The first use of the ARM2 was the Acorn Archimedes personal computer models A305, A310, and A440 launched in 1987.

According to the Dhrystone benchmark, the ARM2 was roughly seven times the performance of a typical 7 MHz 68000-based system like the Amiga or Macintosh SE. It was twice as fast as an Intel 80386 running at 16 MHz, and about the same speed as a multi-processor VAX-11/784 superminicomputer. The only systems that beat it were the Sun SPARC and MIPS R2000 RISC-based workstations.[39] Further, as the CPU was designed for high-speed I/O, it dispensed with many of the support chips seen in these machines; notably, it lacked any dedicated direct memory access (DMA) controller which was often found on workstations. The graphics system was also simplified based on the same set of underlying assumptions about memory and timing. The result was a dramatically simplified design, offering performance on par with expensive workstations but at a price point similar to contemporary desktops.[39]

The ARM2 featured a 32-bit data bus, 26-bit address space and 27 32-bit registers, of which 16 are accessible at any one time (including the PC).[40] The ARM2 had a transistor count of just 30,000,[41] compared to Motorola's six-year-older 68000 model with around 68,000. Much of this simplicity came from the lack of microcode, which represents about one-quarter to one-third of the 68000's transistors, and the lack of (like most CPUs of the day) a cache. This simplicity enabled the ARM2 to have a low power consumption and simpler thermal packaging, through having fewer powered transistors, yet offering better performance than the contemporary, 1987, the IBM PS/2 Model 50, which initially utilised an Intel 80286, offering 1.8 MIPS @ 10 MHz, and later in 1987, the 2 MIPS of the PS/2 70, with its Intel 386 DX @ 16 MHz.[42][43]

A successor, ARM3, was produced with a 4 KB cache, which further improved performance.[44] The address bus was extended to 32 bits in the ARM6, but program code still had to lie within the first 64 MB of memory in 26-bit compatibility mode, due to the reserved bits for the status flags.[45]

Advanced RISC Machines Ltd. – ARM6

[edit]

In the late 1980s, Apple Computer and VLSI Technology started working with Acorn on newer versions of the ARM core. In 1990, Acorn spun off the design team into a new company named Advanced RISC Machines Ltd.,[46][47][48] which became ARM Ltd. when its parent company, Arm Holdings plc, floated on the London Stock Exchange and Nasdaq in 1998.[49] The new Apple–ARM work would eventually evolve into the ARM6, first released in early 1992. Apple used the ARM6-based ARM610 as the basis for their Apple Newton PDA.

Early licensees

[edit]In 1994, Acorn used the ARM610 as the main central processing unit (CPU) in their RiscPC computers. DEC licensed the ARMv4 architecture and produced the StrongARM.[50] At 233 MHz, this CPU drew only one watt (newer versions draw far less). This work was later passed to Intel as part of a lawsuit settlement, and Intel took the opportunity to supplement their i960 line with the StrongARM. Intel later developed its own high performance implementation named XScale, which it has since sold to Marvell. Transistor count of the ARM core remained essentially the same throughout these changes; ARM2 had 30,000 transistors,[51] while ARM6 grew only to 35,000.[52]

Market share

[edit]In 2005, about 98% of all mobile phones sold used at least one ARM processor.[53] In 2010, producers of chips based on ARM architectures reported shipments of 6.1 billion ARM-based processors, representing 95% of smartphones, 35% of digital televisions and set-top boxes, and 10% of mobile computers. In 2011, the 32-bit ARM architecture was the most widely used architecture in mobile devices and the most popular 32-bit one in embedded systems.[54] In 2013, 10 billion were produced[55] and "ARM-based chips are found in nearly 60 percent of the world's mobile devices".[56]

Licensing

[edit]

Core licence

[edit]Arm Ltd.'s primary business is selling IP cores, which licensees use to create microcontrollers (MCUs), CPUs, and systems-on-chips based on those cores. The original design manufacturer combines the ARM core with other parts to produce a complete device, typically one that can be built in existing semiconductor fabrication plants (fabs) at low cost and still deliver substantial performance. The most successful implementation has been the ARM7TDMI with hundreds of millions sold. Atmel has been a precursor design center in the ARM7TDMI-based embedded system.

The ARM architectures used in smartphones, PDAs and other mobile devices range from ARMv5 to ARMv8-A.

In 2009, some manufacturers introduced netbooks based on ARM architecture CPUs, in direct competition with netbooks based on Intel Atom.[57]

Arm Ltd. offers a variety of licensing terms, varying in cost and deliverables. Arm Ltd. provides to all licensees an integratable hardware description of the ARM core as well as complete software development toolset (compiler, debugger, software development kit), and the right to sell manufactured silicon containing the ARM CPU.

SoC packages integrating ARM's core designs include Nvidia Tegra's first three generations, CSR plc's Quatro family, ST-Ericsson's Nova and NovaThor, Silicon Labs's Precision32 MCU, Texas Instruments's OMAP products, Samsung's Hummingbird and Exynos products, Apple's A4, A5, and A5X, and NXP's i.MX.

Fabless licensees, who wish to integrate an ARM core into their own chip design, are usually only interested in acquiring a ready-to-manufacture verified semiconductor intellectual property core. For these customers, Arm Ltd. delivers a gate netlist description of the chosen ARM core, along with an abstracted simulation model and test programs to aid design integration and verification. More ambitious customers, including integrated device manufacturers (IDM) and foundry operators, choose to acquire the processor IP in synthesizable RTL (Verilog) form. With the synthesizable RTL, the customer has the ability to perform architectural level optimisations and extensions. This allows the designer to achieve exotic design goals not otherwise possible with an unmodified netlist (high clock speed, very low power consumption, instruction set extensions, etc.). While Arm Ltd. does not grant the licensee the right to resell the ARM architecture itself, licensees may freely sell manufactured products such as chip devices, evaluation boards and complete systems. Merchant foundries can be a special case; not only are they allowed to sell finished silicon containing ARM cores, they generally hold the right to re-manufacture ARM cores for other customers.

Arm Ltd. prices its IP based on perceived value. Lower performing ARM cores typically have lower licence costs than higher performing cores. In implementation terms, a synthesisable core costs more than a hard macro (blackbox) core. Complicating price matters, a merchant foundry that holds an ARM licence, such as Samsung or Fujitsu, can offer fab customers reduced licensing costs. In exchange for acquiring the ARM core through the foundry's in-house design services, the customer can reduce or eliminate payment of ARM's upfront licence fee.

Compared to dedicated semiconductor foundries (such as TSMC and UMC) without in-house design services, Fujitsu/Samsung charge two- to three-times more per manufactured wafer.[citation needed] For low to mid volume applications, a design service foundry offers lower overall pricing (through subsidisation of the licence fee). For high volume mass-produced parts, the long term cost reduction achievable through lower wafer pricing reduces the impact of ARM's NRE (non-recurring engineering) costs, making the dedicated foundry a better choice.

Companies that have developed chips with cores designed by Arm include Amazon.com's Annapurna Labs subsidiary,[58] Analog Devices, Apple, AppliedMicro (now: MACOM Technology Solutions[59]), Atmel, Broadcom, Cavium, Cypress Semiconductor, Freescale Semiconductor (now NXP Semiconductors), Huawei, Intel,[dubious – discuss] Maxim Integrated, Nvidia, NXP, Qualcomm, Renesas, Samsung Electronics, ST Microelectronics, Texas Instruments, and Xilinx.

Built on ARM Cortex Technology licence

[edit]In February 2016, ARM announced the Built on ARM Cortex Technology licence, often shortened to Built on Cortex (BoC) licence. This licence allows companies to partner with ARM and make modifications to ARM Cortex designs. These design modifications will not be shared with other companies. These semi-custom core designs also have brand freedom, for example Kryo 280.

Companies that are current licensees of Built on ARM Cortex Technology include Qualcomm.[60]

Architectural licence

[edit]Companies can also obtain an ARM architectural licence for designing their own CPU cores using the ARM instruction sets. These cores must comply fully with the ARM architecture. Companies that have designed cores that implement an ARM architecture include Apple, AppliedMicro (now: Ampere Computing), Broadcom, Cavium (now: Marvell), Digital Equipment Corporation, Intel, Nvidia, Qualcomm, Samsung Electronics, Fujitsu, and NUVIA Inc. (acquired by Qualcomm in 2021).

ARM Flexible Access

[edit]On 16 July 2019, ARM announced ARM Flexible Access. ARM Flexible Access provides unlimited access to included ARM intellectual property (IP) for development. Per product licence fees are required once a customer reaches foundry tapeout or prototyping.[61][62]

75% of ARM's most recent IP over the last two years are included in ARM Flexible Access. As of October 2019:

- CPUs: Cortex-A5, Cortex-A7, Cortex-A32, Cortex-A34, Cortex-A35, Cortex-A53, Cortex-R5, Cortex-R8, Cortex-R52, Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33

- GPUs: Mali-G52, Mali-G31. Includes Mali Driver Development Kits (DDK).

- Interconnect: CoreLink NIC-400, CoreLink NIC-450, CoreLink CCI-400, CoreLink CCI-500, CoreLink CCI-550, ADB-400 AMBA, XHB-400 AXI-AHB

- System Controllers: CoreLink GIC-400, CoreLink GIC-500, PL192 VIC, BP141 TrustZone Memory Wrapper, CoreLink TZC-400, CoreLink L2C-310, CoreLink MMU-500, BP140 Memory Interface

- Security IP: CryptoCell-312, CryptoCell-712, TrustZone True Random Number Generator

- Peripheral Controllers: PL011 UART, PL022 SPI, PL031 RTC

- Debug & Trace: CoreSight SoC-400, CoreSight SDC-600, CoreSight STM-500, CoreSight System Trace Macrocell, CoreSight Trace Memory Controller

- Design Kits: Corstone-101, Corstone-201

- Physical IP: Artisan PIK for Cortex-M33 TSMC 22ULL including memory compilers, logic libraries, GPIOs and documentation

- Tools & Materials: Socrates IP ToolingARM Design Studio, Virtual System Models

- Support: Standard ARM Technical support, ARM online training, maintenance updates, credits toward onsite training and design reviews

Cores

[edit]| Architecture | Core bit-width |

Cores | Profile | Refe- rences | |

|---|---|---|---|---|---|

| Arm Ltd. | Third-party | ||||

ARMv1 |

ARM1 | Classic |

|||

ARMv2 |

32 |

ARM2, ARM250, ARM3 | Amber, STORM Open Soft Core[63] | Classic |

|

ARMv3 |

32 |

ARM6, ARM7 | Classic |

||

ARMv4 |

32 |

ARM8 | StrongARM, FA526, ZAP Open Source Processor Core | Classic |

|

ARMv4T |

32 |

ARM7TDMI, ARM9TDMI, SecurCore SC100 | Classic |

||

ARMv5TE |

32 |

ARM7EJ, ARM9E, ARM10E | XScale, FA626TE, Feroceon, PJ1/Mohawk | Classic |

|

ARMv6 |

32 |

ARM11 | Classic |

||

ARMv6-M |

32 |

ARM Cortex-M0, ARM Cortex-M0+, ARM Cortex-M1, SecurCore SC000 | |||

ARMv7-M |

32 |

ARM Cortex-M3, SecurCore SC300 | Apple M7 motion coprocessor | Microcontroller |

|

ARMv7E-M |

32 |

ARM Cortex-M4, ARM Cortex-M7 | Microcontroller |

||

ARMv8-M |

32 |

ARM Cortex-M23,[65] ARM Cortex-M33[66] | Microcontroller |

||

ARMv8.1-M

|

32

|

ARM Cortex-M55, ARM Cortex-M85 | Microcontroller

|

||

ARMv7-R |

32 |

ARM Cortex-R4, ARM Cortex-R5, ARM Cortex-R7, ARM Cortex-R8 | |||

ARMv8-R |

32 |

ARM Cortex-R52 | Real-time |

||

64

|

ARM Cortex-R82 | Real-time

|

|||

ARMv7-A |

32 |

ARM Cortex-A5, ARM Cortex-A7, ARM Cortex-A8, ARM Cortex-A9, ARM Cortex-A12, ARM Cortex-A15, ARM Cortex-A17 | Qualcomm Scorpion/Krait, PJ4/Sheeva, Apple Swift (A6, A6X) | ||

ARMv8-A |

32 |

ARM Cortex-A32[72] | Application |

||

64/32 |

ARM Cortex-A35,[73] ARM Cortex-A53, ARM Cortex-A57,[74] ARM Cortex-A72,[75] ARM Cortex-A73[76] | X-Gene, Nvidia Denver 1/2, Cavium ThunderX, AMD K12, Apple Cyclone (A7)/Typhoon (A8, A8X)/Twister (A9, A9X)/Hurricane+Zephyr (A10, A10X), Qualcomm Kryo, Samsung M1/M2 ("Mongoose") /M3 ("Meerkat") | Application |

||

| ARM Cortex-A34[82] | Application

|

||||

ARMv8.1-A |

64/32 |

TBA | Cavium ThunderX2 | Application |

|

ARMv8.2-A |

64/32 |

ARM Cortex-A55,[84] ARM Cortex-A75,[85] ARM Cortex-A76,[86] ARM Cortex-A77, ARM Cortex-A78, ARM Cortex-X1, ARM Neoverse N1 | Nvidia Carmel, Samsung M4 ("Cheetah"), Fujitsu A64FX (ARMv8 SVE 512-bit) | Application |

|

64 |

ARM Cortex-A65, ARM Neoverse E1 with simultaneous multithreading (SMT), ARM Cortex-A65AE[90] (also having e.g. ARMv8.4 Dot Product; made for safety critical tasks such as advanced driver-assistance systems (ADAS)) | Apple Monsoon+Mistral (A11) (September 2017) | Application |

||

ARMv8.3-A

|

64/32 |

TBA | Application

|

||

64 |

TBA | Apple Vortex+Tempest (A12, A12X, A12Z), Marvell ThunderX3 (v8.3+)[91] | Application |

||

ARMv8.4-A |

64/32 |

TBA | Application |

||

64 |

ARM Neoverse V1 | Apple Lightning+Thunder (A13), Apple Firestorm+Icestorm (A14, M1) | Application |

||

ARMv8.5-A

|

64/32 |

TBA | Application

|

||

64 |

TBA | Application

|

|||

ARMv8.6-A

|

64 |

TBA | Apple Avalanche+Blizzard (A15, M2), Apple Everest+Sawtooth (A16)[92] | Application

|

|

ARMv8.7-A

|

64 |

TBA | Application

|

||

ARMv8.8-A

|

64

|

TBA | Application

|

||

ARMv8.9-A

|

64

|

TBA | Application

|

||

ARMv9.0-A

|

64

|

ARM Cortex-A510, ARM Cortex-A710, ARM Cortex-A715, ARM Cortex-X2, ARM Cortex-X3, ARM Neoverse E2, ARM Neoverse N2, ARM Neoverse V2 | Application

|

||

ARMv9.1-A

|

64

|

TBA | Application

|

||

ARMv9.2-A

|

64

|

ARM Cortex-A520, ARM Cortex-A720, ARM Cortex-X4 | Apple M4[96] | Application

|

|

ARMv9.3-A

|

64

|

TBA | Application

|

||

ARMv9.4-A

|

64

|

TBA | Application

|

||

- ^ Jump up to: a b Although most datapaths and CPU registers in the early ARM processors were 32-bit, addressable memory was limited to 26 bits; with upper bits, then, used for status flags in the program counter register.

- ^ Jump up to: a b c ARMv3 included a compatibility mode to support the 26-bit addresses of earlier versions of the architecture. This compatibility mode optional in ARMv4, and removed entirely in ARMv5.

Arm provides a list of vendors who implement ARM cores in their design (application specific standard products (ASSP), microprocessor and microcontrollers).[99]

Example applications of ARM cores

[edit]

ARM cores are used in a number of products, particularly PDAs and smartphones. Some computing examples are Microsoft's first generation Surface, Surface 2 and Pocket PC devices (following 2002), Apple's iPads, and Asus's Eee Pad Transformer tablet computers, and several Chromebook laptops. Others include Apple's iPhone smartphones and iPod portable media players, Canon PowerShot digital cameras, Nintendo Switch hybrid, the Wii security processor and 3DS handheld game consoles, and TomTom turn-by-turn navigation systems.

In 2005, Arm took part in the development of Manchester University's computer SpiNNaker, which used ARM cores to simulate the human brain.[100]

ARM chips are also used in Raspberry Pi, BeagleBoard, BeagleBone, PandaBoard, and other single-board computers, because they are very small, inexpensive, and consume very little power.

32-bit architecture

[edit]

The 32-bit ARM architecture (ARM32), such as ARMv7-A (implementing AArch32; see section on Armv8-A for more on it), was the most widely used architecture in mobile devices as of 2011[update].[54]

Since 1995, various versions of the ARM Architecture Reference Manual (see § External links) have been the primary source of documentation on the ARM processor architecture and instruction set, distinguishing interfaces that all ARM processors are required to support (such as instruction semantics) from implementation details that may vary. The architecture has evolved over time, and version seven of the architecture, ARMv7, defines three architecture "profiles":

- A-profile, the "Application" profile, implemented by 32-bit cores in the Cortex-A series and by some non-ARM cores

- R-profile, the "Real-time" profile, implemented by cores in the Cortex-R series

- M-profile, the "Microcontroller" profile, implemented by most cores in the Cortex-M series

Although the architecture profiles were first defined for ARMv7, ARM subsequently defined the ARMv6-M architecture (used by the Cortex M0/M0+/M1) as a subset of the ARMv7-M profile with fewer instructions.

CPU modes

[edit]Except in the M-profile, the 32-bit ARM architecture specifies several CPU modes, depending on the implemented architecture features. At any moment in time, the CPU can be in only one mode, but it can switch modes due to external events (interrupts) or programmatically.[101]

- User mode: The only non-privileged mode.

- FIQ mode: A privileged mode that is entered whenever the processor accepts a fast interrupt request.

- IRQ mode: A privileged mode that is entered whenever the processor accepts an interrupt.

- Supervisor (svc) mode: A privileged mode entered whenever the CPU is reset or when an SVC instruction is executed.

- Abort mode: A privileged mode that is entered whenever a prefetch abort or data abort exception occurs.

- Undefined mode: A privileged mode that is entered whenever an undefined instruction exception occurs.

- System mode (ARMv4 and above): The only privileged mode that is not entered by an exception. It can only be entered by executing an instruction that explicitly writes to the mode bits of the Current Program Status Register (CPSR) from another privileged mode (not from user mode).

- Monitor mode (ARMv6 and ARMv7 Security Extensions, ARMv8 EL3): A monitor mode is introduced to support TrustZone extension in ARM cores.

- Hyp mode (ARMv7 Virtualization Extensions, ARMv8 EL2): A hypervisor mode that supports Popek and Goldberg virtualization requirements for the non-secure operation of the CPU.[102][103]

- Thread mode (ARMv6-M, ARMv7-M, ARMv8-M): A mode which can be specified as either privileged or unprivileged. Whether the Main Stack Pointer (MSP) or Process Stack Pointer (PSP) is used can also be specified in CONTROL register with privileged access. This mode is designed for user tasks in RTOS environment but it is typically used in bare-metal for super-loop.

- Handler mode (ARMv6-M, ARMv7-M, ARMv8-M): A mode dedicated for exception handling (except the RESET which are handled in Thread mode). Handler mode always uses MSP and works in privileged level.

Instruction set

[edit]The original (and subsequent) ARM implementation was hardwired without microcode, like the much simpler 8-bit 6502 processor used in prior Acorn microcomputers.

The 32-bit ARM architecture (and the 64-bit architecture for the most part) includes the following RISC features:

- Load–store architecture.

- No support for unaligned memory accesses in the original version of the architecture. ARMv6 and later, except some microcontroller versions, support unaligned accesses for half-word and single-word load/store instructions with some limitations, such as no guaranteed atomicity.[104][105]

- Uniform 16 × 32-bit register file (including the program counter, stack pointer and the link register).

- Fixed instruction width of 32 bits to ease decoding and pipelining, at the cost of decreased code density. Later, the Thumb instruction set added 16-bit instructions and increased code density.

- Mostly single clock-cycle execution.

To compensate for the simpler design, compared with processors like the Intel 80286 and Motorola 68020, some additional design features were used:

- Conditional execution of most instructions reduces branch overhead and compensates for the lack of a branch predictor in early chips.

- Arithmetic instructions alter condition codes only when desired.

- 32-bit barrel shifter can be used without performance penalty with most arithmetic instructions and address calculations.

- Has powerful indexed addressing modes.

- A link register supports fast leaf function calls.

- A simple, but fast, 2-priority-level interrupt subsystem has switched register banks.

Arithmetic instructions

[edit]ARM includes integer arithmetic operations for add, subtract, and multiply; some versions of the architecture also support divide operations.

ARM supports 32-bit × 32-bit multiplies with either a 32-bit result or 64-bit result, though Cortex-M0 / M0+ / M1 cores do not support 64-bit results.[106] Some ARM cores also support 16-bit × 16-bit and 32-bit × 16-bit multiplies.

The divide instructions are only included in the following ARM architectures:

- Armv7-M and Armv7E-M architectures always include divide instructions.[107]

- Armv7-R architecture always includes divide instructions in the Thumb instruction set, but optionally in its 32-bit instruction set.[108]

- Armv7-A architecture optionally includes the divide instructions. The instructions might not be implemented, or implemented only in the Thumb instruction set, or implemented in both the Thumb and ARM instruction sets, or implemented if the Virtualization Extensions are included.[108]

Registers

[edit]| usr | sys | svc | abt | und | irq | fiq |

|---|---|---|---|---|---|---|

| R0 | ||||||

| R1 | ||||||

| R2 | ||||||

| R3 | ||||||

| R4 | ||||||

| R5 | ||||||

| R6 | ||||||

| R7 | ||||||

| R8 | R8_fiq | |||||

| R9 | R9_fiq | |||||

| R10 | R10_fiq | |||||

| R11 | R11_fiq | |||||

| R12 | R12_fiq | |||||

| R13 | R13_svc | R13_abt | R13_und | R13_irq | R13_fiq | |

| R14 | R14_svc | R14_abt | R14_und | R14_irq | R14_fiq | |

| R15 | ||||||

| CPSR | ||||||

| SPSR_svc | SPSR_abt | SPSR_und | SPSR_irq | SPSR_fiq | ||

Registers R0 through R7 are the same across all CPU modes; they are never banked.

Registers R8 through R12 are the same across all CPU modes except FIQ mode. FIQ mode has its own distinct R8 through R12 registers.

R13 and R14 are banked across all privileged CPU modes except system mode. That is, each mode that can be entered because of an exception has its own R13 and R14. These registers generally contain the stack pointer and the return address from function calls, respectively.

Aliases:

- R13 is also referred to as SP, the stack pointer.

- R14 is also referred to as LR, the link register.

- R15 is also referred to as PC, the program counter.

The Current Program Status Register (CPSR) has the following 32 bits.[109]

- M (bits 0–4) is the processor mode bits.

- T (bit 5) is the Thumb state bit.

- F (bit 6) is the FIQ disable bit.

- I (bit 7) is the IRQ disable bit.

- A (bit 8) is the imprecise data abort disable bit.

- E (bit 9) is the data endianness bit.

- IT (bits 10–15 and 25–26) is the if-then state bits.

- GE (bits 16–19) is the greater-than-or-equal-to bits.

- DNM (bits 20–23) is the do not modify bits.

- J (bit 24) is the Java state bit.

- Q (bit 27) is the sticky overflow bit.

- V (bit 28) is the overflow bit.

- C (bit 29) is the carry/borrow/extend bit.

- Z (bit 30) is the zero bit.

- N (bit 31) is the negative/less than bit.

Conditional execution

[edit]Almost every ARM instruction has a conditional execution feature called predication, which is implemented with a 4-bit condition code selector (the predicate). To allow for unconditional execution, one of the four-bit codes causes the instruction to be always executed. Most other CPU architectures only have condition codes on branch instructions.[110]

Though the predicate takes up four of the 32 bits in an instruction code, and thus cuts down significantly on the encoding bits available for displacements in memory access instructions, it avoids branch instructions when generating code for small if statements. Apart from eliminating the branch instructions themselves, this preserves the fetch/decode/execute pipeline at the cost of only one cycle per skipped instruction.

An algorithm that provides a good example of conditional execution is the subtraction-based Euclidean algorithm for computing the greatest common divisor. In the C programming language, the algorithm can be written as:

int gcd(int a, int b) {

while (a != b) // We enter the loop when a < b or a > b, but not when a == b

if (a > b) // When a > b we do this

a -= b;

else // When a < b we do that (no "if (a < b)" needed since a != b is checked in while condition)

b -= a;

return a;

}

The same algorithm can be rewritten in a way closer to target ARM instructions as:

loop:

// Compare a and b

GT = a > b;

LT = a < b;

NE = a != b;

// Perform operations based on flag results

if (GT) a -= b; // Subtract *only* if greater-than

if (LT) b -= a; // Subtract *only* if less-than

if (NE) goto loop; // Loop *only* if compared values were not equal

return a;

and coded in assembly language as:

; assign a to register r0, b to r1

loop: CMP r0, r1 ; set condition "NE" if (a ≠ b),

; "GT" if (a > b),

; or "LT" if (a < b)

SUBGT r0, r0, r1 ; if "GT" (Greater Than), then a = a − b

SUBLT r1, r1, r0 ; if "LT" (Less Than), then b = b − a

BNE loop ; if "NE" (Not Equal), then loop

B lr ; return

which avoids the branches around the then and else clauses. If r0 and r1 are equal then neither of the SUB instructions will be executed, eliminating the need for a conditional branch to implement the while check at the top of the loop, for example had SUBLE (less than or equal) been used.

One of the ways that Thumb code provides a more dense encoding is to remove the four-bit selector from non-branch instructions.

Other features

[edit]Another feature of the instruction set is the ability to fold shifts and rotates into the data processing (arithmetic, logical, and register-register move) instructions, so that, for example, the statement in C language:

a += (j << 2);

could be rendered as a one-word, one-cycle instruction:[111]

ADD Ra, Ra, Rj, LSL #2

This results in the typical ARM program being denser than expected with fewer memory accesses; thus the pipeline is used more efficiently.

The ARM processor also has features rarely seen in other RISC architectures, such as PC-relative addressing (indeed, on the 32-bit[1] ARM the PC is one of its 16 registers) and pre- and post-increment addressing modes.

The ARM instruction set has increased over time. Some early ARM processors (before ARM7TDMI), for example, have no instruction to store a two-byte quantity.

Трубопроводы и другие вопросы реализации

[ редактировать ]ARM7 и более ранние реализации имеют трехэтапный конвейер ; этапы выборки, декодирования и выполнения. Конструкции с более высокой производительностью, такие как ARM9, имеют более глубокие конвейеры: Cortex-A8 имеет тринадцать этапов. Дополнительные изменения реализации для повышения производительности включают более быстрый сумматор и более обширную логику прогнозирования ветвей . Например, разница между ядрами ARM7DI и ARM7DMI заключалась в улучшенном множителе; отсюда и добавленная буква «М».

Сопроцессоры

[ редактировать ]Архитектура ARM (до Armv8) обеспечивает неинтрузивный способ расширения набора команд с помощью «сопроцессоров», к которым можно обращаться с помощью MCR, MRC, MRRC, MCRR и подобных инструкций. Пространство сопроцессора логически разделено на 16 сопроцессоров с номерами от 0 до 15, причем сопроцессор 15 (cp15) зарезервирован для некоторых типичных функций управления, таких как управление кэшами и операциями MMU на процессорах, у которых он есть.

В машинах на базе ARM периферийные устройства обычно подключаются к процессору путем сопоставления их физических регистров с пространством памяти ARM, с пространством сопроцессора или путем подключения к другому устройству (шине), которое, в свою очередь, подключается к процессору. Доступ к сопроцессору имеет меньшую задержку, поэтому некоторые периферийные устройства — например, контроллер прерываний XScale — доступны обоими способами: через память и через сопроцессоры.

В других случаях разработчики микросхем интегрируют аппаратное обеспечение только с помощью механизма сопроцессора. Например, механизм обработки изображений может представлять собой небольшое ядро ARM7TDMI в сочетании с сопроцессором, который выполняет специализированные операции для поддержки определенного набора примитивов транскодирования HDTV.

Отладка

[ редактировать ]Этот раздел нуждается в дополнительных цитатах для проверки . ( Март 2011 г. ) |

Все современные процессоры ARM включают средства аппаратной отладки, позволяющие отладчикам программного обеспечения выполнять такие операции, как остановка, пошаговое выполнение и точка останова кода, начиная с сброса. Эти средства построены с использованием поддержки JTAG , хотя некоторые новые ядра дополнительно поддерживают собственный двухпроводный протокол ARM «SWD». В ядрах ARM7TDMI буква «D» обозначала поддержку отладки JTAG, а «I» обозначала наличие модуля отладки «EmbeddedICE». Для поколений ядер ARM7 и ARM9 EmbeddedICE over JTAG был де-факто стандартом отладки, хотя и не гарантированным с архитектурной точки зрения.

Архитектура ARMv7 определяет базовые средства отладки на архитектурном уровне. К ним относятся точки останова, точки наблюдения и выполнение инструкций в «режиме отладки»; аналогичные возможности были также доступны во EmbeddedICE. Поддерживается отладка как в режиме «остановки», так и в режиме «мониторинга». Фактический транспортный механизм, используемый для доступа к средствам отладки, архитектурно не определен, но реализации обычно включают поддержку JTAG.

Существует отдельная архитектура отладки ARM «CoreSight», которая архитектурно не требуется процессорам ARMv7.

Порт доступа к отладке

[ редактировать ]Порт доступа к отладке (DAP) — это реализация интерфейса отладки ARM. [ 112 ] Существует две различные поддерживаемые реализации: последовательный порт отладки JTAG (SWJ-DP) и последовательный порт отладки проводов (SW-DP). [ 113 ] CMSIS-DAP — это стандартный интерфейс, который описывает, как различное программное обеспечение для отладки на главном ПК может взаимодействовать через USB с прошивкой, работающей на аппаратном отладчике, который, в свою очередь, обменивается данными через SWD или JTAG с процессором ARM Cortex с поддержкой CoreSight. [ 114 ] [ 115 ] [ 116 ]

Инструкции по расширению DSP

[ редактировать ]Чтобы улучшить архитектуру ARM для цифровой обработки сигналов и мультимедийных приложений, в набор команд были добавлены инструкции DSP. [ 117 ] Они обозначаются буквой «E» в названии архитектур ARMv5TE и ARMv5TEJ. E-варианты также подразумевают T, D, M и I.

Новые инструкции распространены в архитектурах процессоров цифровых сигналов (DSP). Они включают в себя вариации знакового умножения-накопления , насыщенного сложения и вычитания , а также подсчета ведущих нулей .

Впервые представленное в 1999 году, это расширение основного набора команд контрастировало с более ранним сопроцессором DSP ARM, известным как Piccolo, который использовал отдельный, несовместимый набор команд, выполнение которого включало отдельный программный счетчик. [ 118 ] В инструкциях Piccolo использовался отдельный файл регистров из шестнадцати 32-битных регистров, причем некоторые инструкции объединяли регистры для использования в качестве 48-битных аккумуляторов, а другие инструкции обращались к 16-битным полурегистрам. Некоторые инструкции могли работать с двумя такими 16-битными значениями параллельно. Связь с файлом регистров Piccolo включала загрузку в Piccolo и сохранение инструкций сопроцессора Piccolo через два буфера по восемь 32-битных записей. Описанный как напоминающий другие подходы, в частности SH-DSP от Hitachi и 68356 от Motorola, Piccolo не использовал выделенную локальную память и полагался на пропускную способность ядра ARM для извлечения операндов DSP, что влияло на одновременную производительность. [ 119 ] Особый набор инструкций Piccolo также оказался не «хорошей целью для компилятора». [ 118 ]

SIMD-расширения для мультимедиа

[ редактировать ]Представленный в архитектуре ARMv6, он был предшественником Advanced SIMD, также называемого Neon . [ 120 ]

Жазель

[ редактировать ]Jazelle DBX (Direct Bytecode eXecution) — это метод, который позволяет байт-код Java выполнять непосредственно в архитектуре ARM в качестве третьего состояния выполнения (и набора команд) наряду с существующими режимами ARM и Thumb. Поддержка этого состояния обозначается буквой «J» в архитектуре ARMv5TEJ, а также в именах ядер ARM9EJ-S и ARM7EJ-S. Поддержка этого состояния требуется начиная с ARMv6 (за исключением профиля ARMv7-M), хотя новые ядра включают только тривиальную реализацию, не обеспечивающую аппаратное ускорение.

Большой палец

[ редактировать ]Чтобы улучшить плотность компилируемого кода, процессоры, начиная с ARM7TDMI (выпущенного в 1994 г.), [ 121 ] ) представили Thumb сжатый набор команд , которые имеют собственное состояние. (Буква «T» в «TDMI» указывает на функцию Thumb.) В этом состоянии процессор выполняет набор инструкций Thumb, компактную 16-битную кодировку для подмножества набора команд ARM. [ 122 ] Большинство инструкций Thumb напрямую сопоставлены с обычными инструкциями ARM. Экономия места достигается за счет того, что некоторые операнды инструкций делаются неявными и ограничивают количество возможностей по сравнению с инструкциями ARM, выполняемыми в состоянии набора команд ARM.

В Thumb 16-битные коды операций имеют меньшую функциональность. Например, условными могут быть только переходы, а многие коды операций ограничены доступом только к половине всех регистров общего назначения ЦП. Более короткие коды операций в целом улучшают плотность кода, хотя некоторые операции требуют дополнительных инструкций. В ситуациях, когда ширина порта памяти или шины ограничена менее 32 битами, более короткие коды операций Thumb обеспечивают повышенную производительность по сравнению с 32-битным кодом ARM, поскольку в процессор может потребоваться загружать меньше программного кода из-за ограниченной полосы пропускания памяти.

В отличие от процессорных архитектур с инструкциями переменной длины (16 или 32 бита), таких как Cray-1 и Hitachi SuperH , наборы инструкций ARM и Thumb существуют независимо друг от друга. Встроенное оборудование, такое как Game Boy Advance , обычно имеет небольшой объем оперативной памяти, доступной с полным 32-битным каналом передачи данных; доступ к большинству осуществляется через 16-битный или более узкий вторичный канал данных. В этой ситуации обычно имеет смысл скомпилировать код Thumb и вручную оптимизировать несколько наиболее ресурсоемких разделов с использованием полных 32-битных инструкций ARM, помещая эти более широкие инструкции в память, доступную по 32-битной шине.

Первым процессором с декодером инструкций Thumb был ARM7TDMI. Все процессоры, поддерживающие 32-битные наборы инструкций, начиная с ARM9 и включая XScale, имеют декодер инструкций Thumb. Он включает в себя инструкции, заимствованные из Hitachi SuperH (1992), лицензированного ARM. [ 123 ] Самые маленькие семейства процессоров ARM (Cortex M0 и M1) реализуют только 16-битный набор инструкций Thumb для максимальной производительности в самых дешевых приложениях. Процессоры ARM, которые не поддерживают 32-битную адресацию, также не используют Thumb.

Большой палец-2

[ редактировать ]Технология Thumb-2 была представлена в ядре ARM1156 , анонсированном в 2003 году. Thumb-2 расширяет ограниченный 16-битный набор команд Thumb дополнительными 32-битными инструкциями, чтобы сделать набор команд более широким, создавая таким образом набор команд переменной длины. . Заявленная цель Thumb-2 заключалась в достижении плотности кода, аналогичной Thumb, с производительностью, аналогичной набору инструкций ARM в 32-битной памяти.

Thumb-2 расширяет набор команд Thumb манипуляциями с битовыми полями, ветвями таблиц и условным выполнением. В то же время набор инструкций ARM был расширен для обеспечения эквивалентной функциональности в обоих наборах инструкций. Новый «Унифицированный язык ассемблера» (UAL) поддерживает генерацию инструкций Thumb или ARM из одного и того же исходного кода; версии Thumb, используемые на процессорах ARMv7, по сути, обладают такими же возможностями, как и код ARM (включая возможность писать обработчики прерываний). Это требует некоторой осторожности и использования новой инструкции «IT» (если-то), которая позволяет выполнять до четырех последовательных инструкций на основе проверяемого условия или его обратного. При компиляции в код ARM это игнорируется, но при компиляции в Thumb генерируется реальная инструкция. Например:

; if (r0 == r1)

CMP r0, r1

ITE EQ ; ARM: no code ... Thumb: IT instruction

; then r0 = r2;

MOVEQ r0, r2 ; ARM: conditional; Thumb: condition via ITE 'T' (then)

; else r0 = r3;

MOVNE r0, r3 ; ARM: conditional; Thumb: condition via ITE 'E' (else)

; recall that the Thumb MOV instruction has no bits to encode "EQ" or "NE".

Все чипы ARMv7 поддерживают набор инструкций Thumb. Все чипы серии Cortex-A, поддерживающие ARMv7, все серии Cortex-R и все серии ARM11 поддерживают как «состояние набора команд ARM», так и «состояние набора команд Thumb», тогда как чипы серии Cortex-M поддерживают только Thumb. набор инструкций. [ 124 ] [ 125 ] [ 126 ]

Среда выполнения Thumb (ThumbEE)

[ редактировать ]ThumbEE (ошибочно называемый Thumb-2EE в некоторой документации ARM), который продавался как Jazelle RCT. [ 127 ] (Runtime Compilation Target), был анонсирован в 2005 году и устарел в 2011 году. Впервые он появился в процессоре Cortex-A8 . ThumbEE — это четвертое состояние набора команд, вносящее небольшие изменения в расширенный набор команд Thumb-2. Эти изменения делают набор команд особенно подходящим для кода, генерируемого во время выполнения (например, JIT-компиляции ) в управляемых средах выполнения . ThumbEE является целевой средой для таких языков, как Java , C# , Perl и Python , и позволяет JIT-компиляторам выводить скомпилированный код меньшего размера без снижения производительности. [ нужна ссылка ]

Новые функции, предоставляемые ThumbEE, включают автоматическую проверку нулевого указателя для каждой инструкции загрузки и сохранения, инструкцию для выполнения проверки границ массива и специальные инструкции, вызывающие обработчик. Кроме того, поскольку ThumbEE использует технологию Thumb-2, он обеспечивает доступ к регистрам r8–r15 (где хранится состояние виртуальной машины Java Jazelle/DBX). [ 128 ] Обработчики — это небольшие разделы часто вызываемого кода, обычно используемые для реализации языков высокого уровня, например, для выделения памяти для нового объекта. Эти изменения происходят в результате перепрофилирования нескольких кодов операций и знания того, что ядро находится в новом состоянии ThumbEE.

23 ноября 2011 года компания Arm запретила любое использование набора инструкций ThumbEE. [ 129 ] и Armv8 удаляет поддержку ThumbEE.

С плавающей запятой (VFP)

[ редактировать ]Технология VFP (Vector Floating Point) — это расширение сопроцессора с плавающей запятой (FPU) для архитектуры ARM. [ 130 ] (в Armv8 реализовано по-другому — сопроцессоры там не определены). Он обеспечивает недорогие вычисления с плавающей запятой одинарной и двойной точности, полностью соответствующие стандарту ANSI/IEEE Std 754-1985 для двоичной арифметики с плавающей запятой . VFP обеспечивает вычисления с плавающей запятой, подходящие для широкого спектра приложений, таких как КПК, смартфоны, сжатие и распаковка голоса, трехмерная графика и цифровой звук, принтеры, телеприставки и автомобильные приложения. Архитектура VFP была предназначена для поддержки выполнения коротких инструкций в «векторном режиме», но они работали с каждым векторным элементом последовательно и, таким образом, не обеспечивали производительность истинного векторного параллелизма одной инструкции и нескольких данных (SIMD). Поэтому этот векторный режим был удален вскоре после его появления. [ 131 ] будет заменен гораздо более мощным Advanced SIMD, также называемым Neon .

Некоторые устройства, такие как ARM Cortex-A8, имеют урезанный модуль VFPLite вместо полного модуля VFP и требуют примерно в десять раз больше тактовых циклов на операцию с плавающей запятой. [ 132 ] Архитектура до Armv8 реализовала операции с плавающей запятой/SIMD с интерфейсом сопроцессора. Другие модули с плавающей запятой и/или SIMD, обнаруженные в процессорах на базе ARM, использующих интерфейс сопроцессора, включают FPA , FPE, iwMMXt , некоторые из которых были реализованы в программном обеспечении путем перехвата, но могли быть реализованы аппаратно. Они предоставляют некоторые из тех же функций, что и VFP, но несовместимы с ним по коду операций . FPA10 также обеспечивает повышенную точность , но правильное округление (требуемое IEEE 754) реализует только с одинарной точностью. [ 133 ]

- ВФПв1

- Устаревший

- ВФПв2

- Необязательное расширение набора инструкций ARM в архитектурах ARMv5TE, ARMv5TEJ и ARMv6. VFPv2 имеет 16 64-битных регистров FPU.

- VFPv3 или VFPv3-D32

- Реализовано на большинстве процессоров Cortex-A8 и A9 ARMv7. Он обратно совместим с VFPv2, за исключением того, что он не может перехватывать исключения с плавающей запятой. VFPv3 в стандартной комплектации имеет 32 64-битных регистра FPU, добавляет инструкции VCVT для преобразования между скалярными, плавающими и двойными значениями, добавляет к VMOV немедленный режим, позволяющий загружать константы в регистры FPU.

- ВФПв3-Д16

- То же, что и выше, но только с 16 64-битными регистрами FPU. Реализовано на процессорах Cortex-R4 и R5 и Tegra 2 (Cortex-A9).

- ВФПв3-F16

- Необычно; он поддерживает IEEE754-2008 с плавающей запятой половинной точности (16 бит) в качестве формата хранения.

- VFPv4 или VFPv4-D32

- Реализованный на процессорах Cortex-A12 и A15 ARMv7, Cortex-A7 опционально имеет VFPv4-D32 в случае FPU с Neon. [ 134 ] поддержку половинной точности в качестве формата хранения и объединенные инструкции умножения-накопления . VFPv4 в стандартной комплектации имеет 32 64-битных регистра FPU, добавляет к функциям VFPv3

- ВФПв4-Д16

- То же, что и выше, но имеет только 16 64-битных регистров FPU. Реализовано на процессорах Cortex-A5 и A7 в случае FPU без Neon. [ 134 ]

- ВФПв5-Д16-М

- Реализовано на Cortex-M7, когда существует опция ядра с плавающей запятой одинарной и двойной точности.

В Debian Linux и его производных, таких как Ubuntu и Linux Mint , Armhf ( ARM hard float ) относится к архитектуре ARMv7, включая дополнительное аппаратное расширение VFP3-D16 для операций с плавающей запятой (и Thumb-2), указанное выше. Пакеты программного обеспечения и инструменты кросс-компиляции используют суффиксы Armhf и Arm/Armel для различения. [ 135 ]

Расширенный SIMD (неон)

[ редактировать ]Расширение Advanced SIMD (также известное как Neon или «MPE» Media Processing Engine) представляет собой комбинированный 64- и 128-битный набор команд SIMD, который обеспечивает стандартизированное ускорение для приложений обработки мультимедиа и сигналов. Neon включен во все устройства Cortex-A8, но является дополнительным в устройствах Cortex-A9. [ 136 ] Neon может выполнять декодирование звука MP3 на процессорах, работающих на частоте 10 МГц, и может запускать (AMR) GSM речевой кодек адаптивной многоскоростной передачи на частоте 13 МГц. Он имеет обширный набор команд, отдельные файлы регистров и независимое аппаратное обеспечение. [ 137 ] Neon поддерживает 8-, 16-, 32- и 64-битные целые числа и данные одинарной точности (32-битные) с плавающей запятой, а также операции SIMD для обработки аудио и видео, а также обработки графики и игр. В Neon SIMD поддерживает до 16 операций одновременно. Аппаратное обеспечение Neon использует те же регистры с плавающей запятой, что и VFP. Такие устройства, как ARM Cortex-A8 и Cortex-A9, поддерживают 128-битные векторы, но одновременно могут выполняться с 64 битами. [ 132 ] тогда как более новые устройства Cortex-A15 могут выполнять 128 бит за раз. [ 138 ] [ 139 ]

Особенность Neon в устройствах Armv7 заключается в том, что он сбрасывает все ненормальные числа в ноль, и в результате компилятор GCC не будет использовать его, если только -funsafe-math-optimizations, позволяющий терять денормали, включен. «Улучшенный» Neon определен, поскольку Armv8 не имеет этой особенности, но начиная с GCC 8.2 тот же флаг все еще требуется для включения инструкций Neon. [ 140 ] С другой стороны, GCC считает Neon безопасным для AArch64 для Armv8.

ProjectNe10 — первый проект ARM с открытым исходным кодом (с момента его создания; при этом они приобрели более старый проект, который теперь называется Mbed TLS ). Библиотека Ne10 представляет собой набор общих полезных функций, написанных на Neon и C (для совместимости). Библиотека была создана, чтобы позволить разработчикам использовать оптимизацию Neon без изучения Neon, но она также служит набором высокооптимизированных примеров встроенного и ассемблерного кода Neon для общих процедур DSP, арифметики и обработки изображений. Исходный код доступен на GitHub. [ 141 ]

ARM Гелиевая технология

[ редактировать ]Гелий — это векторное расширение M-профиля (MVE). Он добавляет более 150 скалярных и векторных инструкций. [ 142 ]

Расширения безопасности

[ редактировать ]TrustZone (для профиля Cortex-A)

[ редактировать ]Расширения безопасности, продаваемые как технология TrustZone, входят в архитектуру профиля приложения ARMv6KZ и более поздних версий. Он обеспечивает недорогую альтернативу добавлению еще одного выделенного ядра безопасности в SoC за счет предоставления двух виртуальных процессоров, поддерживаемых аппаратным контролем доступа. Это позволяет ядру приложения переключаться между двумя состояниями, называемыми мирами (чтобы избежать путаницы с другими названиями доменов возможностей), чтобы предотвратить утечку информации из более доверенного мира в менее доверенный мир. Этот переключатель миров обычно ортогонален всем остальным возможностям процессора, поэтому каждый мир может работать независимо от другого, используя одно и то же ядро. Затем память и периферийные устройства получают информацию об операционной среде ядра и могут использовать ее для обеспечения контроля доступа к секретам и коду на устройстве. [ 143 ]

Обычно мощная операционная система запускается в менее доверенном мире, а меньший код, специализирующийся на безопасности, — в более доверенном мире с целью уменьшить поверхность атаки . Типичные приложения включают функцию DRM для контроля использования мультимедиа на устройствах на базе ARM, [ 144 ] и предотвращение любого несанкционированного использования устройства.

На практике, поскольку конкретные детали реализации проприетарных реализаций TrustZone не были публично раскрыты для ознакомления, неясно, какой уровень уверенности обеспечивается для данной модели угроз , но они не застрахованы от атак. [ 145 ] [ 146 ]

Открытая виртуализация [ 147 ] — это реализация доверенной мировой архитектуры с открытым исходным кодом для TrustZone.

AMD лицензировала и включила технологию TrustZone в свою технологию Secure Processor Technology . [ 148 ] AMD В некоторых, но не во всех продуктах, APU включают в себя процессор Cortex-A5 для обеспечения безопасной обработки. [ 149 ] [ 150 ] [ 151 ] Фактически, ядро Cortex-A5 TrustZone было включено в более ранние продукты AMD, но не было включено из-за ограничений по времени. [ 150 ]

Samsung Knox использует TrustZone для таких целей, как обнаружение изменений в ядре, хранение сертификатов и подтверждение ключей. [ 152 ]

TrustZone для Armv8-M (для профиля Cortex-M)

[ редактировать ]Расширение безопасности, продаваемое как TrustZone для технологии Armv8-M, было представлено в архитектуре Armv8-M. Несмотря на то, что он содержит концепции, аналогичные TrustZone для Armv8-A, он имеет другой архитектурный дизайн, поскольку переключение между мирами выполняется с использованием инструкций ветвления, а не с использованием исключений. Он также поддерживает безопасную обработку чередующихся прерываний из любого мира независимо от текущего состояния безопасности. Вместе эти функции обеспечивают вызовы в безопасный мир с низкой задержкой и быструю обработку прерываний. ARM предоставляет эталонный стек защищенного мирового кода в виде доверенной прошивки для сертификатов M и PSA .

Защита страницы без выполнения

[ редактировать ]Начиная с ARMv6, архитектура ARM поддерживает защиту страниц без выполнения , которая называется XN , что означает eXecute Never . [ 153 ]

Расширение большого физического адреса (LPAE)

[ редактировать ]Расширение большого физического адреса (LPAE), которое увеличивает размер физического адреса с 32 до 40 бит, было добавлено в архитектуру Armv7-A в 2011 году. [ 154 ]

Размер физического адреса может быть даже больше в процессорах на базе 64-битной (Armv8-A) архитектуры. Например, в Cortex-A75 и Cortex-A65AE она составляет 44 бита. [ 155 ]

Армв8-Р и Армв8-М

[ редактировать ]Архитектуры Armv8-R и Armv8-M , анонсированные после архитектуры Armv8-A, имеют некоторые общие функции с Armv8-A. Однако Armv8-M не включает никаких 64-битных инструкций AArch64, а Armv8-R изначально не включал никаких инструкций AArch64; эти инструкции были добавлены в Armv8-R позже.

Армв8.1-М

[ редактировать ]Архитектура Armv8.1-M, анонсированная в феврале 2019 года, представляет собой усовершенствование архитектуры Armv8-M. Он приносит новые функции, в том числе:

- Новое расширение набора векторных команд. Векторное расширение M-профиля (MVE), или Helium, предназначено для приложений обработки сигналов и машинного обучения.

- Дополнительные улучшения набора команд для циклов и ветвей (расширение ветвей с низкими издержками).

- Инструкции для поддержки чисел с плавающей запятой половинной точности .

- Улучшен набор инструкций для управления TrustZone для модулей с плавающей запятой (FPU).

- Новый атрибут памяти в модуле защиты памяти (MPU).

- Улучшения в отладке, включая блок мониторинга производительности (PMU), непривилегированное расширение отладки и дополнительную поддержку отладки, ориентированы на разработку приложений для обработки сигналов.

- Расширение надежности, доступности и удобства обслуживания (RAS).

64/32-битная архитектура

[ редактировать ]

Armv8

[ редактировать ]Армв8-А

[ редактировать ]Объявлено в октябре 2011 г. [ 14 ] Armv8-A (часто называемый ARMv8, хотя также доступен Armv8-R) представляет собой фундаментальное изменение в архитектуре ARM. Он поддерживает два состояния выполнения : 64-битное состояние с именем AArch64 и 32-битное состояние с именем AArch32 . В состоянии AArch64 A64 поддерживается новый 64-битный набор инструкций ; в состоянии AArch32 поддерживаются два набора инструкций: исходный 32-битный набор команд с именем A32 и 32-битный набор инструкций Thumb-2 с именем T32 . AArch32 обеспечивает совместимость пользовательского пространства с Armv7-A. Состояние процессора может измениться при изменении уровня исключения; это позволяет выполнять 32-битные приложения в состоянии AArch32 в 64-битной ОС, ядро которой выполняется в состоянии AArch64, и позволяет 32-битной ОС работать в состоянии AArch32 под управлением 64-битного гипервизора, работающего в состоянии AArch64. . [ 1 ] ARM анонсировала свои ядра Cortex-A53 и Cortex-A57 30 октября 2012 года. [ 74 ] Apple была первой, кто выпустил ядро, совместимое с Armv8-A, в потребительском продукте ( Apple A7 в iPhone 5S ). AppliedMicro , используя FPGA , первым продемонстрировал Armv8-A. [ 156 ] Первой SoC Armv8-A от Samsung является Exynos 5433, используемый в Galaxy Note 4 , который имеет два кластера по четыре ядра Cortex-A57 и Cortex-A53 в конфигурации big.LITTLE ; но он будет работать только в режиме AArch32. [ 157 ]

Как для AArch32, так и для AArch64 Armv8-A поддерживает стандарт VFPv3/v4 и расширенный SIMD (Neon). Он также добавляет инструкции криптографии, поддерживающие AES , SHA-1 / SHA-256 и арифметику с конечными полями . [ 158 ] AArch64 был представлен в Armv8-A и его последующей версии. AArch64 не включен в 32-битные архитектуры Armv8-R и Armv8-M.

Процессор ARMv8-A может поддерживать один или оба AArch32 и AArch64; он может поддерживать AArch32 и AArch64 на более низких уровнях исключений и только AArch64 на более высоких уровнях исключений. [ 159 ] Например, ARM Cortex-A32 поддерживает только AArch32. [ 160 ] ARM Cortex-A34 поддерживает только AArch64, [ 161 ] а ARM Cortex-A72 поддерживает как AArch64, так и AArch32. [ 162 ] Процессор ARMv9-A должен поддерживать AArch64 на всех уровнях исключений и может поддерживать AArch32 на уровне EL0. [ 159 ]

Армв8-Р

[ редактировать ]В профиль Armv8-R была добавлена дополнительная поддержка AArch64, причем первым ядром ARM, реализующим ее, стал Cortex-R82. [ 163 ] Он добавляет набор инструкций A64.

Армв9

[ редактировать ]Армв9-А

[ редактировать ]В обновленной архитектуре, анонсированной в марте 2021 года, особое внимание уделяется безопасному выполнению и разделениям . [ 164 ] [ 165 ]

Система вооружения готова

[ редактировать ]Arm SystemReady, ранее называвшаяся Arm ServerReady, — это программа сертификации, которая помогает внедрить стандартные готовые операционные системы и гипервизоры в системы на базе Arm, от серверов центров обработки данных до промышленных периферийных устройств и устройств Интернета вещей. Ключевыми строительными блоками программы являются спецификации минимальных требований к оборудованию и встроенному ПО, на которые могут опираться операционные системы и гипервизоры. Эти характеристики: [ 166 ]

- Базовая системная архитектура (BSA) [ 167 ] и дополнения для конкретного сегмента рынка (например, дополнение Server BSA) [ 168 ]

- Базовые требования к загрузке (BBR) [ 169 ] и базовые требования безопасности загрузки (BBR) [ 170 ]

Эти спецификации разработаны совместно компанией Arm и ее партнерами из Консультативного комитета по системной архитектуре (SystemArchAC).

Architecture Compliance Suite (ACS) — это инструменты тестирования, которые помогают проверить соответствие этим спецификациям. Спецификация требований Arm SystemReady документирует требования сертификации. [ 171 ]

представила Эту программу компания Arm в 2020 году на первом мероприятии DevSummit . Его предшественник Arm ServerReady был представлен в 2018 году на мероприятии Arm TechCon. В настоящее время в эту программу входят четыре группы:

- SystemReady SR: этот диапазон предназначен для серверов и рабочих станций, поддерживающих операционные системы и гипервизоры, требующие интерфейсов UEFI , ACPI и SMBIOS . Windows, Red Hat Enterprise Linux и VMware ESXi-Arm требуют этих интерфейсов, хотя другие дистрибутивы Linux и BSD также могут их поддерживать. [ нужны разъяснения ]

- SystemReady LS (LinuxBoot System): этот диапазон предназначен для серверов, которые гиперскейлеры используют для поддержки операционных систем Linux, которым требуется прошивка LinuxBoot вместе с интерфейсами ACPI и SMBIOS.

- SystemReady ES (встроенная система): этот диапазон предназначен для промышленных периферийных устройств и устройств Интернета вещей, которые поддерживают операционные системы и гипервизоры, требующие интерфейсов UEFI, ACPI и SMBIOS. Windows IoT Enterprise, Red Hat Enterprise Linux и VMware ESXi-Arm требуют этих интерфейсов, хотя другие дистрибутивы Linux и BSD также могут их поддерживать. [ нужны разъяснения ]

- SystemReady IR (IoT Ready): эта полоса предназначена для промышленных периферийных устройств и устройств IoT, которые поддерживают операционные системы, требующие интерфейсы UEFI и дерева устройств . Также могут поддерживаться встроенный Linux (например, Yocto ) и некоторые дистрибутивы Linux/BSD (например, Fedora, Ubuntu, Debian и OpenSUSE). [ нужны разъяснения ]

Сертифицированный PSA

[ редактировать ]Сертифицированный PSA , ранее называвшийся Архитектурой безопасности платформы, представляет собой независимую от архитектуры структуру безопасности и схему оценки. Он предназначен для обеспечения безопасности устройств Интернета вещей (IoT), построенных на процессорах «система на кристалле» (SoC). [ 172 ] Он был введен для повышения безопасности в тех случаях, когда полностью доверенная среда выполнения слишком велика или сложна. [ 173 ]

Архитектура была представлена компанией Arm в 2017 году на ежегодном мероприятии TechCon . [ 173 ] [ 174 ] Хотя схема не зависит от архитектуры, она впервые была реализована на процессорных ядрах Arm Cortex-M, предназначенных для использования в микроконтроллерах. Сертификат PSA включает в себя свободно доступные модели угроз и анализы безопасности, которые демонстрируют процесс принятия решения о функциях безопасности в распространенных продуктах Интернета вещей. [ 175 ] Он также предоставляет бесплатно загружаемые пакеты интерфейса прикладного программирования (API), архитектурные спецификации, реализации встроенного ПО с открытым исходным кодом и соответствующие наборы тестов. [ 176 ]

После разработки структуры безопасности архитектуры в 2017 году схема обеспечения сертификации PSA была запущена два года спустя в Embedded World в 2019 году. [ 177 ] PSA Certified предлагает многоуровневую схему оценки безопасности для поставщиков чипов, поставщиков ОС и производителей устройств Интернета вещей. [ 178 ] Презентация Embedded World познакомила поставщиков чипов с сертификацией уровня 1. Тогда же был представлен проект защиты второго уровня. [ 179 ] Сертификация уровня 2 стала применимым стандартом в феврале 2020 года. [ 180 ]

Сертификация была создана совместными заинтересованными сторонами PSA, чтобы обеспечить индивидуальный подход к безопасности для разнообразного набора продуктов Интернета вещей. Спецификации, сертифицированные PSA, не зависят от реализации и архитектуры, поэтому их можно применять к любому чипу, программному обеспечению или устройству. [ 181 ] [ 179 ] Сертификация также устраняет фрагментацию отрасли среди производителей и разработчиков продуктов Интернета вещей . [ 182 ]

Поддержка операционной системы

[ редактировать ]32-битные операционные системы

[ редактировать ]Исторические операционные системы

[ редактировать ]Первый 32-битный персональный компьютер на базе ARM, Acorn Archimedes , изначально предназначался для работы под управлением амбициозной операционной системы под названием ARX . Машины поставлялись с ОС RISC , которая также использовалась в более поздних системах на базе ARM от Acorn и других производителей. Некоторые ранние машины Acorn также могли использовать порт Unix под названием RISC iX . (Не следует путать с RISC/os , современным вариантом Unix архитектуры MIPS.)

Встроенные операционные системы

[ редактировать ]32-битная архитектура ARM поддерживается большим количеством встроенных операционных систем и операционных систем реального времени , в том числе:

- А2

- Андроид

- ЧибиОС/РТ

- боги

- ДРИС

- ЭКоС

- embOS

- FreeBSD

- FreeRTOS

- ЧЕСТНОСТЬ

- Линукс

- Операционные системы микроконтроллеров

- Мбед

- МИНИКС 3

- MQX

- Нуклеус ПЛЮС

- NutX

- ОКЛ4

- Встроенная операционная система (OSE)

- ОС-9 [ 183 ]

- Фарос [ 184 ]

- План 9

- PikeOS [ 185 ]

- QNX

- БУНТ

- РТЭМС

- RTXC-кадры

- СКИПТА [ 186 ]

- ThreadX

- ТизенРТ

- Т-Ядро

- Вксворкс

- Windows встроенный компактный

- Windows 10 IoT ядро

- Зефир

Операционные системы мобильных устройств

[ редактировать ]По состоянию на март 2024 года 32-битная архитектура ARM была основной аппаратной средой для большинства операционных систем мобильных устройств, таких как следующие, но многие из этих платформ, таких как Android и Apple iOS, перешли на 64-битную архитектуру ARM:

Раньше, но сейчас снято с производства:

- Если есть

- ОС BlackBerry / BlackBerry 10

- ОС Firefox

- МиГо

- Ньютон ОС

- iOS 10 и более ранние версии

- Симбиан

- Windows 10 Мобильная

- Windows РТ

- Windows Телефон

- Windows Мобайл

Настольные и серверные операционные системы

[ редактировать ]32-битная архитектура ARM поддерживается ОС RISC и несколькими Unix-подобными операционными системами, включая:

- FreeBSD

- NetBSD

- OpenBSD

- OpenSolaris [ 187 ]

- несколько дистрибутивов Linux , например:

64-битные операционные системы

[ редактировать ]Встроенные операционные системы

[ редактировать ]- ЧЕСТНОСТЬ [ 188 ]

- ИЛИ [ 189 ]

- СКИПТА [ 186 ]

- продатьL4 [ 190 ]

- Фарос [ 184 ]

- FreeRTOS

- QNX [ 191 ]

- Вксворкс [ 192 ]

- Зефир

Операционные системы мобильных устройств

[ редактировать ]- Android поддерживает Armv8-A в Android Lollipop (5.0) и более поздних версиях.

- iOS поддерживает Armv8-A в iOS 7 и более поздних версиях на 64-битных процессорах Apple SoC . iOS 11 и более поздних версий, а также iPadOS поддерживают только 64-разрядные процессоры и приложения ARM.

- Мобиан

- ПостмаркетОС

- Арка Linux ARM

- Манджаро [ 193 ]

Настольные и серверные операционные системы

[ редактировать ]- Поддержка Armv8-A была включена в ядро Linux версии 3.7 в конце 2012 года. [ 194 ] Armv8-A поддерживается рядом дистрибутивов Linux , таких как:

- Поддержка Armv8-A была включена во FreeBSD в конце 2014 года. [ 202 ]

- OpenBSD имеет поддержку Armv8 с 2023 года. [update]. [ 203 ]

- NetBSD поддерживает Armv8 с начала 2018 года. [ 204 ]

- Windows — Windows 10 запускает 32-разрядные « x86- и 32-разрядные приложения ARM». [ 205 ] а также собственные настольные приложения ARM64; [ 206 ] [ 207 ] Windows 11 запускает собственные приложения ARM64, а также может запускать приложения x86 и x86-64 посредством эмуляции. Поддержка 64-битных приложений ARM в Microsoft Store доступна с ноября 2018 года. [ 208 ]

- macOS поддерживает ARM с конца 2020 года; Первый выпуск с поддержкой ARM — macOS Big Sur . [ 209 ] Rosetta 2 добавляет поддержку приложений x86-64 , но не виртуализацию компьютерных платформ x86-64. [ 210 ]

Портирование на 32- или 64-битные операционные системы ARM.

[ редактировать ]Приложения Windows, перекомпилированные для ARM и связанные с Winelib из проекта Wine , могут работать на 32-битной или 64-битной ARM в Linux, FreeBSD или других совместимых операционных системах. [ 211 ] [ 212 ] Двоичные файлы x86, например, если они не были специально скомпилированы для ARM, были продемонстрированы на ARM с использованием QEMU с Wine (в Linux и других системах), [ нужна ссылка ] но не работает на полной скорости или с теми же возможностями, что и Winelib.

Примечания

[ редактировать ]- ^ При использовании 32-битных слов скорость 4 Мбит/с соответствует 1 MIPS .

- ^ В доступных ссылках не упоминается, какая это была группа разработчиков, но, учитывая время и известную историю проектов той эпохи, вполне вероятно, что это была команда National Semiconductor, чей NS32016 страдал от большого количества ошибок.

- ^ Мэтт Эванс отмечает, что, похоже, более быстрые версии были просто помещены в более высокий интервал и, похоже, не имели никаких основных изменений. [ 36 ]

См. также

[ редактировать ]- Янтарный — процессорное ядро с открытым исходным кодом, совместимое с ARM.

- AMULET – асинхронная реализация архитектуры ARM.

- Яблочный кремний

- Аккредитованный инженер ARM – программа сертификации

- ARM big.LITTLE — гетерогенная вычислительная архитектура ARM.

- ARMulator - симулятор набора команд.

- Сравнение процессоров ARM

- Крах (уязвимость безопасности) [ 213 ]

- Компьютер с сокращенным набором команд (RISC)

- РИСК-V

- Призрак (уязвимость безопасности)

- Unicore — 32-регистровая архитектура, основанная на 32-битном ARM.

Ссылки

[ редактировать ]Цитаты

[ редактировать ]- ^ Jump up to: а б с д и ж Гризентуэйт, Ричард (2011). «Обзор технологии ARMv8-A» (PDF) . Архивировано из оригинала (PDF) 11 ноября 2011 года . Проверено 31 октября 2011 г.

- ^ «Стандарт вызова процедур для архитектуры ARM» (PDF) . Арм Холдингс . 30 ноября 2013 года . Проверено 27 мая 2013 г.

- ^ Jump up to: а б Уилсон, Роджер (2 ноября 1988 г.). «Некоторые факты о машине Acorn RISC» . Группа новостей : comp.arch . Проверено 25 мая 2007 г.

- ^ Jump up to: а б Хачман, Марк (14 октября 2002 г.). «Ядра ARM проникают на территорию 3G» . ЭкстримТех . Проверено 24 мая 2018 г.

- ^ Терли, Джим (18 декабря 2002 г.). «Двухпроцентное решение» . Встроенный . Проверено 14 февраля 2023 г.

- ^ Катресс, Ян (22 июня 2020 г.). «Новый суперкомпьютер №1: Fujitsu Fugaku и A64FX выводят Arm на вершину с производительностью 415 петафлопс» . anandtech.com . Проверено 25 января 2021 г.

- ^ «Arm Partners поставили 200 миллиардов чипов» . Оружие (Пресс-релиз) . Проверено 3 ноября 2021 г.

- ^ «Создание умного мира и использование искусственного интеллекта: ARM» . Обзор кремния . 2019 . Проверено 8 апреля 2020 г.