Семейство архитектуры ARM

| |

| Дизайнер | |

|---|---|

| Биты | 32-bit , 64-bit |

| Представлено | 1985 год |

| Дизайн | РИСК |

| Тип | Загрузка-сохранение |

| Ветвление | Код состояния , сравнение и ветвление |

| Открыть | Собственный |

| Представлено | 2011 год |

|---|---|

| Версия | ARMv8-R, ARMv8-A, ARMv8.1-A, ARMv8.2-A, ARMv8.3-A, ARMv8.4-A, ARMv8.5-A, ARMv8.6-A, ARMv8.7-A, ARMv8.8-A, ARMv8.9-A, ARMv9.0-A, ARMv9.1-A, ARMv9.2-A, ARMv9.3-A, ARMv9.4-A |

| Кодирование | AArch64 /A64 и AArch32 /A32 используют 32-битные инструкции, AArch32/T32 (Thumb-2) использует смешанные 16- и 32-битные инструкции. [1] |

| Порядок байтов | Би (немного по умолчанию) |

| Расширения | СВЕ , СВЕ2, МСП, АЕС, ША, ТМЕ; Все обязательно: Thumb-2 , Neon , VFPv4-D16, VFPv4; устарело: Джазель |

| Регистры | |

| общего назначения | 31 × 64-битные целочисленные регистры [1] |

| Плавающая точка | 32 × 128-битные регистры [1] для скалярных 32- и 64-битных FP или SIMD FP или целочисленных; или криптография |

| Версия | ARMv9-R, ARMv9-M, ARMv8-R, ARMv8-M, ARMv7-A, ARMv7-R, ARMv7E-M, ARMv7-M, ARMv6-M |

|---|---|

| Кодирование | 32-битная версия, за исключением того, что расширения Thumb-2 используют смешанные 16- и 32-битные инструкции. |

| Порядок байтов | Би (немного по умолчанию) |

| Расширения | Thumb-2 , Neon , Jazelle , AES, SHA, DSP, насыщенный, FPv4-SP, FPv5, гелий |

| Регистры | |

| общего назначения | 15 × 32-битных целочисленных регистров, включая R14 (регистр связи), но не R15 (ПК) |

| Плавающая точка | До 32 × 64-битных регистров, [2] SIMD/с плавающей запятой (необязательно) |

| Версия | ARMv6, ARMv5, ARMv4T, ARMv3, ARMv2 |

|---|---|

| Кодирование | 32-битный, за исключением того, что расширение Thumb использует смешанные 16- и 32-битные инструкции. |

| Порядок байтов | Bi (по умолчанию немного) в ARMv3 и выше |

| Расширения | Большой палец , Джазель |

| Регистры | |

| общего назначения | 15 × 32-битных целочисленных регистров, включая R14 (регистр связи), но не R15 (ПК, 26-битная адресация в более старых версиях) |

| Плавающая точка | Никто |

ARM (стилизованное в нижнем регистре как «arm» , ранее аббревиатура от Advanced RISC Machines и первоначально Acorn RISC Machine ) — это семейство RISC архитектур набора команд (ISA) для компьютерных процессоров . Arm Ltd. разрабатывает ISA и лицензирует их другим компаниям, которые создают физические устройства, использующие этот набор команд. Он также разрабатывает и лицензирует ядра , реализующие эти ISA.

Благодаря своей низкой стоимости, низкому энергопотреблению и низкому выделению тепла процессоры ARM полезны для легких портативных устройств с батарейным питанием, включая смартфоны , ноутбуки и планшетные компьютеры , а также во встроенных системах . [3] [4] [5] Однако процессоры ARM также используются для настольных компьютеров и серверов , включая самый быстрый в мире суперкомпьютер ( Fugaku ) 2020 года. [6] до 2022 года. Произведено более 230 миллиардов чипов ARM, [7] [8] [9] по состоянию на 2022 год [update]ARM — наиболее широко используемое семейство архитектур набора команд. [10] [4] [11] [12] [13]

Было несколько поколений конструкции ARM. Исходный ARM1 использовал 32-битную внутреннюю структуру, но имел 26-битное адресное пространство , что ограничивало его 64 МБ основной памяти . Это ограничение было снято в серии ARMv3, которая имеет 32-битное адресное пространство, и несколько последующих поколений вплоть до ARMv7 остались 32-битными. Выпущенная в 2011 году архитектура ARMv8-A добавила поддержку 64-битного адресного пространства и 64-битной арифметики с новым 32-битным набором команд фиксированной длины. [14] Arm Ltd. также выпустила серию дополнительных наборов инструкций для различных правил; расширение «Thumb» добавляет как 32-, так и 16-битные инструкции для повышения плотности кода , а Jazelle добавила инструкции для непосредственной обработки байт-кода Java . Более поздние изменения включают добавление одновременной многопоточности (SMT) для повышения производительности и отказоустойчивости . [15]

История

[ редактировать ]Би-би-си микро

[ редактировать ]Acorn Computers Первой широко успешной разработкой компании была BBC Micro , представленная в декабре 1981 года. Это была относительно традиционная машина, основанная на процессоре MOS Technology 6502, но ее производительность была примерно вдвое выше, чем у конкурирующих разработок, таких как Apple II, благодаря использованию более быстрого процессора. динамическая оперативная память (DRAM). Типичная DRAM того времени работала на частоте около 2 МГц; Acorn заключила сделку с Hitachi на поставку более быстрых деталей с частотой 4 МГц. [16]

Машины той эпохи обычно разделяли память между процессором и кадровым буфером , что позволяло процессору быстро обновлять содержимое экрана без необходимости выполнять отдельный ввод/вывод (I/O). Поскольку время отображения видео является точным, видеооборудование должно было иметь приоритетный доступ к этой памяти. Из-за особенностей конструкции 6502 процессор половину времени оставлял память нетронутой. Таким образом, запустив процессор на частоте 1 МГц, видеосистема могла считывать данные во время простоев, занимая общую полосу пропускания ОЗУ в 2 МГц. В BBC Micro использование ОЗУ с частотой 4 МГц позволило использовать ту же технику, но работать с удвоенной скоростью. Это позволило ему превзойти любую аналогичную машину на рынке. [17]

Бизнес-компьютер Acorn

[ редактировать ]1981 год стал также годом персонального компьютера IBM появления . Использование недавно представленного Intel 8088 процессора 16-битного процессором 6502 по сравнению с 8-битным обеспечило более высокую общую производительность. Его появление радикально изменило рынок настольных компьютеров: то, что в последние пять лет было в основном хобби и игровым рынком, начало превращаться в обязательный бизнес-инструмент, где более ранние 8-битные разработки просто не могли конкурировать. более новые 32-битные На рынок поступали и модели, такие как Motorola 68000. [18] и National Semiconductor NS32016 . [19]

Компания Acorn начала обдумывать, как конкурировать на этом рынке, и выпустила новый бумажный дизайн под названием Acorn Business Computer . Они поставили перед собой цель создать машину, производительность которой в десять раз превосходит BBC Micro, но по той же цене. [20] Это превзойдет ПК по производительности и удешевит его. В то же время недавнее появление Apple Lisa принесло концепцию графического пользовательского интерфейса (GUI) более широкой аудитории и предположило, что будущее принадлежит машинам с GUI. [21] Однако Lisa стоила 9995 долларов, так как была оснащена вспомогательными чипами, большим объемом памяти и жестким диском , что тогда было очень дорого. [22]

Затем инженеры начали изучать все доступные конструкции процессоров. Их вывод о существующих 16-битных конструкциях заключался в том, что они намного дороже и все равно «немного дерьмовые». [23] предлагая лишь немного более высокую производительность, чем их конструкция BBC Micro. Кроме того, для работы даже на этом уровне почти всегда требовалось большое количество вспомогательных микросхем, что увеличивало стоимость компьютера в целом. Эти системы просто не достигли бы проектной цели. [23] Они также рассматривали новые 32-битные конструкции, но они стоили еще дороже и имели те же проблемы с чипами поддержки. [24] По словам Софи Уилсон , все протестированные на тот момент процессоры работали примерно одинаково, с пропускной способностью около 4 Мбит/с. [25] [а]

Два ключевых события привели Acorn на путь к ARM. Одним из них была публикация серии отчетов Калифорнийского университета в Беркли , в которых предполагалось, что простая конструкция чипа, тем не менее, может иметь чрезвычайно высокую производительность, намного превышающую последние 32-битные конструкции, представленные на рынке. [26] Вторым был визит Стива Фербера и Софи Уилсон в Western Design Center , компанию, управляемую Биллом Меншем и его сестрой, которая стала логическим преемником команды MOS и предлагала новые версии, такие как WDC 65C02 . Команда Acorn увидела, как ученики старших классов создают макеты микросхем на машинах Apple II, а это означало, что это может сделать каждый. [27] [28] Напротив, посещение другой дизайнерской фирмы, работающей над современными 32-битными процессорами, выявило команду, состоящую из более чем дюжины участников, которые уже работали над версией H своего проекта, но все еще содержали ошибки. [б] Это закрепило их решение в конце 1983 года начать разработку собственного процессора — Acorn RISC Machine. [29]

Концепции дизайна

[ редактировать ]Первоначальные проекты RISC Беркли в некотором смысле представляли собой системы обучения, не предназначенные специально для прямой работы. К базовым концепциям RISC с большим количеством регистров и загрузкой/сохранением ARM добавила ряд хорошо принятых конструктивных особенностей 6502. Главной из них была способность быстро обслуживать прерывания , что позволяло машинам обеспечивать разумную ввода/вывода производительность . без дополнительного внешнего оборудования. Чтобы обеспечить прерывания с такой же производительностью, как у 6502, конструкция ARM ограничила свое физическое адресное пространство до 64 МБ общего адресуемого пространства, что требует 26 бит адреса. Поскольку инструкции имели длину 4 байта (32 бита) и должны были быть выровнены по границам 4 байтов, младшие 2 бита адреса инструкции всегда были равны нулю. Это означало, что счетчик программ (ПК) должен был иметь только 24 бита, что позволяло хранить его вместе с восьмибитными флагами процессора в одном 32-битном регистре. Это означало, что при получении прерывания все состояние машины можно было сохранить за одну операцию, тогда как если бы ПК был полным 32-битным значением, потребовались бы отдельные операции для хранения ПК и флагов состояния. Это решение вдвое сократило накладные расходы на прерывания. [30]

Еще одним изменением, и одним из наиболее важных с точки зрения практической реальной производительности, была модификация набора команд для использования преимуществ страничного режима DRAM . Недавно представленный страничный режим позволил последующим обращениям к памяти выполняться в два раза быстрее, если они находились примерно в одном и том же месте или «странице» в чипе DRAM. Проект Беркли не учитывал страничный режим и одинаково обрабатывал всю память. В конструкции ARM были добавлены специальные векторные инструкции доступа к памяти, «S-циклы», которые можно было использовать для заполнения или сохранения нескольких регистров на одной странице в страничном режиме. Это удвоило производительность памяти, когда ее можно было использовать, и было особенно важно для производительности графики. [31]

В проектах RISC Беркли использовались окна регистров , чтобы уменьшить количество операций сохранения и восстановления регистров, выполняемых при вызовах процедур ; в конструкции ARM это не учитывалось.

Уилсон разработал набор команд, написав симуляцию процессора на BBC BASIC , который работал на BBC Micro со вторым процессором 6502 . [32] [33] Это убедило инженеров Acorn, что они на правильном пути. Уилсон обратился к генеральному директору Acorn Герману Хаузеру и запросил дополнительные ресурсы. Хаузер дал свое согласие и собрал небольшую команду для разработки настоящего процессора на основе ISA Уилсона. [34] Официальный проект Acorn RISC Machine стартовал в октябре 1983 года.

ARM1

[ редактировать ]

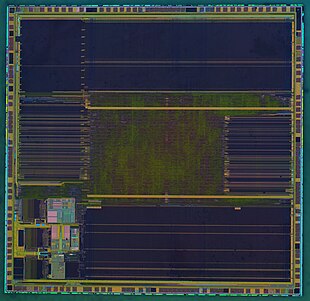

Acorn выбрала VLSI Technology в качестве «кремниевого партнера», поскольку они были источником ПЗУ и специальных чипов для Acorn. Компания Acorn разработала дизайн, а компания VLSI обеспечила компоновку и производство. Первые образцы кремния ARM работали правильно, когда их впервые получили и испытали 26 апреля 1985 года. [3] Эти версии, известные как ARM1, работали на частоте 6 МГц. [35]

Первое приложение ARM было вторым процессором для BBC Micro, где оно помогло в разработке программного обеспечения для моделирования, чтобы завершить разработку вспомогательных микросхем (VIDC, IOC, MEMC), а также ускорило работу программного обеспечения САПР, используемого при разработке ARM2. Впоследствии Уилсон переписал BBC BASIC на языке ассемблера ARM . Глубокие знания, полученные при разработке набора команд, позволили сделать код очень плотным, что сделало ARM BBC BASIC чрезвычайно хорошим тестом для любого эмулятора ARM.

ARM2

[ редактировать ]Результат моделирования на платах ARM1 привел к появлению в конце 1986 года конструкции ARM2, работающей на частоте 8 МГц, а в начале 1987 года - версии с увеличенной скоростью от 10 до 12 МГц. [с] Существенным изменением в базовой архитектуре стало добавление умножителя Бута , тогда как раньше умножение нужно было выполнять программно. [37] Кроме того, новый режим запроса быстрого прерывания, сокращенно FIQ, позволял заменять регистры с 8 по 14 как часть самого прерывания. Это означало, что запросам FIQ не нужно было сохранять свои регистры, что еще больше ускоряло прерывания. [38]

Первым использованием ARM2 стал персональный компьютер Acorn Archimedes моделей A305, A310 и A440, выпущенный в 1987 году.

Согласно тесту Dhrystone , производительность ARM2 примерно в семь раз превышала производительность типичной системы на базе процессора 68000 с частотой 7 МГц, такой как Amiga или Macintosh SE . Он был в два раза быстрее, чем Intel 80386, работавший на частоте 16 МГц, и примерно с той же скоростью, что и многопроцессорный VAX-11/784 суперминикомпьютер . Единственными системами, которые превзошли его, были Sun SPARC и MIPS R2000 на базе RISC рабочие станции . [39] Кроме того, поскольку ЦП был разработан для высокоскоростного ввода-вывода, в нем не было многих вспомогательных микросхем, которые можно было увидеть в этих машинах; в частности, в нем отсутствовал какой-либо выделенный контроллер прямого доступа к памяти (DMA), который часто можно было найти на рабочих станциях. Графическая система также была упрощена на основе того же набора основных предположений о памяти и времени. Результатом стала значительно упрощенная конструкция, предлагающая производительность на уровне дорогих рабочих станций, но по цене, аналогичной современным настольным компьютерам. [39]

ARM2 имел 32-битную шину данных , 26-битное адресное пространство и 27 32-битных регистров , 16 из которых доступны в любой момент времени (включая ПК ). [40] В ARM2 было транзисторов . всего 30 000 [41] по сравнению с шестилетней моделью Motorola 68000 с показателем около 68 000. Во многом эта простота объясняется отсутствием микрокода , который составляет от четверти до одной трети транзисторов 68000, а также отсутствием (как и у большинства процессоров того времени) кэша . Эта простота позволила ARM2 иметь низкое энергопотребление и более простую тепловую упаковку за счет меньшего количества активных транзисторов, но при этом предлагать лучшую производительность, чем современная IBM PS/2 Model 50 1987 года , которая первоначально использовала Intel 80286 и предлагала 1,8 MIPS. @ 10 МГц, а позже, в 1987 году, 2 MIPS PS / 2 70 с Intel 386 DX @ 16 МГц. [42] [43]

Преемник ARM3 был выпущен с кэшем объемом 4 КБ, что еще больше повысило производительность. [44] Адресная шина была расширена до 32 бит в ARM6, но программный код по-прежнему должен был находиться в пределах первых 64 МБ памяти в 26-битном режиме совместимости из-за зарезервированных битов для флагов состояния. [45]

ООО «Продвинутые RISC Machines» — ARM6

[ редактировать ]

В конце 1980-х годов Apple Computer и VLSI Technology начали работать с Acorn над новыми версиями ядра ARM. В 1990 году Acorn выделила команду дизайнеров в новую компанию под названием Advanced RISC Machines Ltd. [46] [47] [48] которая стала ARM Ltd., когда ее материнская компания Arm Holdings plc разместила акции на Лондонской фондовой бирже и Nasdaq в 1998 году. [49] Новая разработка Apple-ARM в конечном итоге превратилась в ARM6, впервые выпущенный в начале 1992 года. Apple использовала ARM610 на базе ARM6 в качестве основы для своего Apple Newton КПК .

Ранние лицензиаты

[ редактировать ]В 1994 году Acorn использовала ARM610 в качестве основного центрального процессора (ЦП) в своих RiscPC компьютерах . DEC лицензировала архитектуру ARMv4 и выпустила StrongARM . [50] При частоте 233 МГц этот процессор потреблял всего один ватт (более новые версии потребляют гораздо меньше). Позже эта работа была передана Intel в рамках урегулирования иска, и Intel воспользовалась возможностью дополнить свою линейку i960 StrongARM. Позже Intel разработала собственную высокопроизводительную реализацию под названием XScale , которую впоследствии продала компании Marvell . Количество транзисторов ядра ARM на протяжении всех этих изменений оставалось практически неизменным; В ARM2 было 30 000 транзисторов. [51] тогда как ARM6 вырос всего до 35 000. [52]

Доля рынка

[ редактировать ]В 2005 году около 98% всех проданных мобильных телефонов использовали хотя бы один процессор ARM. [53] В 2010 году производители чипов на базе ARM -архитектуры сообщили о поставках 6,1 млрд процессоров на базе ARM , что составляет 95% смартфонов , 35% цифровых телевизоров и приставок , а также 10% мобильных компьютеров . В 2011 году 32-битная архитектура ARM была наиболее широко используемой архитектурой в мобильных устройствах и самой популярной 32-битной архитектурой во встроенных системах. [54] В 2013 году было произведено 10 млрд. [55] и «Чипы на базе ARM используются почти в 60 процентах мобильных устройств в мире». [56]

Лицензирование

[ редактировать ]

Основная лицензия

[ редактировать ]Основным бизнесом Arm Ltd. является продажа IP-ядер , которые лицензиаты используют для создания микроконтроллеров (MCU), процессоров и систем на кристаллах на основе этих ядер. Производитель оригинальной конструкции объединяет ядро ARM с другими деталями для создания законченного устройства, которое, как правило, может быть построено на существующих заводах по производству полупроводников (фабрик) с низкими затратами и при этом обеспечивать существенную производительность. Наиболее успешной реализацией стал ARM7TDMI , проданный сотнями миллионов экземпляров. Atmel была центром разработки предшественников встраиваемой системы на базе ARM7TDMI.

Архитектуры ARM, используемые в смартфонах, КПК и других мобильных устройствах, варьируются от ARMv5 до ARMv8-A .

В 2009 году некоторые производители представили нетбуки на базе процессоров с архитектурой ARM, составив прямую конкуренцию нетбукам на базе Intel Atom . [57]

Arm Ltd. предлагает различные условия лицензирования, различающиеся по стоимости и результатам. Arm Ltd. предоставляет всем лицензиатам интегрируемое описание аппаратного обеспечения ядра ARM, а также полный набор инструментов для разработки программного обеспечения ( компилятор , отладчик , комплект разработки программного обеспечения ), а также право на продажу произведенного полупроводникового процессора, содержащего процессор ARM.

Пакеты SoC, объединяющие основные разработки ARM, включают первые три поколения Nvidia Tegra, семейство Quatro от CSR plc, Nova и NovaThor от ST-Ericsson, микроконтроллеры Precision32 от Silicon Labs, продукты OMAP от Samsung от Texas Instruments, продукты Hummingbird и Exynos , Apple A4 , A5 и A5X , а также NXP от i.MX .

Лицензиаты Fabless , желающие интегрировать ядро ARM в свою собственную конструкцию чипа, обычно заинтересованы только в приобретении готового к производству проверенного полупроводникового ядра интеллектуальной собственности . Для этих клиентов компания Arm Ltd. предоставляет описание списка цепей выбранного ядра ARM, а также абстрактную модель моделирования и тестовые программы для облегчения интеграции и проверки конструкции. Более амбициозные клиенты, в том числе производители интегрированных устройств (IDM) и литейные операторы, предпочитают приобретать IP-адрес процессора в синтезируемой RTL ( Verilog форме ). Благодаря синтезируемому RTL заказчик имеет возможность выполнять оптимизацию и расширение на уровне архитектуры. Это позволяет разработчику достигать экзотических целей проектирования, которые иначе невозможны с помощью немодифицированного списка соединений ( высокая тактовая частота , очень низкое энергопотребление, расширение набора команд и т. д.). Хотя компания Arm Ltd. не предоставляет лицензиату право перепродавать саму архитектуру ARM, лицензиаты могут свободно продавать произведенную продукцию, такую как микросхемы, оценочные платы и комплексные системы. Торговые литейные заводы могут быть особым случаем; Им не только разрешено продавать готовый кремний, содержащий ядра ARM, но и, как правило, они имеют право повторно производить ядра ARM для других клиентов.

Arm Ltd. оценивает свою интеллектуальную собственность на основе воспринимаемой ценности. Ядра ARM с более низкой производительностью обычно требуют более низких затрат на лицензию, чем ядра с более высокой производительностью. С точки зрения реализации синтезируемое ядро стоит дороже, чем ядро жесткого макроса (черного ящика). Вопрос цен усложняется тем, что литейное предприятие, имеющее лицензию ARM, такое как Samsung или Fujitsu, может предложить потрясающим клиентам снижение затрат на лицензирование. В обмен на приобретение ядра ARM через собственные службы проектирования литейного завода клиент может уменьшить или исключить оплату авансового лицензионного сбора ARM.

По сравнению со специализированными заводами по производству полупроводников (такими как TSMC и UMC ), не имеющими собственных услуг по проектированию, Fujitsu/Samsung взимают в два-три раза больше за изготовленную пластину . [ нужна ссылка ] Для приложений с низким и средним объемом работы литейное бюро по проектированию предлагает более низкие общие цены (за счет субсидирования лицензионного сбора). Для крупносерийного массового производства деталей долгосрочное снижение затрат, достижимое за счет снижения цен на пластины, снижает влияние затрат ARM на NRE ( единовременное проектирование ), что делает специализированный литейный завод лучшим выбором.

В число компаний, разработавших чипы с ядрами, разработанными Arm, входят Amazon.com дочерняя компания Annapurna Labs , [58] Analog Devices , Apple , AppliedMicro (сейчас: MACOM Technology Solutions) [59] ), Atmel , Broadcom , Cavium , Cypress Semiconductor , Freescale Semiconductor (теперь NXP Semiconductors ), Huawei , Intel , [ сомнительно – обсудить ] Maxim Integrated , Nvidia , NXP , Qualcomm , Renesas , Samsung Electronics , ST Microelectronics , Texas Instruments и Xilinx .

Построен на основе лицензии ARM Cortex Technology.

[ редактировать ]В феврале 2016 года ARM объявила о лицензии «Built on ARM Cortex Technology», которую часто сокращают до лицензии «Built on Cortex» (BoC). Эта лицензия позволяет компаниям сотрудничать с ARM и вносить изменения в конструкции ARM Cortex. Эти изменения конструкции не будут переданы другим компаниям. Эти полузаказные конструкции ядра также имеют свободу бренда, например Kryo 280 .

В число компаний, которые в настоящее время являются лицензиатами технологии Building on ARM Cortex, входит Qualcomm . [60]

Архитектурная лицензия

[ редактировать ]Компании также могут получить архитектурную лицензию ARM для разработки собственных ядер ЦП с использованием наборов инструкций ARM. Эти ядра должны полностью соответствовать архитектуре ARM. В число компаний, разработавших ядра, реализующие архитектуру ARM, входят Apple, AppliedMicro (сейчас: Ampere Computing ), Broadcom, Cavium (сейчас: Marvell), Digital Equipment Corporation , Intel, Nvidia, Qualcomm, Samsung Electronics, Fujitsu и NUVIA Inc. ( приобретена Qualcomm в 2021 году).

Гибкий доступ к ARM

[ редактировать ]16 июля 2019 года ARM объявила о гибком доступе ARM. ARM Flexible Access обеспечивает неограниченный доступ к включенной интеллектуальной собственности (IP) ARM для разработки. Лицензионные сборы за каждый продукт взимаются после того, как клиент приступает к созданию литейного производства или прототипированию. [61] [62]

75% последних IP-адресов ARM за последние два года включены в ARM Flexible Access. По состоянию на октябрь 2019 года:

- Процессоры: Cortex-A5 , Cortex-A7 , Cortex-A32 , Cortex-A34 , Cortex-A35 , Cortex-A53 , Cortex-R5 , Cortex-R8 , Cortex-R52 , Cortex-M0 , Cortex-M0+ , Cortex-M3 , Кортекс-М4 , Кортекс-М7 , Кортекс-М23 , Кортекс-М33

- Графические процессоры: Mali-G52 , Mali-G31 . Включает комплекты разработки драйверов Mali (DDK).

- Межсоединение: CoreLink NIC-400, CoreLink NIC-450, CoreLink CCI-400, CoreLink CCI-500, CoreLink CCI-550, ADB-400 AMBA, XHB-400 AXI-AHB

- Системные контроллеры: CoreLink GIC-400, CoreLink GIC-500, PL192 VIC, BP141 TrustZone Memory Wrapper, CoreLink TZC-400, CoreLink L2C-310, CoreLink MMU-500, интерфейс памяти BP140.

- IP-адрес безопасности: CryptoCell-312, CryptoCell-712, генератор истинных случайных чисел TrustZone.

- Периферийные контроллеры: PL011 UART, PL022 SPI, PL031 RTC.

- Отладка и трассировка: CoreSight SoC-400, CoreSight SDC-600, CoreSight STM-500, макроячейка CoreSight System Trace, контроллер памяти CoreSight Trace

- Комплекты конструкторов: Корстоун-101, Корстоун-201

- Физический IP: Artisan PIK для Cortex-M33 TSMC 22ULL, включая компиляторы памяти, логические библиотеки, GPIO и документацию.

- Инструменты и материалы: Socrates IP ToolingARM Design Studio, модели виртуальных систем.

- Поддержка: стандартная техническая поддержка ARM, онлайн-обучение ARM, обновления обслуживания, кредиты на обучение на месте и обзоры конструкции.

Ядра

[ редактировать ]| Архитектура | Основной разрядность |

Ядра | Профиль | Ссылаться ренцес | |

|---|---|---|---|---|---|

| Арм, ООО | Третья сторона | ||||

ARMv1 |

ARM1 | Классический |

|||

ARMv2 |

32 |

АРМ2 , АРМ250, АРМ3 | Янтарный , STORM Open Soft Core [63] | Классический |

|

ARMv3 |

32 |

АРМ6 , АРМ7 | Классический |

||

ARMv4 |

32 |

ARM8 | StrongARM , FA526, ZAP процессорное ядро с открытым исходным кодом | Классический |

|

ARMv4T |

32 |

ARM7TDMI , ARM9TDMI , SecurCore SC100 | Классический |

||

ARMv5TE |

32 |

ARM7EJ , ARM9E , ARM10E | XScale , FA626TE, Feroceon, PJ1/Ирокез | Классический |

|

ARMv6 |

32 |

ARM11 | Классический |

||

АРМв6-М |

32 |

ARM Cortex-M0 , ARM Cortex-M0+ , ARM Cortex-M1 , SecurCore SC000 | |||

АРМв7-М |

32 |

ARM Cortex-M3 , SecurCore SC300 | Apple M7 Сопроцессор движения | Микроконтроллер |

|

ARMv7E-M |

32 |

ARM Cortex-M4 , ARM Cortex-M7 | Микроконтроллер |

||

АРМв8-М |

32 |

АРМ Кортекс-М23 , [65] АРМ Кортекс-М33 [66] | Микроконтроллер |

||

ARMv8.1-М

|

32

|

ARM Cortex-M55 , ARM Cortex-M85 | Микроконтроллер

|

||

ARMv7-R |

32 |

ARM Cortex-R4 , ARM Cortex-R5 , ARM Cortex-R7 , ARM Cortex-R8 | |||

ARMv8-R |

32 |

ARM Кортекс-R52 | В режиме реального времени |

||

64

|

ARM Кортекс-R82 | В режиме реального времени

|

|||

ARMv7-А |

32 |

ARM Cortex-A5 , ARM Cortex-A7 , ARM Cortex-A8 , ARM Cortex-A9 , ARM Cortex-A12 , ARM Cortex-A15 , ARM Cortex-A17 | Qualcomm Скорпион / Крейт , PJ4/Шива, Apple Swift ( A6 , A6X ) | ||

ARMv8-А |

32 |

ARM Кортекс-А32 [72] | Приложение |

||

64 /32 |

АРМ Кортекс-А35 , [73] ARM Cortex-A53 , ARM Cortex-A57 , [74] АРМ Кортекс-А72 , [75] ARM Кортекс-A73 [76] | X-Gene , Nvidia Denver 1/2 , Cavium ThunderX , AMD K12 , Apple Cyclone ( A7 )/Typhoon ( A8 , A8X )/Twister ( A9 , A9X )/Hurricane+Zephyr ( A10 , A10X ), Qualcomm Kryo , Samsung M1 /М2 («Мангуст») /М3 («Сурикат») | Приложение |

||

| ARM Кортекс-А34 [82] | Приложение

|

||||

ARMv8.1-А |

64/32 |

будет объявлено позднее | Кавиум ГромX2 | Приложение |

|

ARMv8.2-А |

64/32 |

АРМ Кортекс-А55 , [84] АРМ Кортекс-А75 , [85] АРМ Кортекс-А76 , [86] ARM Cortex-A77 , ARM Cortex-A78 , ARM Cortex-X1 , ARM Neoverse N1 | Nvidia Carmel , Samsung M4 («Гепард»), Fujitsu A64FX (512-битный ARMv8 SVE) | Приложение |

|

64 |

ARM Cortex-A65 , ARM Neoverse E1 с одновременной многопоточностью (SMT), ARM Cortex-A65AE [90] (также имеющий, например, скалярное произведение ARMv8.4; предназначено для задач, критически важных для безопасности, таких как усовершенствованные системы помощи водителю (ADAS)) | Apple Monsoon+Mistral ( A11 ) (сентябрь 2017 г.) | Приложение |

||

ARMv8.3-А

|

64/32 |

будет объявлено позднее | Приложение

|

||

64 |

будет объявлено позднее | Apple Vortex+Tempest ( A12 , A12X , A12Z ), Marvell ThunderX3 (v8.3+) [91] | Приложение |

||

ARMv8.4-А |

64/32 |

будет объявлено позднее | Приложение |

||

64 |

ARM Неоверс V1 | Яблочная молния+Гром ( A13 ), Яблочная огненная буря+Ледяная буря ( A14 , M1 ) | Приложение |

||

ARMv8.5-А

|

64/32 |

будет объявлено позднее | Приложение

|

||

64 |

будет объявлено позднее | Приложение

|

|||

ARMv8.6-А

|

64 |

будет объявлено позднее | Apple Avalanche+Blizzard ( A15 , M2 ), Apple Everest+Sawtooth ( A16 ) [92] | Приложение

|

|

ARMv8.7-А

|

64 |

будет объявлено позднее | Приложение

|

||

ARMv8.8-А

|

64

|

будет объявлено позднее | Приложение

|

||

ARMv8.9-А

|

64

|

будет объявлено позднее | Приложение

|

||

ARMv9.0-А

|

64

|

ARM Cortex-A510 , ARM Cortex-A710 , ARM Cortex-A715 , ARM Cortex-X2 , ARM Cortex-X3 , ARM Neoverse E2 , ARM Neoverse N2 , ARM Neoverse V2 | Приложение

|

||

ARMv9.1-А

|

64

|

будет объявлено позднее | Приложение

|

||

ARMv9.2-А

|

64

|

ARM Cortex-A520 , ARM Cortex-A720 , ARM Cortex-X4 | Яблоко М4 [96] | Приложение

|

|

ARMv9.3-А

|

64

|

будет объявлено позднее | Приложение

|

||

ARMv9.4-А

|

64

|

будет объявлено позднее | Приложение

|

||

- ^ Перейти обратно: а б Хотя большинство каналов данных и регистров ЦП в ранних процессорах ARM были 32-битными, адресная память была ограничена 26 битами ; затем старшие биты используются для флагов состояния в регистре счетчика программ.

- ^ Перейти обратно: а б с ARMv3 включал режим совместимости для поддержки 26-битных адресов более ранних версий архитектуры. Этот режим совместимости не является обязательным в ARMv4 и полностью удален в ARMv5.

Arm предоставляет список поставщиков, которые реализуют ядра ARM в своих разработках (стандартные продукты для конкретных приложений (ASSP), микропроцессоры и микроконтроллеры). [99]

Примеры применения ядер ARM

[ редактировать ]

Ядра ARM используются во многих продуктах, особенно в КПК и смартфонах . Некоторыми примерами вычислений являются устройства Microsoft первого Surface , Surface 2 и Pocket PC поколения (после 2002 года ), Apple от iPad и Asus от Eee Pad Transformer планшетные компьютеры , а также несколько ноутбуков Chromebook . Apple iPhone Другие включают смартфоны и iPod портативные медиаплееры , Canon PowerShot цифровые камеры , гибрид Nintendo Switch , процессор безопасности Wii и 3DS портативные игровые консоли , а также навигации TomTom пошаговой системы .

В 2005 году Арм принял участие в разработке Манчестерского университета компьютера SpiNNaker , который использовал ядра ARM для моделирования человеческого мозга . [100]

Чипы ARM также используются в Raspberry Pi , BeagleBoard , BeagleBone , PandaBoard и других одноплатных компьютерах , поскольку они очень маленькие, недорогие и потребляют очень мало энергии.

32-битная архитектура

[ редактировать ]

32-битная архитектура ARM ( ARM32 ), такая как ARMv7-A (реализующая AArch32; дополнительную информацию см . в разделе Armv8-A ), была наиболее широко используемой архитектурой в мобильных устройствах по состоянию на 2011 год. [update]. [54]

С 1995 года различные версии Справочного руководства по архитектуре ARM (см. § Внешние ссылки ) являются основным источником документации по архитектуре процессора ARM и набору команд, отличая интерфейсы, которые должны поддерживать все процессоры ARM (например, семантику инструкций), от детали реализации, которые могут различаться. Архитектура со временем развивалась, и седьмая версия архитектуры, ARMv7, определяет три «профиля» архитектуры:

- A-профиль, профиль «Приложение», реализованный 32-битными ядрами серии Cortex-A и некоторыми ядрами, отличными от ARM.

- R-профиль, профиль «Реального времени», реализованный ядрами Cortex-R. серии

- М-профиль, профиль «Микроконтроллер», реализованный большинством ядер Cortex-M . серии

Хотя профили архитектуры были впервые определены для ARMv7, впоследствии ARM определила архитектуру ARMv6-M (используемую Cortex M0 / M0+ / M1 ) как подмножество профиля ARMv7-M с меньшим количеством инструкций.

Режимы процессора

[ редактировать ]За исключением M-профиля, 32-битная архитектура ARM определяет несколько режимов ЦП в зависимости от реализованных функций архитектуры. В любой момент времени ЦП может находиться только в одном режиме, но переключать режимы он может вследствие внешних событий (прерывания) или программно. [101]

- Пользовательский режим: единственный непривилегированный режим.

- Режим FIQ: привилегированный режим, который включается всякий раз, когда процессор принимает запрос на быстрое прерывание .

- Режим IRQ: привилегированный режим, который включается всякий раз, когда процессор принимает прерывание.

- Режим супервизора (svc): привилегированный режим, включаемый при каждом сбросе ЦП или при выполнении инструкции SVC.

- Режим прерывания: привилегированный режим, который включается всякий раз, когда возникает исключение прерывания предварительной выборки или прерывания данных.

- Неопределенный режим: привилегированный режим, который включается всякий раз, когда возникает неопределенное исключение инструкции.

- Системный режим (ARMv4 и выше): единственный привилегированный режим, вход в который не осуществляется посредством исключения. Его можно ввести только путем выполнения инструкции, которая явно записывает биты режима регистра текущего состояния программы (CPSR) из другого привилегированного режима (не из пользовательского режима).

- Режим монитора (расширения безопасности ARMv6 и ARMv7, ARMv8 EL3): режим монитора введен для поддержки расширения TrustZone в ядрах ARM.

- Режим Hyp (расширения виртуализации ARMv7, ARMv8 EL2): режим гипервизора, который поддерживает требования виртуализации Попека и Голдберга для незащищенной работы ЦП. [102] [103]

- Режим потока (ARMv6-M, ARMv7-M, ARMv8-M): режим, который можно указать как привилегированный или непривилегированный. Использование указателя основного стека (MSP) или указателя стека процесса (PSP) также можно указать в регистре CONTROL с привилегированным доступом. Этот режим предназначен для пользовательских задач в среде RTOS, но обычно используется в «голом железе» для суперцикла.

- Режим обработчика (ARMv6-M, ARMv7-M, ARMv8-M): режим, предназначенный для обработки исключений (кроме RESET, который обрабатывается в режиме Thread). Режим обработчика всегда использует MSP и работает на привилегированном уровне.

Набор инструкций

[ редактировать ]Первоначальная (и последующая) реализация ARM была аппаратно реализована без микрокода , как и гораздо более простой 8-битный процессор 6502 , использовавшийся в предыдущих микрокомпьютерах Acorn.

32-битная архитектура ARM (и по большей части 64-битная архитектура) включает в себя следующие функции RISC:

- Архитектура загрузки-сохранения .

- нет поддержки невыровненного доступа к памяти В исходной версии архитектуры . ARMv6 и более поздние версии, за исключением некоторых версий микроконтроллера, поддерживают невыровненный доступ для инструкций загрузки/сохранения, состоящих из полуслова и одного слова, с некоторыми ограничениями, такими как отсутствие гарантированной атомарности . [104] [105]

- размером 16 × 32 бита Единый регистровый файл (включая счетчик программ, указатель стека и регистр связи).

- Фиксированная ширина инструкций 32 бита для облегчения декодирования и конвейерной обработки за счет уменьшения плотности кода . Позже в набор инструкций Thumb были добавлены 16-битные инструкции и увеличена плотность кода.

- В основном выполнение за один такт.

Чтобы компенсировать более простую конструкцию по сравнению с процессорами типа Intel 80286 и Motorola 68020 , были использованы некоторые дополнительные конструктивные особенности:

- Условное выполнение большинства инструкций снижает накладные расходы на ветвление и компенсирует отсутствие предсказателя ветвлений в ранних чипах.

- Арифметические инструкции изменяют коды условий только при необходимости.

- 32-битный бочкообразный сдвигатель можно использовать без снижения производительности при выполнении большинства арифметических инструкций и вычислений адресов.

- Имеет мощные режимы индексированной адресации .

- Регистр связи поддерживает быстрые вызовы конечных функций.

- с двумя уровнями приоритета Простая, но быстрая подсистема прерываний имеет переключаемые банки регистров.

Арифметические инструкции

[ редактировать ]ARM включает в себя арифметические операции с целыми числами: сложение, вычитание и умножение; некоторые версии архитектуры также поддерживают операции деления.

ARM поддерживает умножение 32 × 32 бита с 32-битным или 64-битным результатом, хотя ядра Cortex-M0/M0+/M1 не поддерживают 64-битные результаты. [106] Некоторые ядра ARM также поддерживают умножения 16 × 16 бит и 32 × 16 бит.

Инструкции деления включены только в следующие архитектуры ARM:

- Архитектуры Armv7-M и Armv7E-M всегда включают инструкции деления. [107]

- Архитектура Armv7-R всегда включает инструкции деления в набор инструкций Thumb, но при необходимости — в 32-битный набор команд. [108]

- Архитектура Armv7-A дополнительно включает инструкции деления. Инструкции могут быть не реализованы, либо реализованы только в наборе инструкций Thumb, либо реализованы в обоих наборах инструкций Thumb и ARM, либо реализованы, если включены расширения виртуализации. [108]

Регистры

[ редактировать ]| usr | система | СВК | около | и | прерывание | фик |

|---|---|---|---|---|---|---|

| Р0 | ||||||

| Р1 | ||||||

| Р2 | ||||||

| Р3 | ||||||

| Р4 | ||||||

| Р5 | ||||||

| Р6 | ||||||

| Р7 | ||||||

| Р8 | R8_рис | |||||

| Р9 | R9_фик | |||||

| 10 рэндов | R10_фик | |||||

| Р11 | R11_рис | |||||

| Р12 | R12_фик | |||||

| Р13 | R13_svc | R13_abt | R13_и | R13_irq | R13_рис | |

| Р14 | R14_svc | R14_abt | R14_и | R14_irq | R14_рис | |

| 15 рэндов | ||||||

| КПСР | ||||||

| SPSR_svc | SPSR_abt | СПСР_и | SPSR_irq | SPSR_fiq | ||

Регистры от R0 до R7 одинаковы во всех режимах ЦП; они никогда не вносятся в банк.

Регистры с R8 по R12 одинаковы во всех режимах ЦП, кроме режима FIQ. Режим FIQ имеет свои собственные регистры от R8 до R12.

R13 и R14 объединены во все привилегированные режимы ЦП, кроме системного режима. То есть каждый режим, в который можно войти из-за исключения, имеет свои R13 и R14. Эти регистры обычно содержат указатель стека и адрес возврата из вызовов функций соответственно.

Псевдонимы:

- R13 также называется SP, указателем стека .

- R14 также называется LR, регистром связи .

- R15 также называют ПК, программным счетчиком .

Регистр текущего состояния программы (CPSR) имеет следующие 32 бита. [109]

- M (биты 0–4) — биты режима процессора.

- T (бит 5) — бит состояния Thumb.

- F (бит 6) — бит отключения FIQ.

- I (бит 7) — бит отключения IRQ.

- А (бит 8) — это бит запрета прерывания неточных данных.

- E (бит 9) — бит порядка байтов данных.

- IT (биты 10–15 и 25–26) — это биты состояния if-then.

- GE (биты 16–19) — это биты «больше или равно».

- DNM (биты 20–23) — это биты запрета на изменение.

- J (бит 24) — бит состояния Java.

- Q (бит 27) — бит закрепленного переполнения.

- V (бит 28) — бит переполнения.

- C (бит 29) — бит переноса/заимствования/расширения.

- Z (бит 30) — нулевой бит.

- N (бит 31) — отрицательный бит/меньше чем.

Условное исполнение

[ редактировать ]Почти каждая инструкция ARM имеет функцию условного выполнения, называемую предикацией , которая реализуется с помощью 4-битного селектора кода условия (предиката). Чтобы обеспечить безусловное выполнение, один из четырехбитных кодов заставляет команду выполняться всегда. Большинство других архитектур ЦП имеют только коды условий в инструкциях ветвления. [110]

Хотя предикат занимает четыре из 32 битов в коде команды и, таким образом, значительно сокращает количество битов кодирования, доступных для смещения в инструкциях доступа к памяти, он избегает инструкций ветвления при генерации кода для небольших if заявления . Помимо устранения самих инструкций ветвления, это сохраняет конвейер выборки/декодирования/выполнения за счет всего лишь одного цикла на пропущенную инструкцию.

Алгоритм, который представляет собой хороший пример условного выполнения, — это основанный на вычитании алгоритм Евклида для вычисления наибольшего общего делителя . На языке программирования C алгоритм можно записать так:

int gcd(int a, int b) {

while (a != b) // We enter the loop when a < b or a > b, but not when a == b

if (a > b) // When a > b we do this

a -= b;

else // When a < b we do that (no "if (a < b)" needed since a != b is checked in while condition)

b -= a;

return a;

}

Тот же алгоритм можно переписать так, чтобы он был ближе к целевым инструкциям ARM :

loop:

// Compare a and b

GT = a > b;

LT = a < b;

NE = a != b;

// Perform operations based on flag results

if (GT) a -= b; // Subtract *only* if greater-than

if (LT) b -= a; // Subtract *only* if less-than

if (NE) goto loop; // Loop *only* if compared values were not equal

return a;

и закодирован на языке ассемблера как:

; assign a to register r0, b to r1

loop: CMP r0, r1 ; set condition "NE" if (a ≠ b),

; "GT" if (a > b),

; or "LT" if (a < b)

SUBGT r0, r0, r1 ; if "GT" (Greater Than), then a = a − b

SUBLT r1, r1, r0 ; if "LT" (Less Than), then b = b − a

BNE loop ; if "NE" (Not Equal), then loop

B lr ; return

который позволяет избежать ветвей вокруг then и else статьи. Если r0 и r1 равны, то ни один из SUB инструкции будут выполнены, что устраняет необходимость в условном переходе для реализации while проверка в верхней части цикла, например, имела SUBLE (меньше или равно).

Одним из способов, с помощью которого код Thumb обеспечивает более плотное кодирование, является удаление четырехбитного селектора из инструкций, не связанных с ветвлением.

Другие особенности

[ редактировать ]Еще одной особенностью набора команд является возможность свертывания сдвигов и поворотов в инструкции обработки данных (арифметические, логические и перемещения между регистрами), так что, например, оператор на языке C :

a += (j << 2);

может быть отображено как однословная инструкция за один цикл: [111]

ADD Ra, Ra, Rj, LSL #2

В результате типичная программа ARM оказывается более плотной, чем ожидалось, с меньшим количеством обращений к памяти; таким образом трубопровод используется более эффективно.

Процессор ARM также имеет функции, редко встречающиеся в других RISC-архитектурах, такие как адресация относительно ПК (действительно, на 32-битной архитектуре). [1] ARM ПК — один из 16 его регистров), а также режимы адресации до и после приращения.

Набор инструкций ARM со временем увеличился. Например, некоторые ранние процессоры ARM (до ARM7TDMI) не имеют инструкции для хранения двухбайтовой величины.

Трубопроводы и другие вопросы реализации

[ редактировать ]ARM7 и более ранние реализации имеют трехэтапный конвейер ; этапы выборки, декодирования и выполнения. Конструкции с более высокой производительностью, такие как ARM9, имеют более глубокие конвейеры: Cortex-A8 имеет тринадцать этапов. Дополнительные изменения реализации для повышения производительности включают более быстрый сумматор и более обширную логику прогнозирования ветвей . Например, разница между ядрами ARM7DI и ARM7DMI заключалась в улучшенном множителе; отсюда и добавленная буква «М».

Сопроцессоры

[ редактировать ]Архитектура ARM (до Armv8) обеспечивает неинтрузивный способ расширения набора команд с помощью «сопроцессоров», к которым можно обращаться с помощью MCR, MRC, MRRC, MCRR и подобных инструкций. Пространство сопроцессора логически разделено на 16 сопроцессоров с номерами от 0 до 15, причем сопроцессор 15 (cp15) зарезервирован для некоторых типичных функций управления, таких как управление кэшами и операциями MMU на процессорах, у которых он есть.

В машинах на базе ARM периферийные устройства обычно подключаются к процессору путем сопоставления их физических регистров с пространством памяти ARM, с пространством сопроцессора или путем подключения к другому устройству (шине), которое, в свою очередь, подключается к процессору. Доступ к сопроцессору имеет меньшую задержку, поэтому некоторые периферийные устройства — например, контроллер прерываний XScale — доступны обоими способами: через память и через сопроцессоры.

В других случаях разработчики микросхем интегрируют аппаратное обеспечение только с помощью механизма сопроцессора. Например, механизм обработки изображений может представлять собой небольшое ядро ARM7TDMI в сочетании с сопроцессором, который выполняет специализированные операции для поддержки определенного набора примитивов транскодирования HDTV.

Отладка

[ редактировать ]Этот раздел нуждается в дополнительных цитатах для проверки . ( Март 2011 г. ) |

Все современные процессоры ARM включают средства аппаратной отладки, позволяющие отладчикам программного обеспечения выполнять такие операции, как остановка, пошаговое выполнение и точка останова кода, начиная с сброса. Эти средства построены с использованием поддержки JTAG , хотя некоторые новые ядра дополнительно поддерживают собственный двухпроводный протокол ARM «SWD». В ядрах ARM7TDMI буква «D» обозначала поддержку отладки JTAG, а «I» обозначала наличие модуля отладки «EmbeddedICE». Для поколений ядер ARM7 и ARM9 EmbeddedICE over JTAG был де-факто стандартом отладки, хотя и не гарантированным с архитектурной точки зрения.

Архитектура ARMv7 определяет базовые средства отладки на архитектурном уровне. К ним относятся точки останова, точки наблюдения и выполнение инструкций в «режиме отладки»; аналогичные возможности были также доступны во EmbeddedICE. Поддерживается отладка как в режиме «остановки», так и в режиме «мониторинга». Фактический транспортный механизм, используемый для доступа к средствам отладки, архитектурно не определен, но реализации обычно включают поддержку JTAG.

Существует отдельная архитектура отладки ARM «CoreSight», которая архитектурно не требуется процессорам ARMv7.

Порт доступа к отладке

[ редактировать ]Порт доступа к отладке (DAP) — это реализация интерфейса отладки ARM. [112] Существует две различные поддерживаемые реализации: последовательный порт отладки JTAG (SWJ-DP) и последовательный порт отладки проводов (SW-DP). [113] CMSIS-DAP — это стандартный интерфейс, который описывает, как различное программное обеспечение отладки на главном ПК может взаимодействовать через USB с прошивкой, работающей на аппаратном отладчике, который, в свою очередь, обменивается данными через SWD или JTAG с процессором ARM Cortex с поддержкой CoreSight. [114] [115] [116]

Инструкции по расширению DSP

[ редактировать ]Чтобы улучшить архитектуру ARM для цифровой обработки сигналов и мультимедийных приложений, в набор команд были добавлены инструкции DSP. [117] Они обозначаются буквой «E» в названии архитектур ARMv5TE и ARMv5TEJ. E-варианты также подразумевают T, D, M и I.

Новые инструкции распространены в архитектурах процессоров цифровых сигналов (DSP). Они включают в себя вариации знакового умножения-накопления , насыщенного сложения и вычитания , а также подсчета ведущих нулей .

Впервые представленное в 1999 году, это расширение основного набора команд контрастировало с более ранним сопроцессором DSP ARM, известным как Piccolo, который использовал отдельный, несовместимый набор команд, выполнение которого включало отдельный программный счетчик. [118] В инструкциях Piccolo использовался отдельный файл регистров из шестнадцати 32-битных регистров, причем некоторые инструкции объединяли регистры для использования в качестве 48-битных аккумуляторов, а другие инструкции обращались к 16-битным полурегистрам. Некоторые инструкции могли работать с двумя такими 16-битными значениями параллельно. Связь с файлом регистров Piccolo включала загрузку в Piccolo и сохранение инструкций сопроцессора Piccolo через два буфера по восемь 32-битных записей. Описанный как напоминающий другие подходы, в частности SH-DSP от Hitachi и 68356 от Motorola, Piccolo не использовал выделенную локальную память и полагался на пропускную способность ядра ARM для извлечения операндов DSP, что влияло на одновременную производительность. [119] Особый набор инструкций Piccolo также оказался не «хорошей целью для компилятора». [118]

SIMD-расширения для мультимедиа

[ редактировать ]Представленный в архитектуре ARMv6, он был предшественником Advanced SIMD, также называемого Neon . [120]

Жазель

[ редактировать ]Jazelle DBX (Direct Bytecode eXecution) — это метод, который позволяет байт-код Java выполнять непосредственно в архитектуре ARM в качестве третьего состояния выполнения (и набора команд) наряду с существующими режимами ARM и Thumb. Поддержка этого состояния обозначается буквой «J» в архитектуре ARMv5TEJ, а также в именах ядер ARM9EJ-S и ARM7EJ-S. Поддержка этого состояния требуется начиная с ARMv6 (за исключением профиля ARMv7-M), хотя новые ядра включают только тривиальную реализацию, не обеспечивающую аппаратное ускорение.

Большой палец

[ редактировать ]Чтобы улучшить плотность компилируемого кода, процессоры, начиная с ARM7TDMI (выпущенного в 1994 г.), [121] ) представили Thumb сжатый набор команд , которые имеют собственное состояние. (Буква «T» в «TDMI» указывает на функцию Thumb.) В этом состоянии процессор выполняет набор инструкций Thumb, компактную 16-битную кодировку для подмножества набора команд ARM. [122] Большинство инструкций Thumb напрямую сопоставлены с обычными инструкциями ARM. Экономия места достигается за счет того, что некоторые операнды инструкций делаются неявными и ограничивают количество возможностей по сравнению с инструкциями ARM, выполняемыми в состоянии набора команд ARM.

В Thumb 16-битные коды операций имеют меньшую функциональность. Например, условными могут быть только переходы, а многие коды операций ограничены доступом только к половине всех регистров общего назначения ЦП. Более короткие коды операций в целом улучшают плотность кода, хотя некоторые операции требуют дополнительных инструкций. В ситуациях, когда ширина порта памяти или шины ограничена менее 32 битами, более короткие коды операций Thumb обеспечивают повышенную производительность по сравнению с 32-битным кодом ARM, поскольку в процессор может потребоваться загружать меньше программного кода из-за ограниченной полосы пропускания памяти.

В отличие от процессорных архитектур с инструкциями переменной длины (16 или 32 бита), таких как Cray-1 и Hitachi SuperH , наборы инструкций ARM и Thumb существуют независимо друг от друга. Встроенное оборудование, такое как Game Boy Advance , обычно имеет небольшой объем оперативной памяти, доступной с полным 32-битным каналом передачи данных; доступ к большинству осуществляется через 16-битный или более узкий вторичный канал данных. В этой ситуации обычно имеет смысл скомпилировать код Thumb и вручную оптимизировать несколько наиболее ресурсоемких разделов с использованием полных 32-битных инструкций ARM, помещая эти более широкие инструкции в память, доступную 32-битной шине.

Первым процессором с декодером инструкций Thumb был ARM7TDMI. Все процессоры, поддерживающие 32-битные наборы инструкций, начиная с ARM9 и включая XScale, имеют декодер инструкций Thumb. Он включает в себя инструкции, заимствованные из Hitachi SuperH (1992), лицензированного ARM. [123] Самые маленькие семейства процессоров ARM (Cortex M0 и M1) реализуют только 16-битный набор инструкций Thumb для максимальной производительности в самых дешевых приложениях. Процессоры ARM, которые не поддерживают 32-битную адресацию, также не используют Thumb.

Большой палец-2

[ редактировать ]Технология Thumb-2 была представлена в ядре ARM1156 , анонсированном в 2003 году. Thumb-2 расширяет ограниченный 16-битный набор команд Thumb дополнительными 32-битными инструкциями, чтобы сделать набор команд более широким, создавая таким образом набор команд переменной длины. . Заявленная цель Thumb-2 заключалась в достижении плотности кода, аналогичной Thumb, с производительностью, аналогичной набору инструкций ARM в 32-битной памяти.

Thumb-2 расширяет набор команд Thumb манипуляциями с битовыми полями, ветвями таблиц и условным выполнением. В то же время набор инструкций ARM был расширен для обеспечения эквивалентной функциональности в обоих наборах инструкций. Новый «Унифицированный язык ассемблера» (UAL) поддерживает генерацию инструкций Thumb или ARM из одного и того же исходного кода; версии Thumb, используемые на процессорах ARMv7, по сути, обладают такими же возможностями, как и код ARM (включая возможность писать обработчики прерываний). Это требует некоторой осторожности и использования новой инструкции «IT» (если-то), которая позволяет выполнять до четырех последовательных инструкций на основе проверяемого условия или его обратного. При компиляции в код ARM это игнорируется, но при компиляции в Thumb генерируется реальная инструкция. Например:

; if (r0 == r1)

CMP r0, r1

ITE EQ ; ARM: no code ... Thumb: IT instruction

; then r0 = r2;

MOVEQ r0, r2 ; ARM: conditional; Thumb: condition via ITE 'T' (then)

; else r0 = r3;

MOVNE r0, r3 ; ARM: conditional; Thumb: condition via ITE 'E' (else)

; recall that the Thumb MOV instruction has no bits to encode "EQ" or "NE".

Все чипы ARMv7 поддерживают набор инструкций Thumb. Все чипы серии Cortex-A, поддерживающие ARMv7, все серии Cortex-R и все серии ARM11 поддерживают как «состояние набора команд ARM», так и «состояние набора команд Thumb», тогда как чипы серии Cortex-M поддерживают только Thumb. набор инструкций. [124] [125] [126]

Среда выполнения Thumb (ThumbEE)

[ редактировать ]ThumbEE (ошибочно называемый Thumb-2EE в некоторой документации ARM), который продавался как Jazelle RCT. [127] (Runtime Compilation Target), был анонсирован в 2005 году и устарел в 2011 году. Впервые он появился в процессоре Cortex-A8 . ThumbEE — это четвертое состояние набора команд, вносящее небольшие изменения в расширенный набор команд Thumb-2. Эти изменения делают набор команд особенно подходящим для кода, генерируемого во время выполнения (например, JIT-компиляции ) в управляемых средах выполнения . ThumbEE является целевой средой для таких языков, как Java , C# , Perl и Python , и позволяет JIT-компиляторам выводить скомпилированный код меньшего размера без снижения производительности. [ нужна ссылка ]

Новые функции, предоставляемые ThumbEE, включают автоматическую проверку нулевого указателя для каждой инструкции загрузки и сохранения, инструкцию для выполнения проверки границ массива и специальные инструкции, вызывающие обработчик. Кроме того, поскольку ThumbEE использует технологию Thumb-2, он обеспечивает доступ к регистрам r8–r15 (где хранится состояние виртуальной машины Java Jazelle/DBX). [128] Обработчики — это небольшие разделы часто вызываемого кода, обычно используемые для реализации языков высокого уровня, например, для выделения памяти для нового объекта. Эти изменения происходят в результате перепрофилирования нескольких кодов операций и знания того, что ядро находится в новом состоянии ThumbEE.

23 ноября 2011 года компания Arm запретила любое использование набора инструкций ThumbEE. [129] и Armv8 удаляет поддержку ThumbEE.

С плавающей запятой (VFP)

[ редактировать ]Технология VFP (Vector Floating Point) — это расширение сопроцессора с плавающей запятой (FPU) для архитектуры ARM. [130] (в Armv8 реализовано по-другому — сопроцессоры там не определены). Он обеспечивает недорогие вычисления с плавающей запятой одинарной и двойной точности, полностью соответствующие стандарту ANSI/IEEE Std 754-1985 для двоичной арифметики с плавающей запятой . VFP обеспечивает вычисления с плавающей запятой, подходящие для широкого спектра приложений, таких как КПК, смартфоны, сжатие и распаковка голоса, трехмерная графика и цифровой звук, принтеры, телеприставки и автомобильные приложения. Архитектура VFP была предназначена для поддержки выполнения коротких инструкций в «векторном режиме», но они работали с каждым векторным элементом последовательно и, таким образом, не обеспечивали производительность истинного векторного параллелизма одной инструкции и нескольких данных (SIMD). Поэтому этот векторный режим был удален вскоре после его появления. [131] будет заменен гораздо более мощным Advanced SIMD, также называемым Neon .

Некоторые устройства, такие как ARM Cortex-A8, имеют урезанный модуль VFPLite вместо полноценного модуля VFP и требуют примерно в десять раз больше тактовых циклов на операцию с плавающей запятой. [132] Архитектура до Armv8 реализовала операции с плавающей запятой/SIMD с интерфейсом сопроцессора. Другие модули с плавающей запятой и/или SIMD, обнаруженные в процессорах на базе ARM, использующих интерфейс сопроцессора, включают FPA , FPE, iwMMXt , некоторые из которых были реализованы в программном обеспечении путем перехвата, но могли быть реализованы аппаратно. Они предоставляют некоторые из тех же функций, что и VFP, но несовместимы с ним по коду операций . FPA10 также обеспечивает повышенную точность , но правильное округление (требуемое IEEE 754) реализует только с одинарной точностью. [133]

- ВФПв1

- Устаревший

- ВФПв2

- Необязательное расширение набора инструкций ARM в архитектурах ARMv5TE, ARMv5TEJ и ARMv6. VFPv2 имеет 16 64-битных регистров FPU.

- VFPv3 или VFPv3-D32

- Реализовано на большинстве процессоров Cortex-A8 и A9 ARMv7. Он обратно совместим с VFPv2, за исключением того, что он не может перехватывать исключения с плавающей запятой. VFPv3 в стандартной комплектации имеет 32 64-битных регистра FPU, добавляет инструкции VCVT для преобразования между скалярными, плавающими и двойными значениями, добавляет к VMOV непосредственный режим, позволяющий загружать константы в регистры FPU.

- ВФПв3-Д16

- То же, что и выше, но только с 16 64-битными регистрами FPU. Реализовано на процессорах Cortex-R4 и R5 и Tegra 2 (Cortex-A9).

- ВФПв3-F16

- Необычно; он поддерживает IEEE754-2008 с плавающей запятой половинной точности (16 бит) в качестве формата хранения.

- VFPv4 или VFPv4-D32

- Реализованный на процессорах Cortex-A12 и A15 ARMv7, Cortex-A7 опционально имеет VFPv4-D32 в случае FPU с Neon. [134] как поддержку половинной точности в качестве формата хранения, так и объединенные инструкции умножения-накопления . VFPv4 в стандартной комплектации имеет 32 64-битных регистра FPU, добавляет к функциям VFPv3

- ВФПв4-Д16

- То же, что и выше, но имеет только 16 64-битных регистров FPU. Реализовано на процессорах Cortex-A5 и A7 в случае FPU без Neon. [134]

- ВФПв5-Д16-М

- Реализовано на Cortex-M7, когда существует опция ядра с плавающей запятой одинарной и двойной точности.

В Debian Linux и его производных, таких как Ubuntu и Linux Mint , Armhf ( ARM hard float ) относится к архитектуре ARMv7, включая дополнительное аппаратное расширение VFP3-D16 для операций с плавающей запятой (и Thumb-2), указанное выше. Пакеты программного обеспечения и инструменты кросс-компиляции используют суффиксы Armhf и Arm/Armel для различения. [135]

Расширенный SIMD (неон)

[ редактировать ]Расширение Advanced SIMD (также известное как Neon или «MPE» Media Processing Engine) представляет собой комбинированный 64- и 128-битный набор команд SIMD, который обеспечивает стандартизированное ускорение для приложений обработки мультимедиа и сигналов. Neon включен во все устройства Cortex-A8, но является дополнительным в устройствах Cortex-A9. [136] Neon может выполнять декодирование звука MP3 на процессорах, работающих на частоте 10 МГц, и может запускать (AMR) GSM речевой кодек адаптивной многоскоростной передачи на частоте 13 МГц. Он имеет обширный набор команд, отдельные файлы регистров и независимое аппаратное обеспечение. [137] Neon поддерживает 8-, 16-, 32- и 64-битные целые числа и данные одинарной точности (32-битные) с плавающей запятой, а также операции SIMD для обработки аудио и видео, а также обработки графики и игр. В Neon SIMD поддерживает до 16 операций одновременно. Аппаратное обеспечение Neon использует те же регистры с плавающей запятой, что и VFP. Такие устройства, как ARM Cortex-A8 и Cortex-A9, поддерживают 128-битные векторы, но одновременно могут выполняться с 64 битами. [132] тогда как более новые устройства Cortex-A15 могут выполнять 128 бит за раз. [138] [139]

Особенность Neon в устройствах Armv7 заключается в том, что он сбрасывает все ненормальные числа в ноль, и в результате компилятор GCC не будет использовать его, если только -funsafe-math-optimizations, позволяющий терять денормали, включен. «Расширенный» Neon определен, поскольку Armv8 не имеет этой особенности, но начиная с GCC 8.2 тот же флаг все еще требуется для включения инструкций Neon. [140] С другой стороны, GCC считает Neon безопасным для AArch64 для Armv8.

ProjectNe10 — первый проект ARM с открытым исходным кодом (с момента его создания; при этом они приобрели более старый проект, который теперь называется Mbed TLS ). Библиотека Ne10 представляет собой набор общих полезных функций, написанных на Neon и C (для совместимости). Библиотека была создана, чтобы позволить разработчикам использовать оптимизацию Neon без изучения Neon, но она также служит набором высокооптимизированных примеров встроенного и ассемблерного кода Neon для общих процедур DSP, арифметики и обработки изображений. Исходный код доступен на GitHub. [141]

ARM Гелиевая технология

[ редактировать ]Гелий — это векторное расширение M-профиля (MVE). Он добавляет более 150 скалярных и векторных инструкций. [142]

Расширения безопасности

[ редактировать ]TrustZone (для профиля Cortex-A)

[ редактировать ]Расширения безопасности, продаваемые как технология TrustZone, входят в архитектуру профиля приложения ARMv6KZ и более поздних версий. Он обеспечивает недорогую альтернативу добавлению еще одного выделенного ядра безопасности в SoC за счет предоставления двух виртуальных процессоров, поддерживаемых аппаратным контролем доступа. Это позволяет ядру приложения переключаться между двумя состояниями, называемыми мирами (чтобы избежать путаницы с другими названиями доменов возможностей), чтобы предотвратить утечку информации из более доверенного мира в менее доверенный мир. Этот переключатель миров обычно ортогонален всем остальным возможностям процессора, поэтому каждый мир может работать независимо от другого, используя одно и то же ядро. Затем память и периферийные устройства получают информацию об операционной среде ядра и могут использовать ее для обеспечения контроля доступа к секретам и коду на устройстве. [143]

Как правило, мощная операционная система запускается в менее доверенном мире, а меньший код, специализирующийся на безопасности, — в более доверенном мире с целью уменьшить поверхность атаки . Типичные приложения включают функцию DRM для контроля использования мультимедиа на устройствах на базе ARM, [144] и предотвращение любого несанкционированного использования устройства.

На практике, поскольку конкретные детали реализации проприетарных реализаций TrustZone не были публично раскрыты для ознакомления, неясно, какой уровень уверенности обеспечивается для данной модели угроз , но они не застрахованы от атак. [145] [146]

Открытая виртуализация [147] — это реализация доверенной мировой архитектуры с открытым исходным кодом для TrustZone.

AMD лицензировала и включила технологию TrustZone в свою технологию Secure Processor Technology . [148] AMD В некоторых, но не во всех продуктах, APU включают в себя процессор Cortex-A5 для обеспечения безопасной обработки. [149] [150] [151] Фактически, ядро Cortex-A5 TrustZone было включено в более ранние продукты AMD, но не было включено из-за ограничений по времени. [150]

Samsung Knox использует TrustZone для таких целей, как обнаружение изменений в ядре, хранение сертификатов и подтверждение ключей. [152]

TrustZone для Armv8-M (для профиля Cortex-M)

[ редактировать ]Расширение безопасности, продаваемое как TrustZone для технологии Armv8-M, было представлено в архитектуре Armv8-M. Несмотря на то, что он содержит концепции, аналогичные TrustZone для Armv8-A, он имеет другой архитектурный дизайн, поскольку переключение между мирами выполняется с использованием инструкций ветвления, а не с использованием исключений. Он также поддерживает безопасную обработку чередующихся прерываний из любого мира независимо от текущего состояния безопасности. Вместе эти функции обеспечивают вызовы в безопасный мир с низкой задержкой и быструю обработку прерываний. ARM предоставляет эталонный стек защищенного мирового кода в виде доверенной прошивки для сертификатов M и PSA .

Защита страницы без выполнения

[ редактировать ]Начиная с ARMv6, архитектура ARM поддерживает защиту страниц без выполнения , которая называется XN , что означает eXecute Never . [153]

Расширение большого физического адреса (LPAE)

[ редактировать ]Расширение большого физического адреса (LPAE), которое увеличивает размер физического адреса с 32 до 40 бит, было добавлено в архитектуру Armv7-A в 2011 году. [154]

Размер физического адреса может быть даже больше в процессорах на базе 64-битной (Armv8-A) архитектуры. Например, в Cortex-A75 и Cortex-A65AE она составляет 44 бита. [155]

Армв8-Р и Армв8-М

[ редактировать ]Архитектуры Armv8-R и Armv8-M , анонсированные после архитектуры Armv8-A, имеют некоторые общие функции с Armv8-A. Однако Armv8-M не включает никаких 64-битных инструкций AArch64, а Armv8-R изначально не включал никаких инструкций AArch64; эти инструкции были добавлены в Armv8-R позже.

Армв8.1-М

[ редактировать ]Архитектура Armv8.1-M, анонсированная в феврале 2019 года, представляет собой усовершенствование архитектуры Armv8-M. Он приносит новые функции, в том числе:

- Новое расширение набора векторных команд. Векторное расширение M-профиля (MVE), или Helium, предназначено для приложений обработки сигналов и машинного обучения.

- Дополнительные улучшения набора команд для циклов и ветвей (расширение ветвей с низкими издержками).

- Инструкции для поддержки чисел с плавающей запятой половинной точности .

- Улучшен набор инструкций для управления TrustZone для модулей с плавающей запятой (FPU).

- Новый атрибут памяти в модуле защиты памяти (MPU).

- Улучшения в отладке, включая блок мониторинга производительности (PMU), непривилегированное расширение отладки и дополнительную поддержку отладки, ориентированы на разработку приложений для обработки сигналов.

- Расширение надежности, доступности и удобства обслуживания (RAS).

64/32-битная архитектура

[ редактировать ]

Armv8

[ редактировать ]Армв8-А

[ редактировать ]Объявлено в октябре 2011 г. [14] Armv8-A (часто называемый ARMv8, хотя также доступен Armv8-R) представляет собой фундаментальное изменение в архитектуре ARM. Он поддерживает два состояния выполнения : 64-битное состояние с именем AArch64 и 32-битное состояние с именем AArch32 . В состоянии AArch64 A64 поддерживается новый 64-битный набор инструкций ; в состоянии AArch32 поддерживаются два набора инструкций: исходный 32-битный набор команд с именем A32 и 32-битный набор инструкций Thumb-2 с именем T32 . AArch32 обеспечивает совместимость пользовательского пространства с Armv7-A. Состояние процессора может измениться при изменении уровня исключения; это позволяет 32-битным приложениям выполняться в состоянии AArch32 в 64-битной ОС, ядро которой выполняется в состоянии AArch64, а также позволяет 32-битной ОС работать в состоянии AArch32 под управлением 64-битного гипервизора, работающего в состоянии AArch64. . [1] ARM анонсировала свои ядра Cortex-A53 и Cortex-A57 30 октября 2012 года. [74] Apple была первой, кто выпустил ядро, совместимое с Armv8-A, в потребительском продукте ( Apple A7 в iPhone 5S ). AppliedMicro , используя FPGA , первым продемонстрировал Armv8-A. [156] Первой SoC Armv8-A от Samsung является Exynos 5433, используемый в Galaxy Note 4 , который имеет два кластера по четыре ядра Cortex-A57 и Cortex-A53 в конфигурации big.LITTLE ; но он будет работать только в режиме AArch32. [157]

Как для AArch32, так и для AArch64 Armv8-A поддерживает стандарт VFPv3/v4 и расширенный SIMD (Neon). Он также добавляет инструкции криптографии, поддерживающие AES , SHA-1 / SHA-256 и арифметику с конечными полями . [158] AArch64 был представлен в Armv8-A и его последующей версии. AArch64 не включен в 32-битные архитектуры Armv8-R и Armv8-M.

Процессор ARMv8-A может поддерживать один или оба AArch32 и AArch64; он может поддерживать AArch32 и AArch64 на более низких уровнях исключений и только AArch64 на более высоких уровнях исключений. [159] Например, ARM Cortex-A32 поддерживает только AArch32. [160] ARM Cortex-A34 поддерживает только AArch64, [161] а ARM Cortex-A72 поддерживает как AArch64, так и AArch32. [162] Процессор ARMv9-A должен поддерживать AArch64 на всех уровнях исключений и может поддерживать AArch32 на уровне EL0. [159]

Армв8-Р

[ редактировать ]В профиль Armv8-R была добавлена дополнительная поддержка AArch64, причем первым ядром ARM, реализующим ее, стал Cortex-R82. [163] Он добавляет набор инструкций A64.

Армв9

[ редактировать ]Армв9-А

[ редактировать ]В обновленной архитектуре, анонсированной в марте 2021 года, особое внимание уделяется безопасному выполнению и разделениям . [164] [165]

Система вооружения готова

[ редактировать ]Arm SystemReady, ранее называвшаяся Arm ServerReady, — это программа сертификации, которая помогает внедрить стандартные готовые операционные системы и гипервизоры в системы на базе Arm, от серверов центров обработки данных до промышленных периферийных устройств и устройств Интернета вещей. Ключевыми строительными блоками программы являются спецификации минимальных требований к оборудованию и встроенному ПО, на которые могут опираться операционные системы и гипервизоры. Эти характеристики: [166]

- Базовая системная архитектура (BSA) [167] и дополнения для конкретного сегмента рынка (например, дополнение Server BSA) [168]

- Базовые требования к загрузке (BBR) [169] и базовые требования безопасности загрузки (BBR) [170]

Эти спецификации разработаны совместно компанией Arm и ее партнерами из Консультативного комитета по системной архитектуре (SystemArchAC).

Architecture Compliance Suite (ACS) — это инструменты тестирования, которые помогают проверить соответствие этим спецификациям. Спецификация требований Arm SystemReady документирует требования сертификации. [171]

представила Эту программу компания Arm в 2020 году на первом мероприятии DevSummit . Его предшественник Arm ServerReady был представлен в 2018 году на мероприятии Arm TechCon. В настоящее время в эту программу входят четыре группы:

- SystemReady SR: этот диапазон предназначен для серверов и рабочих станций, поддерживающих операционные системы и гипервизоры, требующие интерфейсов UEFI , ACPI и SMBIOS . Windows, Red Hat Enterprise Linux и VMware ESXi-Arm требуют этих интерфейсов, хотя другие дистрибутивы Linux и BSD также могут их поддерживать. [ нужны разъяснения ]

- SystemReady LS (LinuxBoot System): этот диапазон предназначен для серверов, которые гиперскейлеры используют для поддержки операционных систем Linux, которым требуется прошивка LinuxBoot вместе с интерфейсами ACPI и SMBIOS.

- SystemReady ES (встроенная система): этот диапазон предназначен для промышленных периферийных устройств и устройств Интернета вещей, которые поддерживают операционные системы и гипервизоры, требующие интерфейсов UEFI, ACPI и SMBIOS. Windows IoT Enterprise, Red Hat Enterprise Linux и VMware ESXi-Arm требуют этих интерфейсов, хотя другие дистрибутивы Linux и BSD также могут их поддерживать. [ нужны разъяснения ]

- SystemReady IR (IoT Ready): эта полоса предназначена для промышленных периферийных устройств и устройств IoT, которые поддерживают операционные системы, требующие интерфейсы UEFI и дерева устройств . Также могут поддерживаться встроенный Linux (например, Yocto ) и некоторые дистрибутивы Linux/BSD (например, Fedora, Ubuntu, Debian и OpenSUSE). [ нужны разъяснения ]

Сертифицированный PSA

[ редактировать ]Сертифицированный PSA , ранее называвшийся Архитектурой безопасности платформы, представляет собой независимую от архитектуры структуру безопасности и схему оценки. Он предназначен для обеспечения безопасности устройств Интернета вещей (IoT), построенных на процессорах «система на кристалле» (SoC). [172] Он был введен для повышения безопасности в тех случаях, когда полностью доверенная среда выполнения слишком велика или сложна. [173]

Архитектура была представлена компанией Arm в 2017 году на ежегодном мероприятии TechCon . [173] [174] Хотя схема не зависит от архитектуры, она впервые была реализована на процессорных ядрах Arm Cortex-M, предназначенных для использования в микроконтроллерах. Сертификат PSA включает в себя свободно доступные модели угроз и анализы безопасности, демонстрирующие процесс принятия решения о функциях безопасности в распространенных продуктах Интернета вещей. [175] Он также предоставляет бесплатно загружаемые пакеты интерфейса прикладного программирования (API), архитектурные спецификации, реализации встроенного ПО с открытым исходным кодом и соответствующие наборы тестов. [176]

После разработки структуры безопасности архитектуры в 2017 году схема обеспечения сертификации PSA была запущена два года спустя в Embedded World в 2019 году. [177] PSA Certified предлагает многоуровневую схему оценки безопасности для поставщиков чипов, поставщиков ОС и производителей устройств Интернета вещей. [178] Презентация Embedded World познакомила поставщиков чипов с сертификацией уровня 1. Тогда же был представлен проект защиты второго уровня. [179] Сертификация уровня 2 стала применимым стандартом в феврале 2020 года. [180]

Сертификация была создана совместными заинтересованными сторонами PSA, чтобы обеспечить индивидуальный подход к безопасности для разнообразного набора продуктов Интернета вещей. Спецификации, сертифицированные PSA, не зависят от реализации и архитектуры, поэтому их можно применять к любому чипу, программному обеспечению или устройству. [181] [179] Сертификация также устраняет фрагментацию отрасли среди производителей и разработчиков продуктов Интернета вещей . [182]

Поддержка операционной системы

[ редактировать ]32-битные операционные системы

[ редактировать ]Исторические операционные системы

[ редактировать ]Первый 32-битный персональный компьютер на базе ARM, Acorn Archimedes , изначально предназначался для работы под управлением амбициозной операционной системы под названием ARX . Машины поставлялись с ОС RISC , которая также использовалась в более поздних системах на базе ARM от Acorn и других производителей. Некоторые ранние машины Acorn также могли использовать порт Unix под названием RISC iX . (Не следует путать с RISC/os , современным вариантом Unix архитектуры MIPS.)

Встроенные операционные системы

[ редактировать ]32-битная архитектура ARM поддерживается большим количеством встроенных операционных систем и операционных систем реального времени , в том числе:

- А2

- Андроид

- ЧибиОС/РТ

- боги

- ДРИС

- ЭКоС

- embOS

- FreeBSD

- FreeRTOS

- ЧЕСТНОСТЬ

- Линукс

- Операционные системы микроконтроллеров

- Мбед

- МИНИКС 3

- MQX

- Нуклеус ПЛЮС

- NutX

- ОКЛ4

- Встроенная операционная система (OSE)

- ОС-9 [183]

- Фарос [184]

- План 9

- PikeOS [185]

- QNX

- БУНТ

- РТЭМС

- RTXC-кадры

- СКИПТА [186]

- ThreadX

- ТизенРТ

- Т-Ядро

- Вксворкс

- Windows встроенный компактный

- Windows 10 IoT ядро

- Зефир

Операционные системы мобильных устройств

[ редактировать ]По состоянию на март 2024 года 32-битная архитектура ARM была основной аппаратной средой для большинства операционных систем мобильных устройств, таких как следующие, но многие из этих платформ, таких как Android и Apple iOS, перешли на 64-битную архитектуру ARM:

Раньше, но сейчас снято с производства:

- Если есть

- ОС BlackBerry / BlackBerry 10

- ОС Firefox

- МиГо

- Ньютон ОС

- iOS 10 и более ранние версии

- Симбиан

- Windows 10 Мобильная

- Windows РТ

- Windows Телефон

- Windows Мобайл

Настольные и серверные операционные системы

[ редактировать ]32-битная архитектура ARM поддерживается ОС RISC и несколькими Unix-подобными операционными системами, включая:

- FreeBSD

- NetBSD

- OpenBSD

- OpenSolaris [187]

- несколько дистрибутивов Linux , например:

64-битные операционные системы

[ редактировать ]Встроенные операционные системы

[ редактировать ]- ЧЕСТНОСТЬ [188]

- ИЛИ [189]

- СКИПТА [186]

- продатьL4 [190]

- Фарос [184]

- FreeRTOS

- QNX [191]

- Вксворкс [192]

- Зефир

Операционные системы мобильных устройств

[ редактировать ]- Android поддерживает Armv8-A в Android Lollipop (5.0) и более поздних версиях.

- iOS поддерживает Armv8-A в iOS 7 и более поздних версиях на 64-битных процессорах Apple SoC . iOS 11 и более поздних версий, а также iPadOS поддерживают только 64-разрядные процессоры и приложения ARM.

- Мобиан

- ПостмаркетОС

- Арка Linux ARM

- Манджаро [193]

Настольные и серверные операционные системы