х86

| Дизайнер | Интел , АМД |

|---|---|

| Биты | 16-битная , 32-битная и 64-битная версии |

| Представлено | 1978 (16-bit), 1985 (32-bit), 2003 (64-bit) |

| Дизайн | ЦИСК |

| Тип | Регистр-память |

| Кодирование | Переменная (от 1 до 15 байт) |

| Ветвление | Код состояния |

| Порядок байтов | Маленький |

| Размер страницы | 8086 – i286 : Нет i386 , i486 : страницы по 4 КБ P5 Pentium : добавлены страницы по 4 МБ. (Устаревший PAE : 4 КБ→2 МБ) x86-64 : добавлены страницы по 1 ГБ. |

| Расширения | x87 , IA-32 , x86-64 , x86-S , MMX , 3DNow! , SSE бит MCA , ACPI , SSE2 , NX , SMT , SSE3 , SSSE3 , SSE4 , SSE4.2 , AES , CLMUL , RDRAND , SHA , MPX , SME , SGX , XOP , F16C , - BMI NI FMA, AVX , AVX2 , AVX-VNNI , AVX512 , AVX10 , AMX , VT-x , VT-d , AMD-V , AMD-Vi , TSX , ASF , TXT , APX |

| Открыть | Частично. Для некоторых расширенных функций x86 может потребоваться лицензия Intel; Для x86-64 может потребоваться дополнительная лицензия AMD. Процессор Pentium Pro (и NetBurst ) присутствует на рынке уже более 21 года. [ 1 ] и поэтому не может быть объектом патентных претензий. Таким образом, подмножество i686 архитектуры x86 полностью открыто. Процессоры серии Opteron . 1000 присутствуют на рынке уже более 21 года и поэтому не могут быть предметом патентных претензий Таким образом, подмножество AMD K8 архитектуры x86 полностью открыто. [ 2 ] |

| Регистры | |

| общего назначения |

|

| Плавающая точка | |

x86 (также известный как 80x86 [ 3 ] или семейство 8086 [ 4 ] ) — это семейство компьютера со сложным набором команд (CISC). архитектур набора команд [ а ] Первоначально разработанный Intel на основе микропроцессора 8086 с 8-битной внешней шиной и его варианта 8088 . 8086 был представлен в 1978 году как полностью 16-битное расширение 8-битного микропроцессора Intel 8080 с сегментацией памяти как решением для адресации большего объема памяти, чем может быть охвачен простым 16-битным адресом. Термин «x86» появился потому, что имена нескольких преемников процессора Intel 8086 заканчиваются на «86», включая 80186 , 80286 , 80386 и 80486 . В просторечии их звали «186», «286», «386» и «486».

Этот термин не является синонимом совместимости с IBM PC , поскольку он подразумевает множество другого компьютерного оборудования . Во встроенных системах и компьютерах общего назначения использовались чипы x86 до появления рынка ПК-совместимых технологий . [ б ] некоторые из них до дебюта IBM PC (1981).

По состоянию на июнь 2022 г. [update]Большинство продаваемых настольных и портативных компьютеров основаны на архитектуре семейства x86. [ 5 ] в то время как в мобильных категориях, таких как смартфоны и планшеты, доминирует ARM . В верхнем сегменте x86 продолжает доминировать в сегментах рабочих станций и облачных вычислений с интенсивными вычислениями . [ 6 ]

Обзор

[ редактировать ]В 1980-х и начале 1990-х годов, когда процессоры 8088 и 80286 еще широко использовались, термин x86 обычно обозначал любой процессор, совместимый с 8086. Однако сегодня x86 обычно подразумевает двоичную совместимость с -битным набором команд 80386 32 . Это связано с тем, что этот набор команд стал чем-то вроде наименьшего общего знаменателя для многих современных операционных систем, а также, вероятно, с тем, что этот термин стал общепринятым после появления 80386 в 1985 году.

Через несколько лет после появления 8086 и 8088 компания Intel усложнила свою схему наименования и терминологию, поскольку «iAPX» амбициозного, но злополучного процессора Intel iAPX 432 был опробован на более успешном семействе чипов 8086. [ с ] применяется как своего рода префикс системного уровня. Система 8086, включающая сопроцессоры , такие как 8087 и 8089 , и более простые системные чипы, специфичные для Intel. [ д ] поэтому была описана как система iAPX 86. [ 7 ] [ и ] Существовали также термины iRMX (для операционных систем), iSBC (для одноплатных компьютеров) и iSBX (для многомодульных плат на базе архитектуры 8086), все вместе под заголовком Microsystem 80 . [ 8 ] [ 9 ] Однако эта схема наименования была весьма временной и просуществовала несколько лет в начале 1980-х годов. [ ж ]

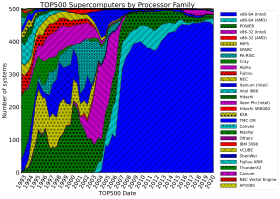

Хотя 8086 был в первую очередь разработан для встраиваемых систем и небольших многопользовательских или однопользовательских компьютеров, в основном как ответ на успешный 8080-совместимый Zilog Z80 . [ 10 ] Линия x86 вскоре расширилась в возможностях и вычислительной мощности. Сегодня x86 повсеместно распространен как в стационарных, так и в портативных персональных компьютерах, а также используется в компьютерах среднего класса , рабочих станциях , серверах и большинстве новых суперкомпьютерных кластеров списка ТОП500 . Большое количество программного обеспечения , включая большой список операционных систем x86, использует оборудование на базе x86.

Однако современный x86 относительно редко встречается во встроенных системах , а небольшие приложения с низким энергопотреблением (использующие крошечные батареи) и рынки недорогих микропроцессоров, таких как бытовая техника и игрушки, не имеют значительного присутствия x86. [ г ] Здесь распространены простые 8- и 16-битные архитектуры, а также более простые RISC-архитектуры, такие как RISC-V , хотя x86-совместимые VIA C7 , VIA Nano , AMD Geode . , Athlon Neo и Intel Atom являются примерами 32-битных архитектур и 64-битные конструкции, используемые в некоторых относительно маломощных и недорогих сегментах.

Было предпринято несколько попыток, в том числе со стороны Intel, положить конец доминированию на рынке «неэлегантной» архитектуры x86, созданной непосредственно на основе первых простых 8-битных микропроцессоров. Примером этого является iAPX 432 (проект, первоначально называвшийся Intel 8800) . [ 11 ] ), Intel 960 , Intel 860 и архитектура Intel/Hewlett-Packard Itanium . Однако постоянное совершенствование микроархитектуры x86 , схемотехники и производства полупроводников затруднит замену x86 во многих сегментах. 64-битное расширение AMD x86 (на которое Intel в конечном итоге ответила совместимым дизайном) [ 12 ] а масштабируемость чипов x86 в форме современных многоядерных процессоров подчеркивает x86 как пример того, как постоянное совершенствование установленных отраслевых стандартов может противостоять конкуренции со стороны совершенно новых архитектур. [ 13 ]

Хронология

[ редактировать ]Эта статья нуждается в дополнительных цитатах для проверки . ( март 2020 г. ) |

В таблице ниже перечислены модели процессоров и серии моделей, реализующие различные архитектуры семейства x86, в хронологическом порядке. Каждая линейка характеризуется значительно улучшенными или коммерчески успешными конструкциями микроархитектуры процессора.

| Эра | Введение | Известные модели процессоров | Адресное пространство | Примечательные особенности | |||

|---|---|---|---|---|---|---|---|

| Линейный | Виртуальный | Физический | |||||

| х86-16 | 1-й | 1978 | Интел 8086 , Интел 8088 (1979 г.) | 16-битный | ЧТО | 20-битный | 16-битный ISA , IBM PC (8088), IBM PC/XT (8088) |

| 1982 | Интел 80186 , Интел 80188 НЭК В20 /В30 (1983) |

8086-2 ISA, встроенный (80186/80188) | |||||

| 2-й | Intel 80286 и клоны | 30-битный | 24-битный | защищенный режим , IBM PC/XT 286 , IBM PC/AT | |||

| ИА-32 | 3-й | 1985 | Intel 80386 , AMD Am386 (1991 г.) | 32-битный | 46-битный | 32-битный | 32-разрядная ISA , подкачка, IBM PS/2 |

| 4-й (конвейерная обработка, кеш) | 1989 | Интел 80486 Cyrix Cx486S , DLC (1992) AMD Am486 (1993 г.), Am5x86 (1995 г.) |

конвейерная обработка , встроенный x87 FPU (486DX), встроенный кэш | ||||

| 5-е место ( Суперскаляр ) |

1993 | Intel Pentium , Pentium 2010 (1996 г.) | Суперскалярная , 64-битная шина данных , более быстрый FPU, MMX (Pentium MMX), APIC , SMP | ||||

| 1994 | НексГен Nx586 АМД 5к86 / К5 (1996 г.) |

Дискретная микроархитектура ( μ-op трансляция ) | |||||

| 1995 | Сайрикс Cx5x86 Cyrix 6x86 /MX (1997 г.) / MII (1998 г.) |

динамическое исполнение | |||||

| 6-е место ( PAE , перевод μ-op) |

1995 | Интел Пентиум Про | 36-битный ( ПАЕ ) | трансляция μ-op, инструкции условного перемещения, динамическое выполнение , спекулятивное выполнение , 3-сторонний суперскаляр x86, суперскалярный FPU, PAE , встроенный кэш L2 | |||

| 1997 | Intel Pentium II , Pentium III (1999 г.) Селерон (1998 г.), Ксеон (1998 г.) |

встроенный (Pentium II) или встроенный (Celeron) кэш L2, SSE (Pentium III), слот 1 , Socket 370 или слот 2 (Xeon) | |||||

| 1997 | AMD K6 / K6-2 (1998 г.)/ K6-III (1999 г.) | 32-битный | 3DСейчас! , 3-уровневая кэш-система (K6-III) | ||||

| Расширенная платформа | 1999 | AMD Атлон Атлон ХР / МП (2001 г.) Терпеть (2000) Семпрон (2004) |

36-битный | MMX+, 3DNow!+, шина с двойной накачкой, слот A или разъем A | |||

| 2000 | Трансмутационный Крузо | 32-битный | CMS Процессор платформы x86 на базе , ядро VLIW -128, встроенный контроллер памяти, встроенная логика моста PCI | ||||

| Интел Пентиум 4 | 36-битный | SSE2 , HTT (Northwood), NetBurst, шина с четырьмя накачками, Trace Cache, Socket 478 | |||||

| 2003 | Интел Пентиум М Intel Core (2006 г.) Двухъядерный Пентиум (2007 г.) |

μ-op fusion , бит XD (Дотан) (Intel Core «Йона») | |||||

| Эффективность передачи | CMS 6.0.4, VLIW -256, бит NX , HT | ||||||

| ИА-64 | 64-битный переход 1999–2005 |

2001 | Intel Itanium (2001–2017 гг.) | 52-битный | 64-битная архитектура EPIC , 128-битный набор инструкций VLIW, встроенное аппаратное обеспечение IA-32 для поддержки операционных систем x86 и приложений x86 (ранние поколения), программное обеспечение IA-32 EL для поддержки приложений x86 (Itanium 2), регистровые файлы Itanium переназначаются в регистры x86 | ||

| х86-64 | 64-битная расширенная версия с 2001 года |

x86-64 — это 64-битная расширенная архитектура x86, ее режим Legacy сохраняет всю и неизмененную архитектуру x86. Собственная архитектура процессоров x86-64: пребывание в 64-битном режиме, отсутствие режима доступа при сегментации, представление 64-битного линейного адресного пространства с разрешением архитектуры; адаптированная архитектура IA-32, находящаяся в режиме совместимости наряду с 64-битным режимом, обеспечивает поддержку большинства приложений x86. | |||||

| 2003 | Атлон 64 / FX / X2 (2005 г.), Оптерон Семпрон (2004) / X2 (2008) Турион 64 (2005 г.) / X2 (2006 г.) |

40-битный | AMD64 представленных исключительно как процессоры x86), встроенный контроллер памяти, HyperTransport , встроенный двухъядерный процессор (X2), V (Athlon 64 Orleans), Socket 754/939/940 (за исключением некоторых процессоров Sempron , AMD - или AM2 | ||||

| 2004 | Пентиум 4 (Прескотт) Селерон Д , Пентиум Д (2005 г.) |

36-битный | EM64T (включен на некоторых моделях Pentium 4 и Celeron D), SSE3 , 2-го поколения. Конвейерная обработка NetBurst, двухъядерный процессор (на кристалле: Pentium D 8xx, на кристалле: Pentium D 9xx), Intel VT (Pentium 4 6x2), разъем LGA 775 | ||||

| 2006 | Intel Core 2 Двухъядерный Пентиум (2007 г.) Двухъядерный процессор Celeron (2008 г.) |

Intel 64 (<<== EM64T), SSSE3 (65 нм), широкое динамическое исполнение, объединение микроопераций, объединение макроопераций в 16-битном и 32-битном режиме, [ 14 ] [ 15 ] встроенный четырехъядерный процессор (Core 2 Quad), интеллектуальный общий кэш L2 (Intel Core 2 «Merom») | |||||

| 2007 | AMD Феном / II (2008) Атлон II (2009 г.) Турион II (2009) |

48-битный | Монолитный четырехъядерный (X4)/трехъядерный (X3), SSE4a , Rapid Virtualization Indexing (RVI), HyperTransport 3, AM2+ или AM3 | ||||

| 2008 | Intel Core 2 (45 нм) | 40-битный | ССЕ4.1 | ||||

| Интел Атом | процессор нетбука или интеллектуального устройства с низким энергопотреблением, ядро P54C используется повторно | ||||||

| Intel Core i7 Ядро i5 (2009 г.) Ядро i3 (2010 г.) |

QuickPath, встроенный GMCH ( Clarkdale ), SSE4.2 , расширенные таблицы страниц (EPT) для виртуализации, объединение макроопераций в 64-битном режиме, [ 14 ] [ 15 ] (Intel Xeon «Bloomfield» с микроархитектурой Nehalem) | ||||||

| ВИА Нано | аппаратное шифрование ; адаптивное управление питанием | ||||||

| 2010 | AMD FX | 48-битный | восьмиядерный, CMT (кластерная многопоточная обработка), FMA, OpenCL, AM3+ | ||||

| 2011 | AMD APU серии A и E ( Llano ) | 40-битный | встроенный графический процессор, PCI Express 2.0, разъем FM1 | ||||

| AMD APU серий C, E и Z ( Bobcat ) | 36-битный | APU интеллектуального устройства с низким энергопотреблением | |||||

| Intel Core i3 , Core i5 и Core i7 ( Сэнди-Бридж / Айви-Бридж ) |

Внутреннее кольцевое соединение, декодированный кэш μ-op, LGA 1155 разъем | ||||||

| 2012 | AMD APU серии A ( Buldozer, Trinity и новее) | 48-битный | AVX , APU на базе Bulldozer, Socket FM2 или Socket FM2+ | ||||

| Intel Xeon Phi ( Рыцарский уголок ) | Сопроцессор дополнительной карты PCI-E для системы на базе XEON, чип Manycore, In-order P54C , очень широкий VPU (512-битный SSE), инструкции LRBni (8 × 64-бит) | ||||||

| 2013 | AMD Ягуар (Атлон, Семпрон) |

SoC , игровая консоль и процессор интеллектуальных устройств с низким энергопотреблением | |||||

| Интел Сильвермонт (Атом, Селерон, Пентиум) |

36-битный | SoC , процессор интеллектуальных устройств с низким или сверхнизким энергопотреблением | |||||

| Intel Core i3 , Core i5 и Core i7 ( Haswell / Broadwell ) | 39-битный | AVX2 , FMA3 , TSX , BMI1 и BMI2 Инструкции LGA 1150 , разъем | |||||

| 2015 | Intel Бродвелл-U ( Intel Core i3 , Core i5 , Core i7 , Core M , Pentium , Celeron ) |

SoC, встроенный Broadwell-U PCH-LP (многочиповый модуль) | |||||

| 2015–2020 | Intel Skylake / Kaby Lake / Cannon Lake / Coffee Lake / Rocket Lake (Intel Pentium/Celeron Gold, Core i3 , Core i5 , Core i7 , Core i9 ) |

46-битный | AVX-512 (только для Cannon Lake-U и вариантов Skylake для рабочих станций/серверов) | ||||

| 2016 | Intel Xeon Phi ( Рыцарский десант ) | 48-битный | Многоядерный процессор и сопроцессор для систем Xeon, ядро на базе Airmont (Atom) | ||||

| 2016 | AMD Бристоль Ридж (AMD (Про) A6/A8/A10/A12) |

Встроенный FCH на кристалле, SoC, разъем AM4 | |||||

| 2017 | Серия AMD Ryzen / AMD Epyc серия | Реализация AMD SMT, нескольких кристаллов на кристалле | |||||

| 2017 | Чжаосинь УДаокоу (KX-5000, KH-20000) | Zhaoxin Первая совершенно новая архитектура x86-64 от | |||||

| 2018–2021 | Intel Sunny Cove ( Ice Lake -U и Y), Cypress Cove ( Rocket Lake ) | 57-битный | Первая реализация AVX-512 от Intel для потребительского сегмента. Добавление инструкций векторной нейронной сети (VNNI) | ||||

| 2019 | AMD Матисс | 48-битный | Конструкция многочипового модуля с кристаллом ввода-вывода, отдельным от кристалла(ов) ЦП, поддержка PCIe Gen4 | ||||

| 2020 | Intel Willow Cove ( Тигровое озеро - Д/Н/Ч) | 57-битный | Архитектура двухкольцевых межсоединений, обновленный Gaussian Neural Accelerator (GNA2), новые инструкции векторного пересечения AVX-512, добавление технологии управления потоком управления (CET). | ||||

| 2021 | Интел Олдер Лейк | Гибридный дизайн с ядрами производительности (Golden Cove) и эффективности (Gracemont), поддержкой PCIe Gen5 и DDR5, обновленным Gaussian Neural Accelerator (GNA3). AVX-512 официально не поддерживается. | |||||

| 2022 | AMD Вермеер (5800X3D) | 48-битный | Чипы X3D имеют дополнительный 3D-кеш L3 с вертикальным расположением объемом 64 МБ (3D V-Cache) для кэша L3 объемом до 96 МБ. | ||||

| 2022 | AMD Рафаэль | Первая реализация AVX-512 от AMD для потребительского сегмента. iGPU теперь входит в стандартную комплектацию процессоров Ryzen с двумя RDNA 2. вычислительными ядрами | |||||

| Эра | Введение | Известные модели процессоров | Адресное пространство | Примечательные особенности | |||

История

[ редактировать ]Дизайнеры и производители

[ редактировать ]

В разное время такие компании, как IBM , VIA , NEC , [ ч ] AMD , TI , STM , Fujitsu , OKI , Siemens , Cyrix , Intersil , C&T , NexGen , UMC и DM&P приступили к разработке или производству [ я ] x86 Процессоры (ЦП), предназначенные для персональных компьютеров и встраиваемых систем. Другие компании, которые разработали или произвели процессоры x86 или x87, включают ITT Corporation , National Semiconductor , ULSI System Technology и Weitek .

Такие реализации x86 редко представляли собой простые копии, но часто использовали разные внутренние микроархитектуры и разные решения на электронном и физическом уровнях. Вполне естественно, что ранние совместимые микропроцессоры были 16-битными, а 32-битные конструкции были разработаны гораздо позже. На рынке персональных компьютеров реальные количества начали появляться примерно в 1990 году с процессорами, совместимыми с i386 и i486 , часто называемыми так же, как оригинальные чипы Intel.

После полностью конвейерного i486 в 1993 году Intel представила торговую марку Pentium (которая, в отличие от цифр, могла быть зарегистрирована как торговая марка ) для своего нового набора суперскалярных процессоров x86. Теперь, когда схема наименования x86 юридически очищена, другим поставщикам x86 пришлось выбирать другие имена для своих x86-совместимых продуктов, и поначалу некоторые предпочитали продолжать использовать вариации схемы нумерации: IBM в партнерстве с Cyrix выпустила 5x86 , а затем и очень эффективную схему нумерации. Линии 6x86 (M1) и 6x86 MX ( MII ) конструкций Cyrix, которые были первыми микропроцессорами x86, реализовавшими переименование регистров для обеспечения возможности спекулятивного выполнения .

Тем временем AMD разработала и выпустила усовершенствованный, но отложенный процессор 5k86 ( K5 AMD 29K RISC ), который внутри был во многом основан на более ранней конструкции ; Подобно NexGen компании Nx586 , он использовал такую стратегию, при которой выделенные этапы конвейера декодировали инструкции x86 в единообразные и легко обрабатываемые микрооперации - метод, который по сей день остается основой для большинства проектов x86.

Некоторые ранние версии этих микропроцессоров имели проблемы с рассеиванием тепла. У 6x86 также было несколько незначительных проблем с совместимостью: у Nx586 отсутствовал блок операций с плавающей запятой (FPU) и (что на тот момент имело решающее значение) совместимость по выводам, в то время как K5 имел несколько разочаровывающую производительность, когда он (в конце концов) был представлен.

Незнание потребителями альтернатив серии Pentium еще больше способствовало тому, что эти разработки оказались сравнительно неудачными, несмотря на то, что K5 имел очень хорошую совместимость с Pentium, а 6x86 был значительно быстрее, чем Pentium в целочисленном коде. [ Дж ] Позже AMD сумела вырасти в серьёзного соперника с набором процессоров K6 , уступившим место очень успешным Athlon и Opteron .

Были и другие претенденты, такие как Centaur Technology (ранее IDT ), Rise Technology и Transmeta . от VIA Technologies Энергоэффективные процессоры C3 и C7 , разработанные компанией Centaur , продавались в течение многих лет после их выпуска в 2005 году. Разработка Centaur 2008 года, VIA Nano , была их первым процессором с суперскалярным и умозрительным исполнением . Он был представлен примерно в то же время (в 2008 году), когда Intel представила Intel Atom , свой первый «нормальный» процессор после P5 Pentium .

За прошедшие годы к исходному набору команд x86 было добавлено множество дополнений и расширений, почти всегда с полной обратной совместимостью . [ к ] Семейство архитектуры реализовано в процессорах Intel, Cyrix , AMD , VIA Technologies и многих других компаний; существуют также открытые реализации, такие как платформа Zet SoC (в настоящее время неактивна). [ 16 ] Тем не менее, из них только Intel, AMD, VIA Technologies и DM&P Electronics имеют лицензии на архитектуру x86, и из них только первые два активно производят современные 64-битные разработки, что приводит к так называемой «дуополии» Intel и AMD в процессорах x86.

Однако в 2014 году китайская компания Zhaoxin со штаб-квартирой в Шанхае , совместное предприятие китайской компании и VIA Technologies, начала разработку процессоров x86 на базе VIA для настольных компьютеров и ноутбуков. Выпуск новейшего семейства «7» [ 17 ] процессоров x86 (например, KX-7000), которые не так быстры, как чипы AMD или Intel, но по-прежнему являются современными, [ 18 ] было запланировано на 2021 год; Однако по состоянию на март 2022 года выпуск не состоялся. [ 19 ]

От 16-битной и 32-битной к 64-битной архитектуре

[ редактировать ]Архитектура набора команд дважды расширялась до большего размера слова . В 1985 году Intel выпустила 32-битный процессор 80386 (позже известный как i386), который постепенно заменил более ранние 16-битные чипы в компьютерах (хотя обычно не во встроенных системах в последующие годы ); эта расширенная модель программирования первоначально называлась архитектурой i386 (как и ее первая реализация), но позже Intel назвала ее IA-32 , представив свою (несвязанную) архитектуру IA-64 .

В 1999–2003 годах AMD называла ее x86-64 расширила эту 32-битную архитектуру до 64 бит и в ранних документах , а позже — AMD64 . Вскоре Intel приняла архитектурные расширения AMD под названием IA-32e, позже использовала имя EM64T и, наконец, использовала Intel 64. Microsoft и Sun Microsystems / Oracle также используют термин «x64», в то время как многие дистрибутивы Linux и BSD также используют термин «amd64». " срок. Microsoft Windows, например, обозначает свои 32-битные версии как «x86», а 64-битные версии — как «x64», а установочные файлы 64-битных версий Windows необходимо помещать в каталог с именем «AMD64». [ 20 ]

В 2023 году Intel предложила серьезное изменение в архитектуре, получившее название x86-S (где S означает «упрощение»), целью которого является прекращение поддержки устаревших режимов выполнения и инструкций. Процессор, реализующий это предложение, начнет выполнение непосредственно в длинном режиме и будет поддерживать только 64-битные операционные системы. 32-битный код будет поддерживаться только для пользовательских приложений, работающих в кольце 3, и будет использовать ту же упрощенную сегментацию, что и длинный режим. [ 21 ] [ 22 ]

Основные свойства архитектуры

[ редактировать ]Архитектура x86 представляет собой инструкцию переменной длины, в первую очередь конструкцию CISC с упором на обратную совместимость . Однако набор команд не является типичным CISC, а представляет собой расширенную версию простых восьмибитных архитектур 8008 и 8080 . Байтовая адресация включена, и слова хранятся в памяти с прямым порядком байтов. Доступ к памяти по невыровненным адресам разрешен почти для всех инструкций. Наибольший собственный размер для целочисленной арифметики и адресов памяти (или смещений ) составляет 16, 32 или 64 бита в зависимости от поколения архитектуры (более новые процессоры также включают прямую поддержку меньших целых чисел). Несколько скалярных значений могут обрабатываться одновременно с помощью модуля SIMD, присутствующего в более поздних поколениях, как описано ниже. [ л ] Смещения немедленной адресации и непосредственные данные могут быть выражены как 8-битные величины для часто встречающихся случаев или контекстов, когда диапазона -128..127 достаточно. Таким образом, типичные инструкции имеют длину 2 или 3 байта (хотя некоторые из них намного длиннее, а некоторые однобайтовые).

Для дополнительной экономии пространства кодирования большинство регистров выражаются в кодах операций с использованием трех или четырех битов, последний - через префикс кода операции в 64-битном режиме, в то время как не более одного операнда инструкции может быть ячейкой памяти. [ м ] Однако этот операнд памяти также может быть пунктом назначения (или комбинированным источником и пунктом назначения), в то время как другой операнд, источник, может быть либо регистровым, либо непосредственным. Помимо прочего, это способствует размеру кода, который конкурирует с восьмибитными машинами, и позволяет эффективно использовать кэш-память инструкций. Относительно небольшое количество регистров общего назначения (также унаследованных от его 8-битных предков) сделало адресацию относительно регистров (с использованием небольших немедленных смещений) важным методом доступа к операндам, особенно в стеке. Поэтому много работы было вложено в то, чтобы сделать такой доступ таким же быстрым, как и доступ к регистру, т. е. обеспечить выполнение инструкций за один цикл в большинстве случаев, когда данные, к которым осуществляется доступ, доступны в кэше верхнего уровня.

Плавающая точка и SIMD

[ редактировать ]Специальный процессор с плавающей запятой с 80-битными внутренними регистрами, 8087 , был разработан для оригинального 8086 . Этот микропроцессор впоследствии превратился в расширенный 80387 , а более поздние процессоры включали обратно совместимую версию этой функциональности на том же микропроцессоре, что и основной процессор. В дополнение к этому современные конструкции x86 также содержат SIMD -модуль (см. SSE ниже), где инструкции могут работать параллельно с (одним или двумя) 128-битными словами, каждое из которых содержит два или четыре числа с плавающей запятой (каждое 64 или 32). битов соответственно) или, альтернативно, 2, 4, 8 или 16 целых чисел (каждое шириной 64, 32, 16 или 8 бит соответственно).

Наличие широких SIMD-регистров означает, что существующие процессоры x86 могут загружать или хранить до 128 бит данных памяти в одной инструкции, а также выполнять побитовые операции (но не целочисленную арифметику). [ н ] ) на полных 128-битных количествах параллельно. В процессоры Intel Sandy Bridge добавлены инструкции Advanced Vector Extensions (AVX), расширяющие регистры SIMD до 256 бит. Начальные многоядерные инструкции Intel, реализованные процессорами Knights Corner Xeon Phi , и инструкции AVX-512, реализованные процессорами Knights Landing Xeon Phi и процессорами Skylake-X , используют 512-битные SIMD-регистры.

Текущие реализации

[ редактировать ]Во время выполнения современные процессоры x86 используют несколько дополнительных шагов декодирования для разделения большинства инструкций на более мелкие части, называемые микрооперациями. Затем они передаются блоку управления , который буферизует и планирует их в соответствии с семантикой x86, чтобы они могли выполняться, частично параллельно, одним из нескольких (более или менее специализированных) исполнительных блоков . Таким образом, эти современные конструкции x86 являются конвейерными , суперскалярными , а также способны к внеочередному и спекулятивному выполнению (посредством предсказания ветвей , переименования регистров и предсказания зависимости от памяти ), что означает, что они могут выполнять несколько (частичных или полных) инструкций x86 одновременно, и не обязательно в том же порядке, как указано в потоке команд. [ 23 ] Некоторые процессоры Intel ( Xeon Foster MP , некоторые Pentium 4 и некоторые Nehalem и более поздние процессоры Intel Core ) и процессоры AMD (начиная с Zen ) также способны к одновременной многопоточности с двумя потоками на ядро ( Xeon Phi имеет четыре потока на ядро). Некоторые процессоры Intel поддерживают транзакционную память ( TSX ).

Когда этот метод был представлен в середине 1990-х годов, его иногда называли «ядром RISC» или «трансляцией RISC», отчасти по маркетинговым причинам, но также потому, что эти микрооперации имеют некоторые общие свойства с определенными типами инструкций RISC. Однако традиционный микрокод (используемый с 1950-х годов) также по своей сути обладает многими из тех же свойств; новый метод отличается главным образом тем, что перевод в микрооперации теперь происходит асинхронно. Отсутствие необходимости синхронизировать исполнительные блоки с этапами декодирования открывает возможности для более глубокого анализа (буферизованного) потока кода и, следовательно, позволяет обнаруживать операции, которые могут выполняться параллельно, одновременно загружая более чем один исполнительный блок.

Новейшие процессоры при необходимости делают и обратное; они объединяют определенные последовательности x86 (например, сравнение с последующим условным переходом) в более сложную микрооперацию, которая лучше соответствует модели выполнения и, следовательно, может выполняться быстрее или с меньшим использованием машинных ресурсов.

Другой способ повысить производительность — кэшировать декодированные микрооперации, чтобы процессор мог напрямую обращаться к декодированным микрооперациям из специального кэша вместо их повторного декодирования. Intel последовала этому подходу, создав функцию Execution Trace Cache в своей микроархитектуре NetBurst (для процессоров Pentium 4), а затем и в буфере декодированного потока (для процессоров под брендом Core, начиная с Sandy Bridge). [ 24 ]

Transmeta использовала совершенно другой метод в своих процессорах, совместимых с Crusoe x86. Они использовали синхронную ЦП трансляцию для преобразования инструкций x86 в собственный набор инструкций VLIW . Transmeta утверждает, что их подход позволяет создавать более энергоэффективные конструкции, поскольку ЦП может отказаться от сложного этапа декодирования, характерного для более традиционных реализаций x86.

Режимы адресации

[ редактировать ]Режимы адресации для режимов 16-битного процессора можно свести к формуле: [ 25 ] [ 26 ]

Режимы адресации для режимов 32-битного процессора x86 [ 27 ] можно свести к формуле: [ 28 ]

Режимы адресации для режима 64-битного процессора можно свести к формуле: [ 28 ]

Относительная адресация инструкций в 64-битном коде (RIP + смещение, где RIP — регистр указателя инструкций ) упрощает реализацию позиционно-независимого кода (который используется в разделяемых библиотеках в некоторых операционных системах). [ 29 ]

8086 имел 64 КБ восьмибитного (или, альтернативно, 32 К-слова из 16-битного ) пространства ввода- вывода и памяти размером 64 КБ (один сегмент), стек поддерживаемый компьютерным оборудованием . В стек можно помещать только слова (два байта). Стек растет в сторону численно меньших адресов, при этом SS:SP указывает на последний отправленный элемент. Имеется 256 прерываний , которые могут быть вызваны как аппаратно, так и программно. Прерывания могут каскадироваться, используя стек для хранения адреса возврата .

регистры x86

[ редактировать ]16-битный

[ редактировать ]Исходные процессоры Intel 8086 и 8088 имели четырнадцать 16- битных регистров. Четыре из них (AX, BX, CX, DX) являются регистрами общего назначения (GPR), хотя каждый из них может иметь дополнительное назначение; например, только CX может использоваться в качестве счетчика с инструкцией цикла. Доступ к каждому из них возможен как к двум отдельным байтам (таким образом, к старшему байту BX можно обращаться как к BH, а к младшему — как к BL). Два регистра указателя имеют особые роли: SP (указатель стека) указывает на «верх» стека , а BP (базовый указатель) часто используется для указания на какое-то другое место в стеке, обычно над локальными переменными (см. указатель кадра). ). Регистры SI, DI, BX и BP являются адресными регистрами и также могут использоваться для индексации массива.

Для формирования адреса памяти используется один из четырех возможных «сегментных регистров» (CS, DS, SS и ES). В исходных 8086/8088/80186/80188 каждый адрес был построен из сегментного регистра и одного из регистров общего назначения. Например, ds:si — это обозначение адреса, сформированное как [16 * ds + si], позволяющее использовать 20-битную адресацию, а не 16-битную, хотя в более поздних процессорах это изменилось. В то время поддерживались только определенные комбинации.

Регистр FLAGS содержит такие флаги , как флаг переноса , флаг переполнения и нулевой флаг . Наконец, указатель инструкции (IP) указывает на следующую инструкцию, которая будет выбрана из памяти и затем выполнена; к этому регистру программа не может получить прямой доступ (чтение или запись). [ 30 ]

Intel 80186 и 80188 по сути являются модернизированными процессорами 8086 или 8088 соответственно с добавленными встроенными периферийными устройствами и имеют те же регистры процессора, что и 8086 и 8088 (в дополнение к регистрам интерфейса для периферийных устройств).

8086, 8088, 80186 и 80188 могут использовать дополнительный сопроцессор с плавающей запятой 8087 . 8087 представляется программисту частью ЦП и добавляет восемь 80-битных регистров, от st(0) до st(7), каждый из которых может хранить числовые данные в одном из семи форматов: 32-, 64- или 80-битное число с плавающей запятой, 16-, 32- или 64-битное (двоичное) целое число и 80-битное упакованное десятичное целое число. [ 9 ] : С-6, С-13..С-15 Он также имеет собственный 16-битный регистр состояния, доступный через fstsw , и обычно некоторые из ее битов просто используют для ветвления, копируя их в обычные FLAGS. [ 31 ]

В Intel 80286 для поддержки защищенного режима три специальных регистра содержат адреса таблицы дескрипторов (GDTR, LDTR, IDTR ), а четвертый регистр задач (TR) используется для переключения задач. 80287 . является сопроцессором с плавающей запятой для 80286 и имеет те же регистры, что и 8087, с теми же форматами данных

32-битный

[ редактировать ]

С появлением 32-битного процессора 80386 16-битные регистры общего назначения, базовые регистры, индексные регистры, указатель команд и регистр FLAGS , но не сегментные регистры, были расширены до 32 бит. В номенклатуре это выражалось добавлением префикса « E » (от «расширенного») к именам регистров на языке ассемблера x86 . Таким образом, регистр AX соответствует младшим 16 битам нового 32-битного регистра EAX, SI соответствует младшим 16 битам ESI и так далее. Регистры общего назначения, базовые регистры и индексные регистры могут использоваться в качестве базовых в режимах адресации, и все эти регистры, за исключением указателя стека, могут использоваться в качестве индекса в режимах адресации.

Были добавлены два новых сегментных регистра (FS и GS). За счет большего количества регистров, инструкций и операндов формат машинного кода был расширен. Для обеспечения обратной совместимости сегменты с исполняемым кодом могут быть помечены как содержащие 16-битные или 32-битные инструкции. Специальные префиксы позволяют включать 32-битные инструкции в 16-битный сегмент и наоборот.

У 80386 был дополнительный сопроцессор с плавающей запятой, 80387 ; у него было восемь 80-битных регистров: от st(0) до st(7), [ 32 ] как 8087 и 80287. 80386 также может использовать сопроцессор 80287. [ 33 ] В 80486 и всех последующих моделях x86 процессор с плавающей запятой (FPU) встроен в кристалл.

В Pentium MMX добавлены восемь 64-битных целочисленных векторных регистров MMX (от MM0 до MM7, которые используют младшие биты совместно со стеком FPU шириной 80 бит). [ 34 ] В Pentium III Intel добавила 32-битный регистр управления/состояния Streaming SIMD Extensions (SSE) (MXCSR) и восемь 128-битных регистров SSE с плавающей запятой (от XMM0 до XMM7). [ 35 ]

64-битная

[ редактировать ]Начиная с процессора AMD Opteron , архитектура x86 расширила 32-битные регистры до 64-битных, аналогично тому, как происходило расширение с 16 до 32-битных. Префикс R (от слова «регистр») идентифицирует 64-битные регистры (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP) и восемь дополнительных 64-битных регистров общего назначения (R8–R15). ) также были введены при создании x86-64 . Также были добавлены еще восемь векторных регистров SSE (XMM8–XMM15). Однако эти расширения можно использовать только в 64-битном режиме, который является одним из двух режимов, доступных только в длинном режиме . Режимы адресации существенно не изменились по сравнению с 32-битным режимом, за исключением того, что адресация была расширена до 64 бит, знак виртуальных адресов теперь расширен до 64 бит (чтобы запретить биты режима в виртуальных адресах), а другие детали селектора были значительно уменьшены. . Кроме того, был добавлен режим адресации, позволяющий обращаться к памяти относительно RIP ( указатель инструкции ), чтобы упростить реализацию позиционно-независимого кода. , используемый в общих библиотеках в некоторых операционных системах.

128-битный

[ редактировать ]Регистры SIMD XMM0–XMM15 (XMM0–XMM31, если AVX-512 поддерживается ).

256-битный

[ редактировать ]SIMD регистрирует YMM0–YMM15 (YMM0–YMM31, если AVX-512 поддерживается ). Нижняя половина каждого регистра YMM отображается в соответствующий регистр XMM.

512-битный

[ редактировать ]SIMD-регистры ZMM0–ZMM31. Нижняя половина каждого регистра ZMM отображается в соответствующий регистр YMM.

Разное/специального назначения

[ редактировать ]Процессоры x86, имеющие защищенный режим , то есть процессоры 80286 и более поздних версий, также имеют три регистра дескриптора (GDTR, LDTR, IDTR ) и регистр задач (TR).

32-разрядные процессоры x86 (начиная с 80386) также включают в себя различные специальные/разные регистры, такие как регистры управления (от CR0 до 4, CR8 только для 64-разрядных версий), регистры отладки (от DR0 до 3, плюс 6 и 7), тестовые регистры. (TR3–7; только 80486) и регистры конкретной модели (MSR, появляющиеся в составе Pentium). [ о ] ).

AVX-512 имеет восемь дополнительных 64-битных регистров маски K0–K7 для выбора элементов в векторном регистре. В зависимости от векторного регистра и ширины элемента, данной инструкцией может использоваться только подмножество битов регистра маски.

Цель

[ редактировать ]Хотя основные регистры (за исключением указателя команд) являются «общими» в 32-битной и 64-битной версиях набора команд и могут использоваться для чего угодно, изначально предполагалось, что они будут использоваться для следующие цели:

- AL/AH/AX/EAX/RAX: аккумулятор

- CL/CH/CX/ECX/RCX: счетчик (для использования с циклами и строками)

- DL/DH/DX/EDX/RDX: Расширьте точность аккумулятора (например, объедините 32-битные EAX и EDX для 64-битных целочисленных операций в 32-битном коде).

- BL/BH/BX/EBX/RBX: базовый индекс (для использования с массивами)

- SP/ESP/RSP: указатель стека для верхнего адреса стека.

- BP/EBP/RBP: базовый указатель стека для хранения адреса текущего кадра стека .

- SI/ESI/RSI: исходный индекс для строковых операций.

- DI/EDI/RDI: индекс назначения для строковых операций.

- IP/EIP/RIP: указатель инструкции. Содержит счетчик программ , адрес следующей инструкции.

Сегментные регистры:

- CS: Код

- ДС: Данные

- СС: Стек

- RU: Дополнительные данные

- ФС: Дополнительные данные №2

- GS: Дополнительные данные №3.

Для остальных 8 регистров, доступных только в 64-битном режиме, особых целей не предусматривалось.

Некоторые инструкции компилируются и выполняются более эффективно при использовании этих регистров по назначению. Например, использование AL в качестве аккумулятора и добавление к нему непосредственного значения байта дает эффективное добавление к коду операции AL 04h, в то время как использование регистра BL создает общий и более длинный код операции добавления к регистру 80C3h. Другой пример — деление и умножение двойной точности, которое работает специально с регистрами AX и DX.

Современные компиляторы выиграли от введения sib -байта ( байт масштаба-индекса-базы ), который позволяет единообразно обрабатывать регистры ( подобно миникомпьютеру ). Однако универсальное использование сиббайта неоптимально, поскольку оно обеспечивает более длинные кодировки, чем его выборочное использование при необходимости. (Основным преимуществом сиббайта является ортогональность и более мощные режимы адресации, которые он обеспечивает, что позволяет сохранять инструкции и использовать регистры для вычислений адреса, таких как масштабирование индекса.) Некоторые специальные инструкции потеряли приоритет в аппаратной конструкции. и стал медленнее, чем эквивалентные небольшие кодовые последовательности. Ярким примером является инструкция LODSW.

Структура

[ редактировать ]| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R?X | |||||||

| БЫВШИЙ | |||||||

| ?X | |||||||

| ?ЧАС | ?Л | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| ?Д | |||||||

| ?В | |||||||

| ?Б | |||||||

| 16 | 8 |

|---|---|

| ?С | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| Р?П | |||||||

| Э?П | |||||||

| ?П | |||||||

| ?PL | |||||||

Примечание. Регистры ?PL доступны только в 64-битном режиме.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| Р?И | |||||||

| Э?Я | |||||||

| ?Я | |||||||

| ?ТОТ | |||||||

Примечание. Регистры ?IL доступны только в 64-битном режиме.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| РВАТЬ | |||||||

| ЭИП | |||||||

| ИП | |||||||

Режимы работы

[ редактировать ]Реальный режим

[ редактировать ]Этот раздел нуждается в дополнительных цитатах для проверки . ( январь 2014 г. ) |

Режим реального адреса, [ 36 ] Обычно называемый реальным режимом, это режим работы 8086 и более поздних версий x86-совместимых процессоров . Реальный режим характеризуется 20-битным сегментированным адресным пространством памяти (это означает, что можно адресовать лишь немногим более 1 МБ памяти). [ п ] ), прямой доступ программного обеспечения к периферийному оборудованию и отсутствие концепции защиты памяти или многозадачности на аппаратном уровне. Все процессоры x86 серии 80286 и новее запускаются в реальном режиме при включении питания; Процессоры 80186 и более ранние версии имели только один рабочий режим, который эквивалентен реальному режиму в более поздних чипах. (На платформе IBM PC прямой программный доступ к процедурам IBM BIOS доступен только в реальном режиме, поскольку BIOS написан для реального режима. Однако это свойство не процессора x86, а конструкции IBM BIOS.)

Чтобы использовать более 64 КБ памяти, необходимо использовать сегментные регистры. Это создало большие сложности для разработчиков компиляторов, которые ввели нечетные режимы указателей, такие как «ближний», «далекий» и «огромный», чтобы в разной степени использовать неявную природу сегментированной архитектуры, при этом некоторые указатели содержали 16-битные смещения внутри подразумеваемых сегментов и другие. указатели, содержащие адреса сегментов и смещения внутри сегментов. Технически возможно использовать до 256 КБ памяти для кода и данных и до 64 КБ для кода, установив все четыре сегментных регистра один раз, а затем используя только 16-битные смещения (опционально с префиксами переопределения сегментов по умолчанию) для адресовать память, но это накладывает существенные ограничения на способы адресации данных и объединения операндов памяти, а также нарушает архитектурный замысел разработчиков Intel, который заключается в том, чтобы отдельные элементы данных (например, массивы, структуры, кодовые единицы) содержащиеся в отдельных сегментах и адресуемые по собственным сегментным адресам, в новых программах, не портированных с более ранних 8-битных процессоров с 16-битными адресными пространствами.

Нереальный режим

[ редактировать ]Режим Unreal используется некоторыми 16-битными операционными системами и некоторыми 32-битными загрузчиками .

Режим управления системой

[ редактировать ]Режим управления системой (SMM) используется только системной прошивкой ( BIOS / UEFI ), а не операционными системами и прикладным программным обеспечением. Код SMM выполняется в SMRAM.

Защищенный режим

[ редактировать ]Этот раздел нуждается в дополнительных цитатах для проверки . ( январь 2014 г. ) |

В дополнение к реальному режиму процессор Intel 80286 поддерживает защищенный режим, расширяя адресную физическую память до 16 МБ и адресуемую виртуальную память до 1 ГБ , а также обеспечивая защищенную память , которая предотвращает повреждение программ друг друга. Это делается с помощью сегментных регистров только для хранения индекса в таблице дескрипторов, хранящейся в памяти. Существует две такие таблицы: глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT), каждая из которых содержит до 8192 дескрипторов сегментов, причем каждый сегмент предоставляет доступ к 64 КБ памяти. В 80286 дескриптор сегмента предоставляет 24-битный базовый адрес , и этот базовый адрес добавляется к 16-битному смещению для создания абсолютного адреса. Базовый адрес из таблицы выполняет ту же роль, которую буквальное значение сегментного регистра выполняет в реальном режиме; регистры сегментов были преобразованы из прямых регистров в косвенные регистры. Каждому сегменту может быть назначен один из четырех уровней кольца , используемых для аппаратной компьютерной безопасности. . Каждый дескриптор сегмента также содержит поле ограничения сегмента, которое определяет максимальное смещение, которое может использоваться с сегментом. Поскольку смещения составляют 16 бит, сегменты по-прежнему ограничены 64 КБ каждый в защищенном режиме 80286. [ 37 ]

Каждый раз, когда регистр сегмента загружается в защищенном режиме, 80286 должен прочитать 6-байтовый дескриптор сегмента из памяти в набор скрытых внутренних регистров. Таким образом, загрузка регистров сегментов в защищенном режиме происходит намного медленнее, чем в реальном режиме, и следует избегать очень частого изменения сегментов. Фактические операции с памятью с использованием сегментов защищенного режима не сильно замедляются, поскольку 80286 и более поздние версии имеют аппаратное обеспечение для проверки смещения относительно ограничения сегмента параллельно с выполнением инструкций.

Intel 80386 расширил смещения, а также поле ограничения сегмента в каждом дескрипторе сегмента до 32 бит, что позволяет сегменту охватывать все пространство памяти. Также введена поддержка подкачки в защищенном режиме — механизма, позволяющего использовать выгружаемую виртуальную память (с размером страницы 4 КБ). Пейджинг позволяет ЦП сопоставить любую страницу пространства виртуальной памяти с любой страницей пространства физической памяти. Для этого он использует дополнительные таблицы отображения в памяти, называемые таблицами страниц. Защищенный режим на 80386 может работать как с включенным, так и с отключенным пейджингом; механизм сегментации всегда активен и генерирует виртуальные адреса, которые затем сопоставляются механизмом подкачки, если он включен. Механизм сегментации также можно эффективно отключить, установив для всех сегментов базовый адрес 0 и ограничение размера, равное всему адресному пространству; для этого также требуется таблица дескрипторов сегментов минимального размера, состоящая всего из четырех дескрипторов (поскольку сегменты FS и GS использовать не обязательно). [ q ]

Пейджинг широко используется в современных многозадачных операционных системах. Linux , 386BSD и Windows NT были разработаны для 386, поскольку это был первый процессор на архитектуре Intel, поддерживающий подкачку и 32-битное смещение сегментов. Архитектура 386 стала основой всех дальнейших разработок серии x86.

Процессоры x86, поддерживающие защищенный режим, загружаются в реальный режим для обеспечения обратной совместимости с процессорами более старого класса 8086. При включении питания (так называемой загрузке ) процессор инициализируется в реальном режиме, а затем начинает выполнять инструкции. Загрузочный код операционной системы, который может храниться в постоянной памяти , может перевести процессор в защищенный режим для включения подкачки и других функций. И наоборот, сегментная арифметика, обычная практика в коде реального режима, не допускается в защищенном режиме.

Виртуальный режим 8086

[ редактировать ]Также существует подрежим работы в 32-битном защищенном режиме (он же защищенный режим 80386), называемый виртуальным режимом 8086 , также известный как режим V86 . По сути, это специальный гибридный режим работы, который позволяет программам и операционным системам реального режима работать под контролем операционной системы супервизора защищенного режима. Это обеспечивает большую гибкость при одновременном запуске программ как в защищенном, так и в реальном режиме. Этот режим доступен исключительно для 32-битной версии защищенного режима; его не существует ни в 16-битной версии защищенного режима, ни в длинном режиме.

Длинный режим

[ редактировать ]В середине 1990-х годов было очевидно, что 32-битное адресное пространство архитектуры x86 ограничивает ее производительность в приложениях, требующих больших наборов данных. 32-битное адресное пространство позволит процессору напрямую обращаться только к 4 ГБ данных, что превосходит размер таких приложений, как обработка видео и механизмы баз данных . Используя 64-битные адреса, можно напрямую адресовать 16 EiB данных, хотя большинство 64-битных архитектур не поддерживают доступ ко всему 64-битному адресному пространству; например, AMD64 поддерживает только 48 бит из 64-битного адреса, разделенных на четыре уровня подкачки.

В 1999 году AMD опубликовала (почти) полную спецификацию 64-битного расширения архитектуры x86, которое они назвали x86-64 и заявили о намерении производить. В настоящее время такая конструкция используется почти во всех процессорах x86, за некоторыми исключениями, предназначенными для встраиваемых систем .

массового производства Чипы x86-64 для общего рынка стали доступны четыре года спустя, в 2003 году, после того, как было потрачено время на тестирование и доработку рабочих прототипов; примерно в то же время первоначальное название x86-64 было изменено на AMD64 . Успех линейки процессоров AMD64 в сочетании с вялым приемом архитектуры IA-64 вынудил Intel выпустить собственную реализацию набора инструкций AMD64. Ранее Intel реализовала поддержку AMD64. [ 38 ] но решил не включать его в надежде, что AMD не выведет AMD64 на рынок до того, как новый набор инструкций Itanium IA-64 получит широкое распространение. Она обозначила свою реализацию AMD64 как EM64T , а позже переименовала ее в Intel 64 .

В своей документации и названиях версий продуктов Microsoft и Sun вместе называют AMD64/Intel 64 x64 в операционных системах Windows и Solaris . В дистрибутивах Linux он называется «x86-64», его вариант «x86_64» или «amd64». В системах BSD используется «amd64», а в macOS — «x86_64».

Длинный режим в основном является расширением 32-битного набора команд, но в отличие от перехода с 16 на 32-бит, многие инструкции были удалены в 64-битном режиме. Это не влияет на фактическую обратную двоичную совместимость (которая будет выполнять устаревший код в других режимах, сохраняющих поддержку этих инструкций), но меняет способ работы ассемблера и компиляторов для нового кода.

Это был первый случай, когда крупное расширение архитектуры x86 было инициировано и создано другим производителем, а не Intel. Кроме того, это был первый случай, когда Intel приняла технологию такого рода из внешнего источника.

Расширения

[ редактировать ]Модуль с плавающей запятой

[ редактировать ]Ранние процессоры x86 могли быть расширены аппаратным обеспечением для операций с плавающей запятой в виде серии числовых сопроцессоров с плавающей запятой с такими именами, как 8087 , 80287 и 80387, сокращенно x87. Это также было известно как NPX ( Numeric Processor eXtension ), подходящее название, поскольку сопроцессоры, хотя и использовались в основном для вычислений с плавающей запятой, также выполняли целочисленные операции как в двоичном, так и в десятичном форматах. За очень немногими исключениями, процессоры 80486 и последующие процессоры x86 затем интегрировали эту функциональность x87 в кристалл, что сделало инструкции x87 де-факто неотъемлемой частью набора инструкций x86.

Каждый регистр x87, известный как ST(0)–ST(7), имеет ширину 80 бит и хранит числа в с плавающей запятой IEEE стандартном формате двойной точности . Эти регистры организованы в виде стека со ST(0) наверху. Это было сделано для экономии пространства кода операции, и поэтому регистры доступны в произвольном порядке только для любого операнда в инструкции «регистр-регистр»; ST0 всегда должен быть одним из двух операндов: источником или пунктом назначения, независимо от того, является ли другой операнд ST(x) или операндом памяти. Однако произвольный доступ к регистрам стека можно получить с помощью команды, которая заменяет любой указанный ST(x) на ST(0).

Операции включают в себя арифметические и трансцендентные функции, включая тригонометрические и экспоненциальные функции, а также инструкции, которые загружают общие константы (такие как 0; 1; e, основание натурального логарифма; log2(10); и log10(2)) в одну из стек регистрируется. Хотя возможности целых чисел часто упускаются из виду, процессор x87 может работать с большими целыми числами с помощью одной инструкции, чем процессор 8086, 80286, 80386 или любой процессор x86 без 64-битных расширений, а также повторять целочисленные вычисления даже с небольшими значениями (например, 16-бит) можно ускорить, выполняя целочисленные инструкции на процессорах x86 и x87 параллельно. (ЦП x86 продолжает работать, пока сопроцессор x87 выполняет вычисления, а x87 подает сигнал x86, когда он завершается, или прерывает x86, если ему требуется внимание из-за ошибки.)

ММХ

[ редактировать ]MMX — это набор команд SIMD , разработанный Intel и представленный в 1997 году для микропроцессора Pentium MMX . [ 39 ] Набор инструкций MMX был разработан на основе аналогичной концепции, впервые использованной в Intel i860 . Он поддерживается на большинстве последующих процессоров IA-32 от Intel и других производителей. MMX обычно используется для обработки видео (например, в мультимедийных приложениях). [ 40 ]

MMX добавил в архитектуру 8 новых регистров, известных как от MM0 до MM7 (далее именуемых MMn ). На самом деле эти новые регистры были просто псевдонимами существующих регистров стека x87 FPU. Следовательно, все, что было сделано со стеком с плавающей запятой, также повлияет на регистры MMX. В отличие от стека FP, эти регистры MMn были фиксированными, а не относительными, и поэтому к ним был произвольный доступ. Набор команд не принял семантику, подобную стеку, чтобы существующие операционные системы могли правильно сохранять и восстанавливать состояние регистра при многозадачности без изменений. [ 39 ]

Каждый из регистров MMn представляет собой 64-битное целое число. Однако одной из основных концепций набора команд MMX является концепция упакованных типов данных , что означает, что вместо использования всего регистра для одного 64-битного целого числа ( четверенного слова ) его можно использовать для хранения двух 32-битных целых чисел. ( двойное слово ), четыре 16-битных целых числа ( слово ) или восемь 8-битных целых чисел ( байт ). Учитывая, что 64-битные регистры MMn MMX связаны со стеком FPU и каждый из регистров с плавающей запятой имеет ширину 80 бит, старшие 16 бит регистров с плавающей запятой не используются в MMX. Все эти биты устанавливаются во все единицы любой инструкцией MMX, что соответствует представлению NaN или бесконечностей с плавающей запятой. [ 39 ]

3DСейчас!

[ редактировать ]В 1997 году AMD представила 3DNow!. [ 41 ] Внедрение этой технологии совпало с ростом популярности 3D- ЦП развлекательных приложений и было разработано для повышения производительности векторной обработки в приложениях с интенсивным использованием графики. Разработчики 3D-видеоигр и поставщики оборудования для 3D-графики используют 3DNow! AMD серий K6 и Athlon . для повышения их производительности на процессорах [ 42 ]

3DСейчас! был разработан как естественная эволюция MMX от целых чисел к числам с плавающей запятой. Таким образом, он использует точно такое же соглашение об именах регистров, что и MMX, то есть от MM0 до MM7. [ 43 ] Единственное отличие состоит в том, что вместо упаковки целых чисел в эти регистры одинарной точности с плавающей запятой в каждый регистр упаковываются два числа . Преимущество псевдонимов регистров FPU заключается в том, что те же структуры инструкций и данных, которые используются для сохранения состояния регистров FPU, также можно использовать для сохранения 3DNow! регистрировать состояния. Таким образом, не требуется вносить никаких специальных модификаций в операционные системы, которые в противном случае не знали бы о них. [ 44 ]

SSE и AVX

[ редактировать ]Streaming SIMD Extensions (SSE) В 1999 году Intel представила набор инструкций , а в 2000 году — SSE2. Первое дополнение позволило выгрузить базовые операции с плавающей запятой из стека x87, а второе сделало MMX практически устаревшим и позволило реалистично использовать инструкции обычными компиляторами. Представленный в 2004 году вместе с Prescott версией процессора Pentium 4 , SSE3 добавил специальные инструкции по управлению памятью и потоками для повышения производительности технологии Intel HyperThreading . AMD лицензировала набор инструкций SSE3 и реализовала большую часть инструкций SSE3 для своих процессоров Athlon 64 версии E и более поздних версий. Athlon 64 не поддерживает HyperThreading и в нем отсутствуют инструкции SSE3, используемые только для HyperThreading. [ 45 ]

SSE отбросил все устаревшие соединения со стеком FPU. Это также означало, что этот набор инструкций отбрасывал все устаревшие соединения с предыдущими поколениями наборов команд SIMD, такими как MMX. Но это освободило разработчиков, позволив им использовать регистры большего размера, не ограничиваясь размером регистров FPU. Разработчики создали восемь 128-битных регистров, получивших названия от XMM0 до XMM7. (В AMD64 количество регистров SSE XMM было увеличено с 8 до 16.) Однако недостатком было то, что операционные системы должны были знать об этом новом наборе инструкций, чтобы иметь возможность сохранять состояния своих регистров. Поэтому Intel создала слегка измененную версию защищенного режима, называемую расширенным режимом, которая позволяет использовать инструкции SSE, тогда как в обычном защищенном режиме они остаются отключенными. ОС, которая знает о SSE, активирует расширенный режим, тогда как ОС, не знающая об этом, перейдет только в традиционный защищенный режим.

SSE — это набор инструкций SIMD, который работает только со значениями с плавающей запятой, например 3DNow!. Однако, в отличие от 3DNow! он разрывает все устаревшие соединения со стеком FPU. вдвое больше чисел с плавающей запятой одинарной точности Поскольку у него больше регистров, чем у 3DNow!, SSE может упаковать в свои регистры . Первоначальный SSE был ограничен только числами с одинарной точностью, как 3DNow!. В SSE2 также появилась возможность упаковывать числа двойной точности , что 3DNow! не имел возможности сделать это, поскольку число двойной точности имеет размер 64 бита, что соответствует полному размеру одного 3DNow! ММн регистр. При длине 128 бит регистры SSE XMMn могут упаковывать два числа двойной точности в один регистр. Таким образом, SSE2 гораздо более подходит для научных вычислений, чем SSE1 или 3DNow!, которые были ограничены только одинарной точностью. SSE3 не вводит никаких дополнительных регистров. [ 45 ]

Расширенные векторные расширения (AVX) увеличили размер регистров SSE вдвое до 256-битных регистров YMM. Он также представил схему кодирования VEX для размещения регистров большего размера, а также несколько инструкций для перестановки элементов. В AVX2 не было дополнительных регистров, но он отличался добавлением инструкций маскировки, сбора и перемешивания.

AVX-512 имеет еще одно расширение до 32 512-битных регистров ZMM и новую схему EVEX. В отличие от своих предшественников с монолитным расширением, он разделен на множество подмножеств, которые могут быть реализованы конкретными моделями процессоров.

Расширение физического адреса (PAE)

[ редактировать ]Расширение физического адреса или PAE было впервые добавлено в процессоры Intel Pentium Pro , а позже AMD в процессоры Athlon. [ 46 ] чтобы разрешить адресацию до 64 ГБ ОЗУ. Без PAE объем физической оперативной памяти в 32-битном защищенном режиме обычно ограничен 4 ГБ . PAE определяет другую структуру таблицы страниц с более широкими записями таблицы страниц и третьим уровнем таблицы страниц, что позволяет использовать дополнительные биты физического адреса. Хотя первоначальные реализации на 32-битных процессорах теоретически поддерживали до 64 ГБ ОЗУ, ограничения набора микросхем и других платформ часто ограничивали возможности фактического использования. Процессоры x86-64 определяют структуры таблицы страниц, которые теоретически допускают до 52 бит физического адреса, хотя, опять же, набор микросхем и другие проблемы платформы (например, количество доступных слотов DIMM и максимально возможный объем оперативной памяти на каждый модуль DIMM) не позволяют использовать такой большой физический адрес. пространство для реализации. На процессорах x86-64 режим PAE должен быть активен до переключения в длинный режим и должен оставаться активным, пока активен длинный режим , поэтому в длинном режиме не существует режима «не-PAE». Режим PAE не влияет на ширину линейных или виртуальных адресов.

х86-64

[ редактировать ]Этот раздел нуждается в дополнительных цитатах для проверки . ( Март 2016 г. ) |

К 2000-м годам ограничения 32-битных процессоров x86 в адресации памяти стали препятствием для их использования в высокопроизводительных вычислительных кластерах и мощных настольных рабочих станциях. Устаревшая 32-битная архитектура x86 конкурировала с гораздо более совершенными 64-битными RISC-архитектурами, которые могли адресовать гораздо больше памяти. Intel и всей экосистеме x86 требовалась 64-битная адресация памяти, чтобы x86 смогла пережить эпоху 64-битных вычислений, поскольку вскоре приложения для рабочих станций и настольных компьютеров начали выходить за пределы 32-битной адресации памяти. Однако Intel посчитала, что пришло время сделать смелый шаг и использовать переход на 64-битные настольные компьютеры для перехода от архитектуры x86 в целом, но этот эксперимент в конечном итоге провалился.

В 2001 году Intel попыталась внедрить 64-битную архитектуру, отличную от x86, под названием IA-64 в своем процессоре Itanium , первоначально нацеленную на рынок высокопроизводительных вычислений , надеясь, что она в конечном итоге заменит 32-битную x86. [ 47 ] Хотя IA-64 был несовместим с x86, процессор Itanium обеспечивал возможности эмуляции для трансляции инструкций x86 в IA-64, но это настолько сильно влияло на производительность программ x86, что редко, если вообще когда-либо, это было действительно полезно для пользователей: программисты следует переписать программы x86 для архитектуры IA-64, иначе их производительность на Itanium будет на порядки хуже, чем на настоящем процессоре x86. Рынок отверг процессор Itanium, поскольку он нарушал обратную совместимость и предпочитал продолжать использовать чипы x86, а для IA-64 было переписано очень мало программ.

AMD решила пойти другим путем в сторону 64-битной адресации памяти, чтобы не пострадать обратная совместимость. В апреле 2003 года AMD выпустила первый процессор x86 с 64-битными регистрами общего назначения Opteron , способный адресовать гораздо больше, чем 4 ГБ виртуальной памяти, используя новое расширение x86-64 (также известное как AMD64 или x64). 64-битные расширения архитектуры x86 были включены только в недавно представленном длинном режиме , поэтому 32-битные и 16-битные приложения и операционные системы могли просто продолжать использовать процессор AMD64 в защищенном или других режимах, даже без малейшего ущерба для производительность [ 48 ] и с полной совместимостью с исходными инструкциями 16-битного Intel 8086. [ 49 ] : 13–14 Рынок отреагировал положительно, приняв 64-битные процессоры AMD как для высокопроизводительных приложений, так и для деловых и домашних компьютеров.

Видя, что рынок отвергает несовместимый процессор Itanium, а Microsoft поддерживает AMD64, Intel была вынуждена отреагировать и в июле 2004 года представила свой собственный процессор x86-64 Prescott Pentium 4. [ 50 ] В результате процессор Itanium с набором инструкций IA-64 используется редко, а x86 в своей версии x86-64 по-прежнему является доминирующей архитектурой ЦП в невстраиваемых компьютерах.

В x86-64 также появился бит NX , который обеспечивает некоторую защиту от ошибок безопасности, вызванных переполнением буфера .

В результате вклада AMD в развитие архитектуры x86 и ее последующего принятия Intel, 64-битные RISC-архитектуры перестали быть угрозой для экосистемы x86 и практически исчезли с рынка рабочих станций. x86-64 начали использоваться в мощных суперкомпьютерах (в их воплощениях AMD Opteron и Intel Xeon ), рынке, который ранее был естественной средой обитания для 64-битных RISC-проектов (таких как микропроцессоры IBM Power или процессоры SPARC ). Большой скачок к 64-битным вычислениям и поддержание обратной совместимости с 32-битным и 16-битным программным обеспечением позволили архитектуре x86 стать сегодня чрезвычайно гибкой платформой, при этом чипы x86 используются в небольших системах с низким энергопотреблением (например, Intel Quark и Intel Atom ) до быстрых игровых настольных компьютеров (например, Intel Core i7 и AMD FX / Ryzen ) и даже доминировать в крупных суперкомпьютерных кластерах , фактически оставляя ARM в качестве конкурента только 32-битную и 64-битную RISC-архитектуру . смартфон и планшет рынок.

Виртуализация

[ редактировать ]До 2005 года процессоры с архитектурой x86 не могли соответствовать требованиям Попека и Голдберга — спецификации виртуализации, созданной в 1974 году Джеральдом Дж. Попеком и Робертом П. Голдбергом . Однако как проприетарные, так и продукты гипервизора виртуализации x86 с открытым исходным кодом были разработаны с использованием программной виртуализации . Собственные системы включают Hyper-V , Parallels Workstation , VMware ESX , VMware Workstation , VMware Workstation Player и Windows Virtual PC , а бесплатные системы и системы с открытым исходным кодом включают QEMU , виртуальную машину на основе ядра , VirtualBox и Xen .

Внедрение наборов инструкций AMD-V и Intel VT-x в 2005 году позволило процессорам x86 соответствовать требованиям виртуализации Попека и Голдберга. [ 51 ]

АЕС

[ редактировать ]APX (расширения повышенной производительности)

[ редактировать ]APX (расширения расширенной производительности) — это расширения, позволяющие удвоить количество регистров общего назначения с 16 до 32 и добавить новые функции для повышения производительности общего назначения. [ 52 ] [ 53 ] [ 54 ] [ 55 ] Эти расширения были названы «поколенческими». [ 56 ] и «самое большое дополнение к x86 со времен 64-битных версий». [ 57 ] Intel внесла поддержку APX в коллекцию компиляторов GNU (GCC) 14. [ 58 ]

Согласно спецификации архитектуры, [ 59 ] Основные особенности APX:

- 16 дополнительных регистров общего назначения, называемых расширенными GPR (EGPR).

- Форматы инструкций с тремя операндами для многих целочисленных инструкций

- Новые условные инструкции для загрузки, сохранения и сравнения с обычными инструкциями, которые не изменяют флаги.

- Оптимизированы операции сохранения/восстановления регистра.

- 64-битная инструкция абсолютного прямого перехода.

Расширенные GPR для инструкций общего назначения кодируются с использованием 2-байтового префикса REX2 , а новые инструкции и расширенные операнды для существующих инструкций AVX / AVX2 / AVX-512 кодируются с помощью расширенного префикса EVEX , который имеет четыре варианта, используемые для разных групп инструкций.

См. также

[ редактировать ]- язык ассемблера x86

- списки инструкций x86

- сегментация памяти x86

- идентификатор процессора

- Итаний

- х86-64

- 680x0 , конкурирующая архитектура 16-битной и ранней 32-битной эпох.

- PowerPC , конкурирующая архитектура более поздних 32-битных и 64-битных эпох.

- Микроархитектура

- Список процессоров AMD

- Список процессоров Intel

- Список микроархитектур процессоров Intel

- Список ядер микропроцессора VIA

- Список производителей x86

- Запрос прерывания

- iAPX

- Уязвимость процессора при временном выполнении

- Модель тик-так

- Виртуальные устаревшие провода

Примечания

[ редактировать ]- ^ В отличие от микроархитектуры (и конкретной электронной и физической реализации), используемой для конкретной конструкции микропроцессора.

- ^ GRID Compass . Например, ноутбук

- ^ Включая процессоры 8088 , 80186 , 80188 и 80286 .

- ^ Такая система также содержала обычное сочетание стандартных вспомогательных компонентов серии 7400 , включая мультиплексоры , буферы и связующую логику .

- ^ Фактическое значение iAPX было Intel Advanced Performance Architecture или иногда Intel Advanced Processor Architecture .

- ^ конец 1981 - начало 1984 года, примерно

- ^ Рынок встраиваемых процессоров представлен более чем 25 различными архитектурами , которые из-за чувствительности к цене, низкого энергопотребления и требований к простоте оборудования превосходят по численности x86.

- ^ NEC V20 и V30 также предоставили более старый набор команд 8080, позволяющий ПК, оснащенным этими микропроцессорами, работать с приложениями CP/M на полной скорости (т. е. без необходимости моделирования 8080 с помощью программного обеспечения).

- ^ Компании Fables разработали чип и заключили контракт с другой компанией на его производство, в то время как компании Fabbed сами занимались как разработкой, так и производством. Некоторые компании начинали как производители-фабриканты, а затем стали разработчиками без фабрик, одним из таких примеров является AMD.

- ^ Однако у него был более медленный FPU, что немного иронично, поскольку Cyrix начинала как разработчик быстрых модулей с плавающей запятой для процессоров x86.

- ^ Intel отказалась от схемы именования «x86» для P5 Pentium в 1993 году (поскольку номера не могли быть зарегистрированы как товарные знаки). Тем не менее, термин x86 уже был принят среди технических специалистов, авторов компиляторов и т. д.

- ^ 16-битные и 32-битные микропроцессоры были представлены в 1978 и 1985 годах соответственно; о планах на 64-битную версию было объявлено в 1999 году и постепенно внедрялось с 2003 года и далее.

- ^ В некоторых конструкциях CISC, таких как PDP-11 , может использоваться два.

- ^ Это связано с тем, что целочисленная арифметика генерирует перенос между последующими битами (в отличие от простых побитовых операций).

- ^ Особый интерес представляют два MSR: SYSENTER_EIP_MSR и SYSENTER_ESP_MSR, представленные в процессоре Pentium® II, которые хранят адрес обработчика системных служб режима ядра и соответствующий указатель стека ядра. Инициализируемые во время запуска системы, SYSENTER_EIP_MSR и SYSENTER_ESP_MSR используются инструкциями SYSENTER (Intel) или SYSCALL (AMD) для выполнения быстрых системных вызовов, что примерно в три раза быстрее, чем метод программного прерывания, использовавшийся ранее.

- ^ Поскольку сегментированный адрес представляет собой сумму 16-битного сегмента, умноженного на 16, и 16-битного смещения, максимальный адрес составляет 1 114 095 (шестнадцатеричный 10FFEF), для адресуемости 1 114 096 байт = 1 МБ + 65 520 байт. До 80286 процессоры x86 имели только 20 физических адресных строк (сигналы адресных битов), поэтому 21-й бит адреса, бит 20, был отброшен, а адреса после 1 МБ были зеркалами нижнего конца адресного пространства (начиная с адреса ноль). Начиная с 80286, все процессоры x86 имеют как минимум 24 физических адресных строки, а бит 20 вычисленного адреса выводится на адресную шину в реальном режиме, что позволяет процессору адресовать полные 1 114 096 байт, достижимые с помощью сегментированного адреса x86. На популярной платформе IBM PC к машинам с процессором 80286 или новее было добавлено переключаемое оборудование для отключения 21-го бита адреса, чтобы все программы, разработанные для моделей на базе 8088/8086, могли работать, в то время как более новое программное обеспечение могло использовать преимущества «высокого» уровня. память в реальном режиме и полное адресное пространство размером 16 МБ или больше в защищенном режиме — см. шлюз A20.

- ^ Также требуется дополнительная запись дескриптора в верхней части таблицы, поскольку таблица начинается с нуля, но минимальный индекс дескриптора, который можно загрузить в регистр сегмента, равен 1; значение 0 зарезервировано для обозначения регистра сегмента, который не указывает ни на один сегмент.

Ссылки

[ редактировать ]- ^ Прайс, Дэйв (11 мая 1989 г.). «32-разрядный процессор 80486 открывает новые горизонты в области плотности кристаллов и производительности. (Intel Corp.) (анонс продукта) EDN» (пресс-релиз).

- ^ Свойер, Стивен (24 апреля 2003 г.). «AMD представляет 64-битный чип Opteron (ESJ) (новостная статья)» .

- ^ Рао, ПВС (2009). Архитектура компьютерной системы . Прентис-Холл Индии. п. 402 (Раздел 19.1, Семейство процессоров x86 ). ISBN 978-81-203-3594-3 .

- ^ Мхатре, Свапнил Чандракант (2012). Микропроцессоры и интерфейсные технологии: для SE (компьютерная инженерия), II семестр Университета Пуны . Издательство Джайко. ISBN 978-81-8495-325-1 .

- ^ Алкорн, Пол (9 февраля 2022 г.). «AMD устанавливает рекорд доли рынка процессоров за всю историю благодаря росту Intel на рынке настольных ПК и ноутбуков» . Аппаратное обеспечение Тома .

- ^ Брэндон, Джонатан (15 апреля 2015 г.). «Облако за пределами x86: как старые архитектуры возвращаются» . ICloud PE . Новости бизнес-облака. Архивировано из оригинала 19 августа 2021 года . Проверено 23 ноября 2020 г.

Несмотря на доминирование x86 в центрах обработки данных, трудно игнорировать шумиху, которую поставщики подняли за последние пару лет вокруг архитектур, отличных от x86, таких как ARM...

- ^ Дворжак, Джон К. «Что случилось с Intel iAPX432?» . Дворжак.org. Архивировано из оригинала 25 ноября 2017 года . Проверено 18 апреля 2014 г.

- ^ Справочник программиста iAPX 286 (PDF) . Интел. 1983. Архивировано (PDF) из оригинала 28 августа 2017 года . Проверено 28 августа 2017 г.

- ^ Перейти обратно: а б Руководство пользователя iAPX 86, 88 (PDF) . Интел. Август 1981 г. Архивировано (PDF) из оригинала 28 августа 2017 г. . Проверено 28 августа 2017 г.

- ^ Эдвардс, Бендж (16 июня 2008 г.). «Рождение стандарта: микропроцессор Intel 8086» . ПКМир . Архивировано из оригинала 26 сентября 2010 года . Проверено 14 сентября 2014 г.

- ^ Стэнли Мазор (январь – март 2010 г.). «Интел 8086». IEEE Анналы истории вычислений . 32 (1): 75–79. дои : 10.1109/MAHC.2010.22 . S2CID 16451604 .

- ^ «AMD раскрывает новые технологии на микропроцессорном форуме» (пресс-релиз). АМД . 5 октября 1999 г. Архивировано из оригинала 2 марта 2000 г.

«Снова и снова архитекторы процессоров смотрели на неэлегантную архитектуру x86 и заявляли, что ее невозможно расширить для соответствия последним инновациям», - сказал Натан Бруквуд, главный аналитик Insight. 64.

- ^ Берт, Джефф (5 апреля 2010 г.). «Microsoft прекращает поддержку Intel Itanium» . электронная неделя . Проверено 2 июня 2022 г.

- ^ Перейти обратно: а б «Справочное руководство по оптимизации архитектур Intel 64 и IA-32» (PDF) . Интел. Сентябрь 2019 г. 3.4.2.2 Оптимизация для макрослияния. Архивировано (PDF) из оригинала 14 февраля 2020 г. Проверено 7 марта 2020 г.

- ^ Перейти обратно: а б Туман, Агнер. «Микроархитектура процессоров Intel, AMD и VIA» (PDF) . п. 107. Архивировано (PDF) из оригинала 22 марта 2019 года . Проверено 7 марта 2020 г.

Core2 может выполнять объединение макроопераций только в 16-битном и 32-битном режиме. Core Nehalem также может делать это в 64-битном режиме.

- ^ «Zet: открытая реализация x86 (IA-32): обзор» . Открытые ядра . 4 ноября 2013 года. Архивировано из оригинала 11 февраля 2018 года . Проверено 5 января 2014 г.

- ^ «Zhaoxin готовит поддержку ядра Linux для процессоров Centaur 7-й серии» . www.phoronix.com . Проверено 5 апреля 2022 г.

- ^ «Zhaoxin планирует выпустить в 2021 году свои 7-нм процессоры x86 - CPU - Новости - HEXUS.net» . m.hexus.net . Проверено 5 апреля 2022 г.

- ^ «Zhaoxin наконец-то добавляет настройку процессора Lujiazui x86_64 в GCC» . www.phoronix.com . Проверено 5 апреля 2022 г.

- ^ «Особенности по настройке и установке компьютеров под управлением Windows x64 Edition» . Архивировано из оригинала 11 сентября 2014 года . Проверено 14 сентября 2014 г.

- ^ «Представление упрощенной архитектуры Intel» . Интел .

- ^ Ларабель, Майкл (20 мая 2023 г.). «Intel публикует спецификацию X86-S только для 64-битной архитектуры» . Фороникс . Проверено 20 мая 2023 г.

- ^ «Процессоры. Какой режим адресации используют процессоры Intel?» . Архивировано из оригинала 11 сентября 2014 года . Проверено 14 сентября 2014 г.

- ^ «DSB-коммутаторы» . Усилитель Intel VTune 2013 . Интел. Архивировано из оригинала 2 декабря 2013 года . Проверено 26 августа 2013 г.

- ^ «Руководство пользователя семейства 8086» (PDF) . Корпорация Интел. Октябрь 1979 г. с. 2-68. Архивировано (PDF) из оригинала 4 апреля 2018 г. Проверено 28 марта 2018 г.

- ^ «Справочное руководство программиста iAPX 286» (PDF) . Корпорация Интел. 1983. 2.4.3 Режимы адресации памяти. Архивировано (PDF) из оригинала 28 августа 2017 г. Проверено 28 августа 2017 г.

- ^ 80386 Справочное руководство программиста (PDF) . Корпорация Интел. 1986. 2.5.3.2 ВЫЧИСЛЕНИЕ ЭФФЕКТИВНОГО АДРЕСА. Архивировано (PDF) из оригинала 28 декабря 2018 г. Проверено 28 марта 2018 г.

- ^ Перейти обратно: а б Руководство разработчика программного обеспечения для архитектур Intel® 64 и IA-32, том 1: Базовая архитектура . Корпорация Интел. Март 2018. Глава 3. Архивировано из оригинала 26 января 2012 года . Проверено 19 марта 2014 г.

- ^ Андрисс, Деннис (2019). «6.5 Влияние настроек компилятора на дизассемблирование». Практический двоичный анализ: создайте свои собственные инструменты Linux для бинарного измерения, анализа и дизассемблирования . Сан-Франциско, Калифорния: ISBN No Starch Press, Inc. 978-1-59327-913-4 . OCLC 1050453850 .

- ^ «Руководство по сборке x86» . Cs.virginia.edu. 11 сентября 2013 г. Архивировано из оригинала 24 марта 2020 г. Проверено 6 февраля 2014 г.

- ^ «FSTSW/FNSTSW — сохранение слова состояния FPU x87» . Архивировано из оригинала 25 января 2022 года . Проверено 15 января 2020 г.

Форма инструкции FNSTSW AX используется в основном при условном ветвлении...

- ^ Руководство разработчика программного обеспечения для архитектур Intel 64 и IA-32, том 1: Базовая архитектура (PDF) . Интел. Март 2013 г. Глава 8. Архивировано (PDF) из оригинала 2 апреля 2013 г. . Проверено 23 апреля 2013 г.

- ^ «Семейство Intel 80287» . CPU-мир . Архивировано из оригинала 9 августа 2016 года . Проверено 21 июля 2016 г.

- ^ Руководство разработчика программного обеспечения для архитектур Intel 64 и IA-32, том 1: Базовая архитектура (PDF) . Интел. Март 2013 г. Глава 9. Архивировано (PDF) из оригинала 2 апреля 2013 г. . Проверено 23 апреля 2013 г.