x86

| Дизайнер | Intel , Amd |

|---|---|

| Биты | 16-битный , 32-битный и 64-битный |

| Введено | 1978 (16-bit), 1985 (32-bit), 2003 (64-bit) |

| Дизайн | Cisc. |

| Тип | Регистр - Мемори |

| Кодирование | Переменная (от 1 до 15 байтов) |

| Разветвление | Код условия |

| Эндианство | Маленький |

| Размер страницы | 8086 - i286 : нет I386 , I486 : 4 КБ страницы P5 Pentium : добавлен 4 МБ страниц (Legacy Pae : 4 кб → 2 МБ) x86-64 : добавлено 1 ГБ страниц |

| Extensions | x87, IA-32, x86-64, X86S, MMX, 3DNow!, SSE, MCA, ACPI, SSE2, NX bit, SMT, SSE3, SSSE3, SSE4, SSE4.2, AES-NI, CLMUL, SM3, SM4, RDRAND, SHA, MPX, SME, SGX, XOP, F16C, ADX, BMI, FMA, AVX, AVX2, AVX-VNNI, AVX512, AVX10, AMX, VT-x, VT-d, AMD-V, AMD-Vi, TSX, ASF, TXT, APX |

| Open | Partly. For some advanced features, x86 may require license from Intel; x86-64 may require an additional license from AMD. The Pentium Pro processor (and NetBurst) has been on the market for more than 21 years[1] and so cannot be subject to patent claims. The i686 subset of the x86 architecture is therefore fully open. The Opteron 1000 series processors have been on the market for more than 21 years, and so cannot be subject to patent claims. The AMD K8 subset of the x86 architecture is therefore fully open.[2] |

| Registers | |

| General-purpose |

|

| Floating point | |

x86 (также известный как 80x86 [ 3 ] или семья 8086 [ 4 ] ) является семейством сложных наборов инструкций компьютер (CISC) набор инструкций архитектуры [ А ] Первоначально разработанный Intel на основе микропроцессора 8086 и его 8-битного внешнего варианта, 8088 . 8086 был введен в 1978 году как полностью 16-битное расширение 8-битного микропроцессора Intel 8080 с сегментацией памяти в качестве решения для решения большей памяти, чем можно охватить простым 16-битным адресом. Термин «x86» возник из -за того, что имена нескольких преемников в процессоре Intel 8086 заканчиваются в «86», включая 80186 , 80286 , 80386 и 80486 . В разговорной речи их имена были «186», «286», «386» и «486».

Термин не является синонимом совместимости ПК IBM , так как это подразумевает множество других компьютерных оборудования . Встроенные системы и компьютеры общего назначения использовали чипы X86 до начала совместимого с ПК , [ B ] Некоторые из них до дебюта IBM PC (1981).

As of June 2022[update], most desktop and laptop computers sold are based on the x86 architecture family,[5] while mobile categories such as smartphones or tablets are dominated by ARM. At the high end, x86 continues to dominate computation-intensive workstation and cloud computing segments.[6]

Overview

[edit]In the 1980s and early 1990s, when the 8088 and 80286 were still in common use, the term x86 usually represented any 8086-compatible CPU. Today, however, x86 usually implies binary compatibility with the 32-bit instruction set of the 80386. This is due to the fact that this instruction set has become something of a lowest common denominator for many modern operating systems and also probably because the term became common after the introduction of the 80386 in 1985.

A few years after the introduction of the 8086 and 8088, Intel added some complexity to its naming scheme and terminology as the "iAPX" of the ambitious but ill-fated Intel iAPX 432 processor was tried on the more successful 8086 family of chips,[c] applied as a kind of system-level prefix. An 8086 system, including coprocessors such as 8087 and 8089, and simpler Intel-specific system chips,[d] was thereby described as an iAPX 86 system.[7][e] There were also terms iRMX (for operating systems), iSBC (for single-board computers), and iSBX (for multimodule boards based on the 8086-architecture), all together under the heading Microsystem 80.[8][9] However, this naming scheme was quite temporary, lasting for a few years during the early 1980s.[f]

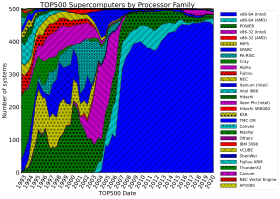

Although the 8086 was primarily developed for embedded systems and small multi-user or single-user computers, largely as a response to the successful 8080-compatible Zilog Z80,[10] the x86 line soon grew in features and processing power. Today, x86 is ubiquitous in both stationary and portable personal computers, and is also used in midrange computers, workstations, servers, and most new supercomputer clusters of the TOP500 list. A large amount of software, including a large list of x86 operating systems are using x86-based hardware.

Modern x86 is relatively uncommon in embedded systems, however, and small low power applications (using tiny batteries), and low-cost microprocessor markets, such as home appliances and toys, lack significant x86 presence.[g] Simple 8- and 16-bit based architectures are common here, as well as simpler RISC architectures like RISC-V, although the x86-compatible VIA C7, VIA Nano, AMD's Geode, Athlon Neo and Intel Atom are examples of 32- and 64-bit designs used in some relatively low-power and low-cost segments.

There have been several attempts, including by Intel, to end the market dominance of the "inelegant" x86 architecture designed directly from the first simple 8-bit microprocessors. Examples of this are the iAPX 432 (a project originally named the Intel 8800[11]), the Intel 960, Intel 860 and the Intel/Hewlett-Packard Itanium architecture. However, the continuous refinement of x86 microarchitectures, circuitry and semiconductor manufacturing would make it hard to replace x86 in many segments. AMD's 64-bit extension of x86 (which Intel eventually responded to with a compatible design)[12] and the scalability of x86 chips in the form of modern multi-core CPUs, is underlining x86 as an example of how continuous refinement of established industry standards can resist the competition from completely new architectures.[13]

Chronology

[edit]This article needs additional citations for verification. (March 2020) |

The table below lists processor models and model series implementing various architectures in the x86 family, in chronological order. Each line item is characterized by significantly improved or commercially successful processor microarchitecture designs.

| Era | Introduction | Prominent CPU models | Address space | Notable features | |||

|---|---|---|---|---|---|---|---|

| Linear | Virtual | Physical | |||||

| x86-16 | 1st | 1978 | Intel 8086, Intel 8088 (1979) | 16-bit | NA | 20-bit | 16-bit ISA, IBM PC (8088), IBM PC/XT (8088) |

| 1982 | Intel 80186, Intel 80188 NEC V20/V30 (1983) |

8086-2 ISA, embedded (80186/80188) | |||||

| 2nd | Intel 80286 and clones | 30-bit | 24-bit | protected mode, IBM PC/XT 286, IBM PC/AT | |||

| IA-32 | 3rd | 1985 | Intel 80386, AMD Am386 (1991) | 32-bit | 46-bit | 32-bit | 32-bit ISA, paging, IBM PS/2 |

| 4th (pipelining, cache) | 1989 | Intel 80486 Cyrix Cx486S, DLC (1992) AMD Am486 (1993), Am5x86 (1995) |

pipelining, on-die x87 FPU (486DX), on-die cache | ||||

| 5th (Superscalar) |

1993 | Intel Pentium, Pentium MMX (1996) | Superscalar, 64-bit databus, faster FPU, MMX (Pentium MMX), APIC, SMP | ||||

| 1994 | NexGen Nx586 AMD 5k86/K5 (1996) |

Discrete microarchitecture (μ-op translation) | |||||

| 1995 | Cyrix Cx5x86 Cyrix 6x86/MX (1997)/MII (1998) |

dynamic execution | |||||

| 6th (PAE, μ-op translation) |

1995 | Intel Pentium Pro | 36-bit (PAE) | μ-op translation, conditional move instructions, dynamic execution, speculative execution, 3-way x86 superscalar, superscalar FPU, PAE, on-chip L2 cache | |||

| 1997 | Intel Pentium II, Pentium III (1999) Celeron (1998), Xeon (1998) |

on-package (Pentium II) or on-die (Celeron) L2 Cache, SSE (Pentium III), Slot 1, Socket 370 or Slot 2 (Xeon) | |||||

| 1997 | AMD K6/K6-2 (1998)/K6-III (1999) | 32-bit | 3DNow!, 3-level cache system (K6-III) | ||||

| Enhanced Platform | 1999 | AMD Athlon Athlon XP/MP (2001) Duron (2000) Sempron (2004) |

36-bit | MMX+, 3DNow!+, double-pumped bus, Slot A or Socket A | |||

| 2000 | Transmeta Crusoe | 32-bit | CMS powered x86 platform processor, VLIW-128 core, on-die memory controller, on-die PCI bridge logic | ||||

| Intel Pentium 4 | 36-bit | SSE2, HTT (Northwood), NetBurst, quad-pumped bus, Trace Cache, Socket 478 | |||||

| 2003 | Intel Pentium M Intel Core (2006) Pentium Dual-Core (2007) |

μ-op fusion, XD bit (Dothan) (Intel Core "Yonah") | |||||

| Transmeta Efficeon | CMS 6.0.4, VLIW-256, NX bit, HT | ||||||

| IA-64 | 64-bit Transition 1999–2005 |

2001 | Intel Itanium (2001–2017) | 52-bit | 64-bit EPIC architecture, 128-bit VLIW instruction bundle, on-die hardware IA-32 H/W enabling x86 OSes & x86 applications (early generations), software IA-32 EL enabling x86 applications (Itanium 2), Itanium register files are remapped to x86 registers | ||

| x86-64 | 64-bit Extended since 2001 |

x86-64 is the 64-bit extended architecture of x86, its Legacy Mode preserves the entire and unaltered x86 architecture. The native architecture of x86-64 processors: residing in the 64-bit Mode, lacks of access mode in segmentation, presenting 64-bit architectural-permit linear address space; an adapted IA-32 architecture residing in the Compatibility Mode alongside 64-bit Mode is provided to support most x86 applications | |||||

| 2003 | Athlon 64/FX/X2 (2005), Opteron Sempron (2004)/X2 (2008) Turion 64 (2005)/X2 (2006) |

40-bit | AMD64 (except some Sempron processors presented as purely x86 processors), on-die memory controller, HyperTransport, on-die dual-core (X2), AMD-V (Athlon 64 Orleans), Socket 754/939/940 or AM2 | ||||

| 2004 | Pentium 4 (Prescott) Celeron D, Pentium D (2005) |

36-bit | EM64T (enabled on selected models of Pentium 4 and Celeron D), SSE3, 2nd gen. NetBurst pipelining, dual-core (on-die: Pentium D 8xx, on-chip: Pentium D 9xx), Intel VT (Pentium 4 6x2), socket LGA 775 | ||||

| 2006 | Intel Core 2 Pentium Dual-Core (2007) Celeron Dual-Core (2008) |

Intel 64 (<<== EM64T), SSSE3 (65 nm), wide dynamic execution, μ-op fusion, macro-op fusion in 16-bit and 32-bit mode,[14][15] on-chip quad-core(Core 2 Quad), Smart Shared L2 Cache (Intel Core 2 "Merom") | |||||

| 2007 | AMD Phenom/II (2008) Athlon II (2009) Turion II (2009) |

48-bit | Monolithic quad-core (X4)/triple-core (X3), SSE4a, Rapid Virtualization Indexing (RVI), HyperTransport 3, AM2+ or AM3 | ||||

| 2008 | Intel Core 2 (45 nm) | 40-bit | SSE4.1 | ||||

| Intel Atom | netbook or low power smart device processor, P54C core reused | ||||||

| Intel Core i7 Core i5 (2009) Core i3 (2010) |

QuickPath, on-chip GMCH (Clarkdale), SSE4.2, Extended Page Tables (EPT) for virtualization, macro-op fusion in 64-bit mode,[14][15] (Intel Xeon "Bloomfield" with Nehalem microarchitecture) | ||||||

| VIA Nano | hardware-based encryption; adaptive power management | ||||||

| 2010 | AMD FX | 48-bit | octa-core, CMT(Clustered Multi-Thread), FMA, OpenCL, AM3+ | ||||

| 2011 | AMD APU A and E Series (Llano) | 40-bit | on-die GPGPU, PCI Express 2.0, Socket FM1 | ||||

| AMD APU C, E and Z Series (Bobcat) | 36-bit | low power smart device APU | |||||

| Intel Core i3, Core i5 and Core i7 (Sandy Bridge/Ivy Bridge) |

Internal Ring connection, decoded μ-op cache, LGA 1155 socket | ||||||

| 2012 | AMD APU A Series (Bulldozer, Trinity and later) | 48-bit | AVX, Bulldozer based APU, Socket FM2 or Socket FM2+ | ||||

| Intel Xeon Phi (Knights Corner) | PCI-E add-on card coprocessor for XEON based system, Manycore Chip, In-order P54C, very wide VPU (512-bit SSE), LRBni instructions (8× 64-bit) | ||||||

| 2013 | AMD Jaguar (Athlon, Sempron) |

SoC, game console and low power smart device processor | |||||

| Intel Silvermont (Atom, Celeron, Pentium) |

36-bit | SoC, low/ultra-low power smart device processor | |||||

| Intel Core i3, Core i5 and Core i7 (Haswell/Broadwell) | 39-bit | AVX2, FMA3, TSX, BMI1, and BMI2 instructions, LGA 1150 socket | |||||

| 2015 | Intel Broadwell-U (Intel Core i3, Core i5, Core i7, Core M, Pentium, Celeron) |

SoC, on-chip Broadwell-U PCH-LP (Multi-chip module) | |||||

| 2015–2020 | Intel Skylake/Kaby Lake/Cannon Lake/Coffee Lake/Rocket Lake (Intel Pentium/Celeron Gold, Core i3, Core i5, Core i7, Core i9) |

46-bit | AVX-512 (restricted to Cannon Lake-U and workstation/server variants of Skylake) | ||||

| 2016 | Intel Xeon Phi (Knights Landing) | 48-bit | Manycore CPU and coprocessor for Xeon systems, Airmont (Atom) based core | ||||

| 2016 | AMD Bristol Ridge (AMD (Pro) A6/A8/A10/A12) |

Integrated FCH on die, SoC, AM4 socket | |||||

| 2017 | AMD Ryzen Series/AMD Epyc Series | AMD's implementation of SMT, on-chip multiple dies | |||||

| 2017 | Zhaoxin WuDaoKou (KX-5000, KH-20000) | Zhaoxin's first brand new x86-64 architecture | |||||

| 2018–2021 | Intel Sunny Cove (Ice Lake-U and Y), Cypress Cove (Rocket Lake) | 57-bit | Intel's first implementation of AVX-512 for the consumer segment. Addition of Vector Neural Network Instructions (VNNI) | ||||

| 2019 | AMD Matisse | 48-bit | Multiple Chip Module design with I/O die separate from CPU die(s), Support for PCIe Gen4 | ||||

| 2020 | Intel Willow Cove (Tiger Lake-Y/U/H) | 57-bit | Dual ring interconnect architecture, updated Gaussian Neural Accelerator (GNA2), new AVX-512 Vector Intersection Instructions, addition of Control-Flow Enforcement Technology (CET) | ||||

| 2021 | Intel Alder Lake | Hybrid design with performance (Golden Cove) and efficiency cores (Gracemont), support for PCIe Gen5 and DDR5, updated Gaussian Neural Accelerator (GNA3). AVX-512 not officially supported | |||||

| 2022 | AMD Vermeer (5800X3D) | 48-bit | X3D chips have an additional 64MB 3D vertically stacked L3 cache (3D V-Cache) for up to 96MB L3 Cache | ||||

| 2022 | AMD Raphael | AMD's first implementation of AVX-512 for the consumer segment, iGPU now standard on Ryzen CPU's with 2 RDNA 2 compute cores | |||||

| Era | Introduction | Prominent CPU models | Address space | Notable features | |||

History

[edit]Designers and manufacturers

[edit]

At various times, companies such as IBM, VIA, NEC,[h] AMD, TI, STM, Fujitsu, OKI, Siemens, Cyrix, Intersil, C&T, NexGen, UMC, and DM&P started to design or manufacture[i] x86 processors (CPUs) intended for personal computers and embedded systems. Other companies that designed or manufactured x86 or x87 processors include ITT Corporation, National Semiconductor, ULSI System Technology, and Weitek.

Such x86 implementations were seldom simple copies but often employed different internal microarchitectures and different solutions at the electronic and physical levels. Quite naturally, early compatible microprocessors were 16-bit, while 32-bit designs were developed much later. For the personal computer market, real quantities started to appear around 1990 with i386 and i486 compatible processors, often named similarly to Intel's original chips.

After the fully pipelined i486, in 1993 Intel introduced the Pentium brand name (which, unlike numbers, could be trademarked) for their new set of superscalar x86 designs. With the x86 naming scheme now legally cleared, other x86 vendors had to choose different names for their x86-compatible products, and initially some chose to continue with variations of the numbering scheme: IBM partnered with Cyrix to produce the 5x86 and then the very efficient 6x86 (M1) and 6x86MX (MII) lines of Cyrix designs, which were the first x86 microprocessors implementing register renaming to enable speculative execution.

AMD meanwhile designed and manufactured the advanced but delayed 5k86 (K5), which, internally, was closely based on AMD's earlier 29K RISC design; similar to NexGen's Nx586, it used a strategy such that dedicated pipeline stages decode x86 instructions into uniform and easily handled micro-operations, a method that has remained the basis for most x86 designs to this day.

Some early versions of these microprocessors had heat dissipation problems. The 6x86 was also affected by a few minor compatibility problems, the Nx586 lacked a floating-point unit (FPU) and (the then crucial) pin-compatibility, while the K5 had somewhat disappointing performance when it was (eventually) introduced.

Customer ignorance of alternatives to the Pentium series further contributed to these designs being comparatively unsuccessful, despite the fact that the K5 had very good Pentium compatibility and the 6x86 was significantly faster than the Pentium on integer code.[j] AMD later managed to grow into a serious contender with the K6 set of processors, which gave way to the very successful Athlon and Opteron.

There were also other contenders, such as Centaur Technology (formerly IDT), Rise Technology, and Transmeta. VIA Technologies' energy efficient C3 and C7 processors, which were designed by the Centaur company, were sold for many years following their release in 2005. Centaur's 2008 design, the VIA Nano, was their first processor with superscalar and speculative execution. It was introduced at about the same time (in 2008) as Intel introduced the Intel Atom, its first "in-order" processor after the P5 Pentium.

Many additions and extensions have been added to the original x86 instruction set over the years, almost consistently with full backward compatibility.[k] The architecture family has been implemented in processors from Intel, Cyrix, AMD, VIA Technologies and many other companies; there are also open implementations, such as the Zet SoC platform (currently inactive).[16] Nevertheless, of those, only Intel, AMD, VIA Technologies, and DM&P Electronics hold x86 architectural licenses, and from these, only the first two actively produce modern 64-bit designs, leading to what has been called a "duopoly" of Intel and AMD in x86 processors.

However, in 2014 the Shanghai-based Chinese company Zhaoxin, a joint venture between a Chinese company and VIA Technologies, began designing VIA based x86 processors for desktops and laptops. The release of its newest "7" family[17] of x86 processors (e.g. KX-7000), which are not quite as fast as AMD or Intel chips but are still state of the art,[18] had been planned for 2021; as of March 2022 the release had not taken place, however.[19]

From 16-bit and 32-bit to 64-bit architecture

[edit]The instruction set architecture has twice been extended to a larger word size. In 1985, Intel released the 32-bit 80386 (later known as i386) which gradually replaced the earlier 16-bit chips in computers (although typically not in embedded systems) during the following years; this extended programming model was originally referred to as the i386 architecture (like its first implementation) but Intel later dubbed it IA-32 when introducing its (unrelated) IA-64 architecture.

In 1999–2003, AMD extended this 32-bit architecture to 64 bits and referred to it as x86-64 in early documents and later as AMD64. Intel soon adopted AMD's architectural extensions under the name IA-32e, later using the name EM64T and finally using Intel 64. Microsoft and Sun Microsystems/Oracle also use term "x64", while many Linux distributions, and the BSDs also use the "amd64" term. Microsoft Windows, for example, designates its 32-bit versions as "x86" and 64-bit versions as "x64", while installation files of 64-bit Windows versions are required to be placed into a directory called "AMD64".[20]

In 2023, Intel proposed a major change to the architecture referred to as X86S (formerly known as X86-S). The S in X86S stands for "simplification", which aims to remove support for legacy execution modes and instructions. A processor implementing this proposal would start execution directly in long mode and would only support 64-bit operating systems. 32-bit code would only be supported for user applications running in ring 3, and would use the same simplified segmentation as long mode.[21][22]

Basic properties of the architecture

[edit]The x86 architecture is a variable instruction length, primarily "CISC" design with emphasis on backward compatibility. The instruction set is not typical CISC, however, but basically an extended version of the simple eight-bit 8008 and 8080 architectures. Byte-addressing is enabled and words are stored in memory with little-endian byte order. Memory access to unaligned addresses is allowed for almost all instructions. The largest native size for integer arithmetic and memory addresses (or offsets) is 16, 32 or 64 bits depending on architecture generation (newer processors include direct support for smaller integers as well). Multiple scalar values can be handled simultaneously via the SIMD unit present in later generations, as described below.[l] Immediate addressing offsets and immediate data may be expressed as 8-bit quantities for the frequently occurring cases or contexts where a −128..127 range is enough. Typical instructions are therefore 2 or 3 bytes in length (although some are much longer, and some are single-byte).

To further conserve encoding space, most registers are expressed in opcodes using three or four bits, the latter via an opcode prefix in 64-bit mode, while at most one operand to an instruction can be a memory location.[m] However, this memory operand may also be the destination (or a combined source and destination), while the other operand, the source, can be either register or immediate. Among other factors, this contributes to a code size that rivals eight-bit machines and enables efficient use of instruction cache memory. The relatively small number of general registers (also inherited from its 8-bit ancestors) has made register-relative addressing (using small immediate offsets) an important method of accessing operands, especially on the stack. Much work has therefore been invested in making such accesses as fast as register accesses—i.e., a one cycle instruction throughput, in most circumstances where the accessed data is available in the top-level cache.

Floating point and SIMD

[edit]A dedicated floating-point processor with 80-bit internal registers, the 8087, was developed for the original 8086. This microprocessor subsequently developed into the extended 80387, and later processors incorporated a backward compatible version of this functionality on the same microprocessor as the main processor. In addition to this, modern x86 designs also contain a SIMD-unit (see SSE below) where instructions can work in parallel on (one or two) 128-bit words, each containing two or four floating-point numbers (each 64 or 32 bits wide respectively), or alternatively, 2, 4, 8 or 16 integers (each 64, 32, 16 or 8 bits wide respectively).

The presence of wide SIMD registers means that existing x86 processors can load or store up to 128 bits of memory data in a single instruction and also perform bitwise operations (although not integer arithmetic[n]) on full 128-bits quantities in parallel. Intel's Sandy Bridge processors added the Advanced Vector Extensions (AVX) instructions, widening the SIMD registers to 256 bits. The Intel Initial Many Core Instructions implemented by the Knights Corner Xeon Phi processors, and the AVX-512 instructions implemented by the Knights Landing Xeon Phi processors and by Skylake-X processors, use 512-bit wide SIMD registers.

Current implementations

[edit]During execution, current x86 processors employ a few extra decoding steps to split most instructions into smaller pieces called micro-operations. These are then handed to a control unit that buffers and schedules them in compliance with x86-semantics so that they can be executed, partly in parallel, by one of several (more or less specialized) execution units. These modern x86 designs are thus pipelined, superscalar, and also capable of out of order and speculative execution (via branch prediction, register renaming, and memory dependence prediction), which means they may execute multiple (partial or complete) x86 instructions simultaneously, and not necessarily in the same order as given in the instruction stream.[23] Some Intel CPUs (Xeon Foster MP, some Pentium 4, and some Nehalem and later Intel Core processors) and AMD CPUs (starting from Zen) are also capable of simultaneous multithreading with two threads per core (Xeon Phi has four threads per core). Some Intel CPUs support transactional memory (TSX).

When introduced, in the mid-1990s, this method was sometimes referred to as a "RISC core" or as "RISC translation", partly for marketing reasons, but also because these micro-operations share some properties with certain types of RISC instructions. However, traditional microcode (used since the 1950s) also inherently shares many of the same properties; the new method differs mainly in that the translation to micro-operations now occurs asynchronously. Not having to synchronize the execution units with the decode steps opens up possibilities for more analysis of the (buffered) code stream, and therefore permits detection of operations that can be performed in parallel, simultaneously feeding more than one execution unit.

The latest processors also do the opposite when appropriate; they combine certain x86 sequences (such as a compare followed by a conditional jump) into a more complex micro-op which fits the execution model better and thus can be executed faster or with fewer machine resources involved.

Another way to try to improve performance is to cache the decoded micro-operations, so the processor can directly access the decoded micro-operations from a special cache, instead of decoding them again. Intel followed this approach with the Execution Trace Cache feature in their NetBurst microarchitecture (for Pentium 4 processors) and later in the Decoded Stream Buffer (for Core-branded processors since Sandy Bridge).[24]

Transmeta used a completely different method in their Crusoe x86 compatible CPUs. They used just-in-time translation to convert x86 instructions to the CPU's native VLIW instruction set. Transmeta argued that their approach allows for more power efficient designs since the CPU can forgo the complicated decode step of more traditional x86 implementations.

Addressing modes

[edit]Addressing modes for 16-bit processor modes can be summarized by the formula:[25][26]

Addressing modes for 32-bit x86 processor modes[27] can be summarized by the formula:[28]

Addressing modes for the 64-bit processor mode can be summarized by the formula:[28]

Instruction relative addressing in 64-bit code (RIP + displacement, where RIP is the instruction pointer register) simplifies the implementation of position-independent code (as used in shared libraries in some operating systems).[29]

The 8086 had 64 KB of eight-bit (or alternatively 32 K-word of 16-bit) I/O space, and a 64 KB (one segment) stack in memory supported by computer hardware. Only words (two bytes) can be pushed to the stack. The stack grows toward numerically lower addresses, with SS:SP pointing to the most recently pushed item. There are 256 interrupts, which can be invoked by both hardware and software. The interrupts can cascade, using the stack to store the return address.

x86 registers

[edit]16-bit

[edit]The original Intel 8086 and 8088 have fourteen 16-bit registers. Four of them (AX, BX, CX, DX) are general-purpose registers (GPRs), although each may have an additional purpose; for example, only CX can be used as a counter with the loop instruction. Each can be accessed as two separate bytes (thus BX's high byte can be accessed as BH and low byte as BL). Two pointer registers have special roles: SP (stack pointer) points to the "top" of the stack, and BP (base pointer) is often used to point at some other place in the stack, typically above the local variables (see frame pointer). The registers SI, DI, BX and BP are address registers, and may also be used for array indexing.

One of four possible 'segment registers' (CS, DS, SS and ES) is used to form a memory address. In the original 8086 / 8088 / 80186 / 80188 every address was built from a segment register and one of the general purpose registers. For example ds:si is the notation for an address formed as [16 * ds + si] to allow 20-bit addressing rather than 16 bits, although this changed in later processors. At that time only certain combinations were supported.

The FLAGS register contains flags such as carry flag, overflow flag and zero flag. Finally, the instruction pointer (IP) points to the next instruction that will be fetched from memory and then executed; this register cannot be directly accessed (read or written) by a program.[30]

The Intel 80186 and 80188 are essentially an upgraded 8086 or 8088 CPU, respectively, with on-chip peripherals added, and they have the same CPU registers as the 8086 and 8088 (in addition to interface registers for the peripherals).

The 8086, 8088, 80186, and 80188 can use an optional floating-point coprocessor, the 8087. The 8087 appears to the programmer as part of the CPU and adds eight 80-bit wide registers, st(0) to st(7), each of which can hold numeric data in one of seven formats: 32-, 64-, or 80-bit floating point, 16-, 32-, or 64-bit (binary) integer, and 80-bit packed decimal integer.[9]: S-6, S-13..S-15 It also has its own 16-bit status register accessible through the fstsw instruction, and it is common to simply use some of its bits for branching by copying it into the normal FLAGS.[31]

In the Intel 80286, to support protected mode, three special registers hold descriptor table addresses (GDTR, LDTR, IDTR), and a fourth task register (TR) is used for task switching. The 80287 is the floating-point coprocessor for the 80286 and has the same registers as the 8087 with the same data formats.

32-bit

[edit]

With the advent of the 32-bit 80386 processor, the 16-bit general-purpose registers, base registers, index registers, instruction pointer, and FLAGS register, but not the segment registers, were expanded to 32 bits. The nomenclature represented this by prefixing an "E" (for "extended") to the register names in x86 assembly language. Thus, the AX register corresponds to the lower 16 bits of the new 32-bit EAX register, SI corresponds to the lower 16 bits of ESI, and so on. The general-purpose registers, base registers, and index registers can all be used as the base in addressing modes, and all of those registers except for the stack pointer can be used as the index in addressing modes.

Two new segment registers (FS and GS) were added. With a greater number of registers, instructions and operands, the machine code format was expanded. To provide backward compatibility, segments with executable code can be marked as containing either 16-bit or 32-bit instructions. Special prefixes allow inclusion of 32-bit instructions in a 16-bit segment or vice versa.

The 80386 had an optional floating-point coprocessor, the 80387; it had eight 80-bit wide registers: st(0) to st(7),[32] like the 8087 and 80287. The 80386 could also use an 80287 coprocessor.[33] With the 80486 and all subsequent x86 models, the floating-point processing unit (FPU) is integrated on-chip.

The Pentium MMX added eight 64-bit MMX integer vector registers (MM0 to MM7, which share lower bits with the 80-bit-wide FPU stack).[34] With the Pentium III, Intel added a 32-bit Streaming SIMD Extensions (SSE) control/status register (MXCSR) and eight 128-bit SSE floating-point registers (XMM0 to XMM7).[35]

64-bit

[edit]Начиная с процессора AMD Opteron , архитектура x86 расширила 32-разрядные регистры на 64-битные регистры, аналогично тому, как имело место расширение на 16-32 бит. R - Prefix (для «регистра») идентифицирует 64-битные регистры (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP) и восемь дополнительных 64-битных общих регистров (R8-R15 ) были также введены в создании X86-64 . Кроме того, были добавлены еще восемь векторных регистров SSE (xmm8 - xmm15). Тем не менее, эти расширения можно использовать только в 64-битном режиме, который является одним из двух режимов, доступных только в длинном режиме . Режимы адресации не были резко изменены с 32-битного режима, за исключением того, что адресация была расширена до 64 бит, виртуальные адреса теперь выровняются на 64 бита (для того, чтобы запретить биты режима в виртуальных адресах), а другие данные селектора были резко уменьшены Полем Кроме того, был добавлен режим адресации, чтобы разрешить ссылки на память относительно RIP ( указатель инструкции ), чтобы облегчить реализацию независимого от положения кода , используется в общих библиотеках в некоторых операционных системах.

128-бит

[ редактировать ]SIMD регистрирует XMM0-XMM15 (xmm0-xmm31, когда AVX-512 поддерживается ).

256-битный

[ редактировать ]SIMD регистрирует YMM0-MMM15 (YMM0-MMM31, когда AVX-512 поддерживается ). Нижняя половина каждой из карт регистров YMM на соответствующем регистре XMM.

512-бит

[ редактировать ]SIMD регистрирует ZMM0 - ZMM31. Нижняя половина каждой из карт ZMM Registers в соответствующем регистре YMM.

Разное/специальное назначение

[ редактировать ]Процессоры x86, которые имеют защищенный режим , то есть 80286 и более поздних процессоров, также имеют три регистра дескрипторов (GDTR, LDTR, IDTR ) и регистр задач (TR).

32-разрядные процессоры x86 (начиная с 80386) также включают различные специальные/разные регистры, такие как контрольные регистры (CR0 до 4, CR8 только для 64-битных), отладки (DR0-3, плюс 6 и 7), регистры тестов. (Только с TR3 до 7; 80486) и регистры специфичных для модели (MSR, появляющиеся с Pentium [ O ] ).

AVX-512 имеет восемь дополнительных 64-битных регистров маски K0-K7 для выбора элементов в векторном регистре. В зависимости от векторного регистра и ширины элементов, только подмножество бит регистра маски может использоваться данной инструкцией.

Цель

[ редактировать ]Хотя основные регистры (за исключением указателя инструкций) являются «общими» в 32-разрядных и 64-битных версиях набора инструкций и могут использоваться для чего-либо, первоначально предполагалось, что они будут использоваться для Следующие цели:

- Al/ah/ax/eax/rax: аккумулятор

- CL/CH/CX/ECX/RCX: счетчик (для использования с петлями и струнами)

- DL/DH/DX/EDX/RDX: расширить точность аккумулятора (например, комбинация 32-битных EAX и EDX для 64-битных целочисленных операций в 32-битном коде)

- BL/BH/BX/EBX/RBX: базовый индекс (для использования с массивами)

- SP/ESP/RSP: указатель стека для верхнего адреса стека.

- BP/EBP/RBP: базовый указатель стека для удержания адреса текущего кадра стека .

- SI/ESI/RSI: Источник индекса для строковых операций.

- DI/EDI/RDI: индекс назначения для операций строк.

- IP/EIP/RIP: указатель инструкции. Удерживает счетчик программы , адрес следующей инструкции.

Регистры сегмента:

- CS: код

- DS: данные

- SS: стек

- Это: дополнительные данные

- FS: дополнительные данные № 2

- GS: дополнительные данные № 3

Никаких конкретных целей не предусмотрено для других 8 регистров, доступных только в 64-битном режиме.

Некоторые инструкции компилируются и выполняют более эффективно при использовании этих регистров для их разработанных целей. Например, использование AL в качестве аккумулятора и добавление немедленного значения байта к нему создает эффективное добавление в al -opcode 04H, в то время как использование регистра BL создает универсальный и более длительный добавление в регистр OpCode 80C3H. Другим примером является двойное точное деление и умножение, которое работает специально с регистрами AX и DX.

Современные компиляторы извлекли выгоду из введения байта SIB ( байт-базой масштаб-индекса ), который позволяет равномерно обрабатывать регистры ( миниакомпьютер -подобные). Тем не менее, использование байта SIB, универсально является неоптимальным, поскольку он производит более длинные кодирования, чем использование его выборочно при необходимости. (Основным преимуществом байта SIB является ортогональность и более мощные режимы адресации, которые он предоставляет, что позволяет сохранить инструкции и использование регистров для расчетов адресов, таких как масштабирование индекса.) Некоторые специальные инструкции потеряли приоритет в дизайне оборудования. и стал медленнее, чем эквивалентные небольшие кодовые последовательности. Примечательным примером является инструкция LODSW.

Структура

[ редактировать ]| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? X | |||||||

| БЫВШИЙ | |||||||

| ? X | |||||||

| ?ЧАС | ? L. | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| ? D. | |||||||

| ?В | |||||||

| ? Б | |||||||

| 16 | 8 |

|---|---|

| ? S | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? P. | |||||||

| Е? | |||||||

| ? P. | |||||||

| ? Пл | |||||||

ПРИМЕЧАНИЕ. Регистры? PL доступны только в 64-битном режиме.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? Я | |||||||

| Е? | |||||||

| ?Я | |||||||

| ? | |||||||

Примечание: регистры? IL доступны только в 64-битном режиме.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| РВАТЬ | |||||||

| Eip | |||||||

| IP | |||||||

Эксплуатационные режимы

[ редактировать ]Реальный режим

[ редактировать ]В этом разделе нужны дополнительные цитаты для проверки . ( Январь 2014 ) |

Режим реального адреса, [ 36 ] Обычно называемый реальным режимом, представляет собой режим работы 8086 и более поздние CPUS-совместимые процессоры . Реальный режим характеризуется 20-битным сегментированным адресным пространством память [ P ] ), прямой доступ к программному обеспечению к периферийному оборудованию, и нет концепции защиты памяти или многозадачности на уровне аппаратного обеспечения. Все процессоры x86 в серии 80286 , а затем запускаются в реальном режиме в Power-On; 80186 ЦП и ранее имели только один эксплуатационный режим, который эквивалентен реальному режиму в более поздних чипах. (На платформе IBM PC прямой доступ к программному обеспечению к процедурам IBM BIOS доступен только в реальном режиме, поскольку BIOS записан для реального режима. Однако это не свойство ЦП x86, а дизайн IBM BIOS.)

Чтобы использовать более 64 КБ памяти, необходимо использовать регистры сегмента. Это создало большие осложнения для исполнителей компиляторов, которые ввели нечетные режимы указателя, такие как «близкий», «далеко» и «огромный», чтобы использовать неявную природу сегментированной архитектуры в разные степени, с некоторыми указателями, содержащими 16-битные смещения внутри подразумеваемых сегментов и других указатели, содержащие адреса сегмента и смещения в сегментах. Технически возможно использовать до 256 КБ памяти для кода и данных, с до 64 КБ для кода, путем установки всех четырех регистров сегмента один раз, а затем только с использованием 16-битных смещений (необязательно с префиксами переопределения по умолчанию), чтобы адресная память, но это накладывает существенные ограничения на то, как можно адресовать данные, а операнды памяти могут быть объединены, и это нарушает архитектурное намерение дизайнеров Intel, которые предназначены для отдельных элементов данных (например, массивы, структуры, кодовые единицы) Содержится в отдельных сегментах и адресованных их собственными адресами сегмента, в новых программах, которые не переносятся из более ранних 8-битных процессоров с 16-битными адресными пространствами.

Нереальный режим

[ редактировать ]Unreal Mode используется около 16-битными операционными системами и несколькими 32-битными загрузчиками .

Режим управления системой

[ редактировать ]Режим управления системой (SMM) используется только системой прошивки ( BIOS / UEFI ), а не программным обеспечением для операционных систем и приложений. Код SMM работает в SMRAM.

Защищенный режим

[ редактировать ]В этом разделе нужны дополнительные цитаты для проверки . ( Январь 2014 ) |

В дополнение к реальному режиму, Intel 80286 поддерживает защищенный режим, расширяя адресуемую физическую память до 16 МБ и адресуемой виртуальной памяти до 1 ГБ и обеспечивая защищенную память , которая не позволяет программам развращать друг друга. Это делается с использованием регистров сегмента только для хранения индекса в таблице дескрипторов, которая хранится в памяти. Существует две такие таблицы: глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT), каждая из которых содержит до 8192 дескрипторов сегмента, каждый из которых дает доступ к 64 т.п.н. памяти. В 80286 дескриптор сегмента предоставляет 24-битный базовый адрес , и этот базовый адрес добавляется в 16-битное смещение для создания абсолютного адреса. Базовый адрес из таблицы выполняет ту же роль, что и буквальное значение регистра сегмента выполняется в реальном режиме; Регистры сегмента были преобразованы из прямых регистров в косвенные регистры. Каждому сегменту можно назначить один из четырех кольцевых уровней, используемых для аппаратной безопасности компьютерной безопасности Полем Каждый дескриптор сегмента также содержит предельное поле сегмента, которое указывает максимальное смещение, которое может использоваться с сегментом. Поскольку смещения составляют 16 бит, сегменты по -прежнему ограничены 64 кб каждая в 80286 защищенном режиме. [ 37 ]

Каждый раз, когда регистр сегмента загружается в защищенном режиме, 80286 должен считывать дескриптор сегмента 6-байтов из памяти в набор скрытых внутренних регистров. Таким образом, регистры сегмента загрузки гораздо медленнее в защищенном режиме, чем в реальном режиме, и следует избегать изменения сегментов. Фактические операции памяти с использованием сегментов защищенного режима не сильно замедляются, потому что 80286, а затем имеют аппаратное обеспечение для проверки смещения по пределу сегмента параллельно с выполнением инструкций.

Intel 80386 расширенные смещения, а также поля ограничения сегмента в каждом дескрипторе сегмента до 32 бит, что позволяет сегменту охватить все пространство памяти. Он также ввел поддержку в защищенном режиме для пейджинга , механизм, позволяющий использовать виртуальную память Page (с размером страницы 4 КБ). Paging позволяет ЦП отображать любую страницу пространства виртуальной памяти на любую страницу пространства физической памяти. Для этого он использует дополнительные таблицы отображения в памяти, называемые таблицами страниц. Защищенный режим на 80386 может работать с Paging или отключенным; Механизм сегментации всегда активен и генерирует виртуальные адреса, которые затем отображаются с помощью механизма пейджинга, если он включен. Механизм сегментации также может быть эффективно отключен, установив все сегменты, чтобы иметь базовый адрес 0, а ограничение размера, равное всему адресу; Это также требует таблицы дескрипторов сегмента минимального размера из четырех дескрипторов (поскольку сегменты FS и GS не должны использоваться). [ Q ]

Пейджинг широко используется современными многозадачными операционными системами. Linux , 386BSD и Windows NT были разработаны для 386, потому что это был первый процессор Intel Architecture, поддерживающий пейджинг и 32-разрядные смещения сегмента. Архитектура 386 стала основой всех дальнейших развития в серии x86.

x86 процессоры, которые поддерживают защищенный режим, в реальном режиме для обратной совместимости со старшим классом процессоров 8086. При включении (ака загрузки ) процессор инициализируется в реальном режиме, а затем начинает выполнять инструкции. Код загрузки операционной системы, который может храниться в памяти только для чтения , может поместить процессор в защищенный режим, чтобы включить пейджинг и другие функции. И наоборот, арифметика сегмента, общая практика в коде реального режима, не допускается в защищенном режиме.

Виртуальный режим 8086

[ редактировать ]В 32-разрядном защищенном режиме также существует подраздел работы (AKA 80386), который называется Virtual 8086 Mode , также известный как режим V86 . Это в основном специальный гибридный режим работы, который позволяет запускать программы реального режима и операционные системы, находясь под управлением операционной системы Spected Mode Supervisor. Это обеспечивает большую гибкость при выполнении программ защищенного режима и программ реального режима одновременно. Этот режим доступен исключительно для 32-битной версии защищенного режима; Он не существует в 16-битной версии защищенного режима или в длинном режиме.

Длинный режим

[ редактировать ]В середине 1990-х годов было очевидно, что 32-разрядное адресное пространство архитектуры X86 ограничивало свою производительность в приложениях, требующих больших наборов данных. 32-разрядное адресное пространство позволит процессору напрямую обращаться только к 4 ГБ данных, размер, превзойденное приложениями, такими как обработка видео и двигатели базы данных . Используя 64-битные адреса, можно напрямую обращаться к 16 EIB данных, хотя большинство 64-битных архитектур не поддерживают доступ к полному 64-разрядному адресному пространству; Например, AMD64 поддерживает только 48 бит по 64-битному адресу, разделяющему на четыре уровня пьесы.

В 1999 году AMD опубликовал (почти) полную спецификацию для 64-битной расширения архитектуры x86, которую они назвали X86-64 с заявленными намерениями для производства. Эта конструкция в настоящее время используется почти во всех процессорах X86, за некоторыми исключениями, предназначенными для встроенных систем .

Четыре года спустя, в 2003 году, в 2003 году, в 2003 году, в 2003 году, в 2003 году, в 2003 году, в 2003 году, проработанные x86-64 , после того, как было потрачено на рабочие прототипы, которые будут испытаны и усовершенствованы; Примерно в то же время начальное имя X86-64 было изменено на AMD64 . Успех линии процессоров AMD64 в сочетании с теплым приемом архитектуры IA-64, вынужденной Intel выпустить свою собственную реализацию набора инструкций AMD64. Intel ранее внедрила поддержку AMD64 [ 38 ] Но решил не включать его в надежде, что AMD не приведет AMD64 на рынок до того, как был широко принят новый набор инструкций IA-64 IANIUM. Он назвал свою реализацию AMD64 как EM64T , а затем переименовал IT Intel 64 .

В своей литературе и названиях версий продукта Microsoft и Sun называют AMD64/Intel 64 в совокупности как x64 в операционных системах Windows и Solaris . Распределения Linux называют его как «x86-64», его вариант «x86_64», либо «AMD64». Системы BSD используют «AMD64», в то время как MacOS использует «x86_64».

Длинный режим в основном является расширением 32-разрядного набора инструкций, но в отличие от перехода с 16–32-битным, многие инструкции были отброшены в 64-битном режиме. Это не влияет на фактическую бинарную обратную совместимость (которая будет выполнять устаревший код в других режимах, которые сохраняют поддержку этих инструкций), но он меняет способ работы ассемблера и компиляторам для нового кода.

Это был первый раз, когда основное расширение архитектуры x86 было инициировано и вызвано производителем, отличным от Intel. Это был также первый раз, когда Intel приняла технологии такого рода из внешнего источника.

Расширения

[ редактировать ]Блок с плавающей запятой

[ редактировать ]Ранние процессоры x86 могут быть расширены с помощью оборудования с плавающей точкой в виде серии численных композиторов с плавающей точкой с такими именами, такими как 8087 , 80287 и 80387, сокращенно x87. Это также было известно как NPX ( числовое расширение процессора ), подходящее имя, так как копроцессоры, в то время как в основном использовались для расчетов с плавающей точкой, также выполняли целочисленные операции как в бинарных, так и в десятичных форматах. За очень немногими исключениями, 80486 и последующие процессоры X86 затем интегрировали эту функцию x87 в чип, что сделало инструкции x87 де -факто интегральной частью набора инструкций x86.

Каждый регистр X87, известный как ST (0) через ST (7), имеет ширину 80 бит и хранит номера в стандартном формате с плавающей точкой IEEE . Эти регистры организованы как стек с ST (0) как верх. Это было сделано для того, чтобы сохранить пространство OpCode, и поэтому регистры являются случайным образом доступны только для любого операнда в инструкции по регистрации на регистрацию; ST0 всегда должен быть одним из двух операндов, либо источником, либо пунктом назначения, независимо от того, является ли другой операнд ST (x) или операндом памяти. Тем не менее, случайный доступ к регистрам стека может быть получен через инструкцию, которая обменивается любым указанным ST (x) с помощью ST (0).

Операции включают арифметические и трансцендентные функции, включая тригонометрические и экспоненциальные функции, и инструкции, которые загружают общие константы (такие как 0; 1; e, основание естественного логарифма; log2 (10); и log10 (2)) в одну из стек регистрируется. Хотя целочисленная способность часто упускается из виду, x87 может работать на более крупных целых числах с одной инструкцией, чем 8086, 80286, 80386 или любой ЦП x86 без 64-битных расширений, и повторные целочисленные расчеты даже по небольшим значениям (например, (например, (например, до 64-битных расшир 16-битный) может быть ускорен, выполняя целочисленные инструкции на процессоре x86 и x87 параллельно. (Процессор x86 продолжает работать, пока он вычисляет копроцессор x87, а x87 устанавливает сигнал на x86, когда он закончен или прерывает x86, если он требует внимания из -за ошибки.)

MMX

[ редактировать ]MMX - это набор инструкций SIMD , разработанный Intel и представленный в 1997 году для микропроцессора Pentium MMX . [ 39 ] Набор инструкций MMX был разработан из аналогичной концепции, впервые использованной в Intel I860 . Он поддерживается на большинстве последующих процессоров IA-32 Intel и другими поставщиками. MMX обычно используется для обработки видео (например, в мультимедийных приложениях). [ 40 ]

MMX добавил 8 новых регистров в архитектуру, известную как MM0 через MM7 (отныне называется MMN ). На самом деле эти новые регистры были просто псевдонимом для существующих регистров стека X87 FPU. Следовательно, все, что было сделано со стеком с плавающей точкой, также повлияет на регистры MMX. В отличие от стека FP, эти регистры MMN были фиксированными, а не относительными, и поэтому они были случайно доступны. Набор инструкций не применил семантику, подобную стеку, так что существующие операционные системы все еще могли правильно сохранить и восстановить состояние регистра при многозадачности без модификаций. [ 39 ]

Каждый из регистров MMN-64-битные целые числа. Однако одной из основных понятий набора инструкций MMX является концепция упакованных типов данных , что означает, что вместо использования всего регистра для одного 64-разрядного целого числа ( четырехворного слова ) можно использовать его для содержания двух 32-битных целых чисел. ( двойное слово ), четыре 16-битных целых числа ( слово ) или восемь 8-битных целых чисел ( байт ). Учитывая, что 64-битные регистры MMN MMX подселены на стеке FPU, и каждый из регистров с плавающей точкой имеет ширину 80 бит, верхние 16 бит регистров с плавающей точкой не используются в MMX. Эти биты устанавливаются на все из них любыми инструкциями MMX, которые соответствуют представлению NAN или бесконечности с плавающей точкой. [ 39 ]

3dnow!

[ редактировать ]В 1997 году AMD представила 3dnow!. [ 41 ] Внедрение этой технологии совпало с ростом 3D- ЦП развлекательных приложений и было разработано для улучшения производительности векторной обработки в графических приложениях. Разработчики 3D видеоигр и 3D -графические поставщики оборудования используют 3DNOW! повысить их производительность в AMD K6 и Athlon . серии процессоров [ 42 ]

3dnow! был разработан, чтобы быть естественной эволюцией MMX от целых чисел до плавающей запятой. Таким образом, он использует точно ту же соглашение о именовании регистра, что и MMX, то есть MM0 - MM7. [ 43 ] Единственное отличие состоит в том, что вместо того, чтобы упаковать целые числа в эти регистры, два числа с плавающей запятой в одной режиме упаковываются в каждый регистр. Преимущество псевдонима регистров FPU состоит в том, что та же самая инструкция и структуры данных, используемые для сохранения состояния регистров FPU, также могут использоваться для сохранения 3DNOW! регистр государства. Таким образом, никаких специальных модификаций не требуется в операционных системах, которые в противном случае не знали бы о них. [ 44 ]

SSE и AVX

[ редактировать ]по потоковой передаче SIMD Extensions (SSE) В 1999 году Intel представила набор инструкций , следующим образом в 2000 году с SSE2. Первое дополнение позволило разгрузить базовые операции с плавающей точкой из стека x87, а второй сделанный MMX почти устарел и позволил реалистично ориентироваться на инструкции обычными компиляторами. Представленная в 2004 году вместе с Prescott пересмотром процессора Pentium 4 , SSE3 добавил конкретные инструкции по памяти и потоку , чтобы повысить производительность технологии гиперподбота Intel . AMD лицензировал набор инструкций SSE3 и внедрил большинство инструкций SSE3 для его процессоров пересмотра E, а затем Athlon 64. Athlon 64 не поддерживает гиперподботку и не имеет тех инструкций SSE3, используемых только для гиперподровки. [ 45 ]

SSE отказался от всех устаревших соединений со стеком FPU. Это также означало, что этот набор инструкций отбросил все устаревшие соединения с предыдущими поколениями наборов инструкций SIMD, таких как MMX. Но это освободило дизайнеров, позволяя им использовать большие регистры, не ограниченные размером регистров FPU. Дизайнеры создали восемь 128-битных регистров с названием XMM0 через XMM7. (В AMD64 число регистров SSE XMM было увеличено с 8 до 16.) Однако недостатком было то, что операционные системы должны были иметь осознание этого нового набора инструкций, чтобы иметь возможность сохранить свои государства регистрации. Таким образом, Intel создал слегка измененную версию защищенного режима, называемую Enhanced Mode, которая позволяет использовать инструкции SSE, тогда как они остаются отключенными в регулярном защищенном режиме. ОС, которая осведомлена о SSE, будет активировать улучшенный режим, тогда как ОС Незапись вступит только в традиционный защищенный режим.

SSE-это набор инструкций SIMD, который работает только на значениях с плавающей точкой, например, 3dnow!. Однако, в отличие от 3dnow! Он разыгрывает все устаревшее соединение со стеком FPU. Потому что он имеет большие регистры, чем 3DNOW!, SSE может упаковать в два раза больше единого точного поплавателя в свои регистры. Первоначальный SSE был ограничен только одной однооперационной числами, такими как 3dnow!. SSE2 также представил возможность упаковывать двойные точные числа, которые 3DNOW! не имел возможности делать, так как двойная точная численность составляет 64-битный размер, что будет полным размером одного 3DNOW! MMN Регистр. При 128 бит регистры SSE XMMN могут упаковать два двойных поплавка в один регистр. Таким образом, SSE2 гораздо более подходит для научных расчетов, чем SSE1 или 3DNOW!, Которые были ограничены только единственной точностью. SSE3 не вводит никаких дополнительных регистров. [ 45 ]

Усовершенствованные векторные расширения (AVX) удвоили размер регистров SSE до 256-битных регистров YMM. Он также ввел схему кодирования VEX для размещения больших регистров, а также несколько инструкций по проницательным элементам. AVX2 не вводил дополнительные регистры, но был примечательным для добавления для маскировки, сбора и инструкций.

AVX-512 имеет еще одно расширение до 32 512-битных регистров ZMM и новой схемы EVEX. В отличие от своих предшественников, показывающих монолитное расширение, он разделен на многие подмножества, которые могут реализовать конкретные модели процессоров.

Расширение физического адреса (PAE)

[ редактировать ]Расширение физического адреса или PAE было впервые добавлено в Intel Pentium Pro , а затем AMD в процессорах Athlon, [ 46 ] Чтобы разрешить адресовать до 64 ГБ оперативной памяти. Без PAE физический ОЗУ в 32-битном защищенном режиме обычно ограничивается 4 ГБ . PAE определяет другую структуру таблицы страниц с более широкими записями таблицы страниц и третьим уровнем таблицы страниц, позволяя дополнительные биты физического адреса. Хотя первоначальные реализации на 32-битных процессорах теоретически поддерживались до 64 ГБ оперативной памяти, ограничения чипсета и другие платформы часто ограничивали то, что на самом деле можно использовать. x86-64 Процессоры определяют структуры таблиц страниц, которые теоретически допускают до 52 бит физического адреса, хотя опять же, чипсет и другие проблемы с платформой (например, количество доступных слотов DIMM и максимальная оперативная память на DIMM) предотвращают такой большой физический адрес пространство, которое будет реализовано. На процессорах x86-64 режим PAE должен быть активным до перехода в длинный режим и должен оставаться активным, в то время как длинный режим активен, поэтому в длинном режиме нет режима «не-PAE». Режим PAE не влияет на ширину линейных или виртуальных адресов.

x86-64

[ редактировать ]В этом разделе нужны дополнительные цитаты для проверки . ( Март 2016 г. ) |

К 2000-м годам 32-разрядные границы процессоров x86 в обращении к памяти были препятствием для их использования в высокопроизводительных вычислительных кластерах и мощных рабочих станциях настольных компьютеров. В возрасте 32-битной x86 конкурировали с гораздо более продвинутыми 64-битными архитектурами RISC, которые могли бы решить гораздо больше памяти. Intel и вся экосистема x86 нуждались в 64-разрядной адресации памяти, если x86 должен был пережить 64-битную эпоху вычислительной эпохи, так как вскоре должны были начать нанести удар по адресу 32-разрядной адресации. Тем не менее, Intel чувствовала, что это было подходящее время, чтобы сделать смелый шаг и использовать переход на 64-битные настольные компьютеры для перехода от архитектуры x86 в целом, эксперимента, который в конечном итоге потерпел неудачу.

В 2001 году Intel попыталась ввести 64-разрядную архитектуру, не являющуюся X86, названную IA-64 в своем процессоре итании , первоначально стремясь к высокоэффективному вычислительному рынку, надеясь, что в конечном итоге он заменит 32-битный x86. [ 47 ] В то время как IA-64 был несовместимы с x86, процессор Itanium действительно предоставил способности эмуляции для перевода инструкций x86 в IA-64, но это настолько сильно повлияло на производительность программ X86, что это было редко, если вообще когда-либо, на самом деле полезно Следует переписать программы x86 для архитектуры IA-64 или их эффективность на итании, будет заказами на величину хуже, чем на истинном процессоре x86. Рынок отклонил процессор Itanium, поскольку он сломался назад и предпочитал продолжать использовать чипы X86, и очень немногие программы были переписаны для IA-64.

AMD решил выбрать еще один путь к 64-битной адресации памяти, следя за тем, чтобы обратная совместимость не пострадала. В апреле 2003 года AMD выпустил первый процессор X86 с 64-разрядными регистрами общего назначения, Opteron , способный решать гораздо более 4 ГБ виртуальной памяти, используя новое расширение x86-64 (также известное как AMD64 или X64). 64-битные расширения в архитектуре x86 были включены только в недавно введенном длинном режиме , поэтому 32-битные и 16-битные приложения и операционные системы могли просто продолжать использовать процессор AMD64 в защищенных или других режимах, даже без малейшей жертвы производительность [ 48 ] и с полной совместимостью обратно к исходным инструкциям 16-битной Intel 8086. [ 49 ] : 13–14 Рынок отреагировал положительно, приняв 64-битные процессоры AMD как для высокопроизводительных приложений, так и для бизнеса или домашних компьютеров.

Видя, что рынок отвергает несовместимый процессор итаниума и Microsoft, поддерживающую AMD64, Intel должна была ответить и внедрить свой собственный процессор X86-64, Prescott Pentium 4, в июле 2004 года. [ 50 ] В результате процессор Itanium с его набором инструкций IA-64 используется редко, а X86, благодаря своему воплощению x86-64, по-прежнему является доминирующей архитектурой ЦП в не внедренных компьютерах.

x86-64 также представила NX-бит , который обеспечивает некоторую защиту от ошибок безопасности, вызванных переполнениями буфера .

В результате 64-разрядного вклада AMD в линию X86 и его последующее принятие Intel 64-разрядные архитектуры RISC перестали быть угрозой для экосистемы X86 и почти исчезли с рынка рабочей станции. X86-64 начал использовать в мощных суперкомпьютерах (в своих воплощениях AMD Opteron и Intel Xeon ), рынке, который ранее был естественной средой обитания для 64-битных конструкций RISC (таких как микропроцессоры IBM Power или процессоры SPARC ). Большой скачок к 64-битным вычислениям и поддержание обратной совместимости с 32-разрядным и 16-битным программным обеспечением позволили архитектуре x86 стать чрезвычайно гибкой платформой сегодня, причем чипы x86 использовались из небольших систем с низкой мощностью (например, сегодня, чипы X86 (например, системы с небольшими мощными (например, x86 чипов (например, системы с низким содержанием мощности (например, чипы X86 (например, системы с низким содержанием мощности (например, чипы x86 (например, x86 чипов использовались из небольших систем с низкой мощностью (например Intel Quark и Intel Atom ) для компьютеров быстрого игрового настольного настольного компьютера (например, Intel Core I7 и AMD FX / Ryzen ) и даже доминируют в крупных суперкомпьютирующих кластерах , эффективно оставляя только 32 -битную и 64-битную архитектуру RISC в качестве конкурента в смартфон и планшет рынок.

Виртуализация

[ редактировать ]До 2005 года архитектурные процессоры X86 не смогли удовлетворить требования Popek и Goldberg - спецификация для виртуализации, созданной в 1974 году Джеральдом Дж. Поуком и Робертом П. Голдбергом . Тем не менее, как проприетарные, так и виртуализационные продукты виртуализации x86 с открытым исходным кодом были разработаны с использованием программной виртуализации . Собственные системы включают Hyper-V , Parallels Workstation , VMware ESX , WMware Workstation , VMware Workstation Player и Windows Virtual PC , в то время как бесплатные и открытые системы включают QEMU , виртуальную машину на основе ядра , VirtualBox и Xen .

Внедрение наборов инструкций AMD-V и Intel VT-X в 2005 году позволило процессорам X86 соответствовать требованиям виртуализации Popek и Goldberg. [ 51 ]

Аэс

[ редактировать ]APX (расширенные расширения производительности)

[ редактировать ]APX (расширенные расширения производительности) являются расширениями, чтобы удвоить количество регистров общего назначения с 16 до 32 и добавляют новые функции для повышения производительности общего назначения. [ 52 ] [ 53 ] [ 54 ] [ 55 ] Эти расширения были названы «поколением» [ 56 ] и «самое большое добавление x86 с 64 бит». [ 57 ] Intel внесла поддержку APX коллекции компилятора GNU (GCC) 14. [ 58 ]

Согласно спецификации архитектуры, [ 59 ] Основными особенностями APX являются:

- 16 дополнительных регистров общего назначения, называемых расширенными GPRS (EGPRS)

- Форматы инструкций с тремя операциями для многих целочисленных инструкций

- Новые условные инструкции для нагрузок, магазинов и сравнений с общими инструкциями, которые не изменяют флаги

- Оптимизированный регистр сэкономить/восстановить операции

- 64-битная абсолютная инструкция прямого прыжка

Расширенные GPR для инструкций общего назначения кодируются с использованием префикса 2-байтового REX2 , в то время как новые инструкции и расширенные операнды для существующих инструкций AVX / AVX2 / AVX-512 кодируются с расширенным префиксом EVEX , который имеет четыре варианта, используемые для различных групп инструкций.

Смотрите также

[ редактировать ]- x86 Язык Ассамблеи

- x86 Списки инструкций

- x86 Сегментация памяти

- Процессор

- Итания

- x86-64

- 680x0 , конкурирующая архитектура в 16 и начале 32 -битных эпох

- PowerPC , конкурирующая архитектура в более поздних 32-битных и 64-битных эпохах

- Микроархитектура

- Список процессоров AMD

- Список процессоров Intel

- Список микроархитектур процессора Intel

- Список ядра микропроцессоров

- Список производителей x86

- Запрос прерывания

- Японский

- Переходное выполнение уязвимости ЦП

- Тик -модель

- Виртуальные устаревшие провода

Примечания

[ редактировать ]- ^ В отличие от микроархитектуры (и конкретной электронной и физической реализации), используемой для конкретной конструкции микропроцессора.

- ^ Compass Compass . Например, ноутбук

- ^ Включая процессоры 8088 , 80186 , 80188 и 80286 .

- ^ Такая система также содержала обычное сочетание стандартных компонентов поддержки серии 7400 , включая мультиплекторы , буферы и логику клея .

- ^ Фактическим значением IAPX была продвинутая архитектура производительности Intel , а иногда и передовая архитектура процессора Intel .

- ^ с конца 1981 года по начало 1984 года, приблизительно

- ^ Встроенный рынок процессоров заполняется более чем 25 различными архитектурами , которые из -за чувствительности к цене, низкой мощности и требований простоты аппаратного обеспечения превосходят по численности x86.

- ^ NEC V20 и V30 также предоставили более старый набор инструкций 8080, позволяя ПК, оснащенным этими микропроцессорами для работы приложения CP/M на полной скорости (т.е. без необходимости моделирования программного обеспечения 8080).

- ^ Fabless Companies спроектировали чип и заключили контракт на другую компанию на его производство, в то время как Fabbed Companies будут делать как дизайн, так и производство самостоятельно. Некоторые компании начинали как производители Fabbed, а затем стали Fabless Designers, одним из таких примеров является AMD.

- ^ Однако у него был более медленный FPU, что немного иронично, так как Cyrix начинала как дизайнер быстрого плавучих подразделений для процессоров x86.

- ^ Intel отказалась от своей схемы именования «x86» с P5 Pentium в течение 1993 года (поскольку цифры не могут быть торговые марки). Тем не менее, термин X86 уже был установлен среди техников, писателей компиляторов и т. Д.

- ^ 16-битные и 32-битные микропроцессоры были введены в течение 1978 и 1985 годов соответственно; Планы на 64 бит были объявлены в течение 1999 года и постепенно представлены с 2003 года и далее.

- ^ Некоторые конструкции "CISC", такие как PDP-11 , могут использовать два.

- ^ Это потому, что целочисленная арифметика генерирует перенос между последующими битами (в отличие от простых бить).

- ^ Двумя MSR, представляющими особый интерес, - это sysenter_eip_msr и sysenter_esp_msr, введенные в процессоре Pentium® II, который хранит адрес службы службы системы режима ядра и соответствующий указатель стека ядра. Инициализируются во время запуска системы, sysenter_eip_msr и sysenter_esp_msr используются инструкциями Sysenter (Intel) или Syscall (AMD) для достижения быстрых системных вызовов, примерно в три раза быстрее, чем метод прерывания программного обеспечения, используемый ранее.

- ^ Поскольку сегментированный адрес представляет собой сумму 16-битного сегмента, умноженного на 16 и 16-битное смещение, максимальный адрес составляет 114,095 (10ffef Hex), для адресации 114,096 байтов = 1 МБ + 65 520 байтов. Перед 80286 процессорами x86 имели только 20 физических адресных линий (сигналы адресов адреса), поэтому 21 -й бит адреса, бит 20, был отброшен, а адреса прошли 1 МБ были зеркалами нижнего конца адресного пространства (начиная с адреса. ноль). С момента 80286 все процессоры x86 имеют не менее 24 физических адресов, а бит 20 вычисленного адреса выдвигается на адресную шину в реальном режиме, что позволяет ЦП обратиться к полным 1114 096 байтам, достижимым с помощью сегментированного адреса x86. На популярной платформе IBM ПК переключаемое аппаратное обеспечение для отключения 21-го адреса было добавлено в машины с 80286 или позже, чтобы все программы, разработанные для моделей на базе 8088/8086 Память в реальном режиме и полное адресное пространство 16 МБ или большее количество в защищенном режиме - см. A20 Gate.

- ^ Также требуется дополнительная запись дескриптора в верхней части таблицы, поскольку таблица начинается с нуля, но минимальный индекс дескриптора, который может быть загружен в регистр сегмента, составляет 1; Значение 0 зарезервировано для представления регистра сегмента, который указывает на сегмент.

Ссылки

[ редактировать ]- ^ Прис, Дэйв (11 мая 1989 г.). «80486 32-битный процессор разрывает новое основание в плотности чипов и операционной производительности. (Intel Corp.) (Объявление продукта) EDN» (пресс-релиз).

- ^ Swoyer, Стивен (24 апреля 2003 г.). «AMD представляет 64-битный чип Opteron (ESJ) (новостная статья)» .

- ^ Рао, PVS (2009). Архитектура компьютерной системы . Прентис-Холл Индии. п. 402 (раздел 19.1, семейство процессоров x86 ). ISBN 978-81-203-3594-3 .

- ^ Mhatre, Swapneel Chandrakant (2012). Микропроцессоры и методы взаимодействия: для SE (Computer Engineering) Semester II Университета Пуны . Jaico Publishing House. ISBN 978-81-8495-325-1 .

- ^ Alcorn, Paul (9 февраля 2022 г.). «AMD устанавливает рекорд доли рынка процессоров за все время, поскольку Intel прирост на настольных и ноутбуке» . Аппаратное обеспечение Тома .

- ^ Брэндон, Джонатан (15 апреля 2015 г.). «Облако за пределами x86: сколько лет архитектуры возвращается» . Icloud PE . Business Cloud News. Архивировано из оригинала 19 августа 2021 года . Получено 23 ноября 2020 года .

Несмотря на доминирование X86 в центре обработки данных, трудно игнорировать поставщики шума за последние пару лет вокруг архитектур, не являющихся x86, такими как ARM ...

- ^ Дворак, Джон С. "Что случилось с Intel iapx432?" Полем Dvorak.org. Архивировано с оригинала 25 ноября 2017 года . Получено 18 апреля 2014 года .

- ^ IAPX 286 Ссылка программиста (PDF) . Intel. 1983. Архивировал (PDF) из оригинала 28 августа 2017 года . Получено 28 августа 2017 года .

- ^ Jump up to: а беременный IAPX 86, 88 Руководство пользователя (PDF) . Intel. Август 1981 года. Архивировал (PDF) из оригинала 28 августа 2017 года . Получено 28 августа 2017 года .

- ^ Эдвардс, Бендж (16 июня 2008 г.). «Рождение стандарта: микропроцессор Intel 8086» . PCWorld . Архивировано с оригинала 26 сентября 2010 года . Получено 14 сентября 2014 года .

- ^ Стэнли Мазор (январь -март 2010 г.). "Intel's 8086". IEEE ANNALS ИСТОРИЯ ИСКУССТВА . 32 (1): 75–79. doi : 10.1109/mahc.2010.22 . S2CID 16451604 .

- ^ «AMD раскрывает новые технологии на Microprocessor Forum» (пресс -релиз). Амд . 5 октября 1999 года. Архивировано с оригинала 2 марта 2000 года.

«Снова и снова процессорные архитекторы смотрели на неэлегантную архитектуру X86 и заявили, что нельзя растянуть, чтобы приспособить последние инновации», - сказал Натан Бруквуд, главный аналитик Insight 64

- ^ Берт, Джефф (5 апреля 2010 г.). «Microsoft, чтобы закончить поддержку Intel Itanium» . eweek . Получено 2 июня 2022 года .

- ^ Jump up to: а беременный «Intel 64 и IA-32 Архитектурных справочных руководств» (PDF) . Intel. Сентябрь 2019. 3.4.2.2 Оптимизация для макро-слияния. Архивировано (PDF) из оригинала 14 февраля 2020 года . Получено 7 марта 2020 года .

- ^ Jump up to: а беременный Туман, Агнер. «Микроархитектура Intel, AMD и через процессоров» (PDF) . п. 107. Архивировал (PDF) из оригинала 22 марта 2019 года . Получено 7 марта 2020 года .

Core2 может выполнять слияние макроопта только в 16-битном и 32-битном режиме. Core Nehalem также может сделать это в 64-битном режиме.

- ^ «Zet: x86 (IA-32) открытая реализация: обзор» . Opencores . 4 ноября 2013 года. Архивировано с оригинала 11 февраля 2018 года . Получено 5 января 2014 года .

- ^ «Чжаоксин, готовясь к поддержке ядра Linux для процессоров Centaur 7-серии» . www.phoronix.com . Получено 5 апреля 2022 года .

- ^ «Zhaoxin, стремясь к выпуску 2021 года для своих процессоров 7NM x86 - CPU - News - hexus.net» . M.Hexus.net . Получено 5 апреля 2022 года .

- ^ «Чжаоксин, наконец, добавил« lujiazui »x86_64 настройки процессора в GCC» . www.phoronix.com . Получено 5 апреля 2022 года .

- ^ «Соображения установки и установки для компьютеров Windows X64 издания» . Архивировано из оригинала 11 сентября 2014 года . Получено 14 сентября 2014 года .

- ^ «Представляя упрощенную архитектуру Intel» . Intel .

- ^ Ларабель, Майкл (20 мая 2023 г.). «Intel публикует" x86-S "спецификация для 64-битной архитектуры» . Phoronix . Получено 20 мая 2023 года .

- ^ «Процессоры - какой режим решения использует процессоры Intel?» Полем Архивировано из оригинала 11 сентября 2014 года . Получено 14 сентября 2014 года .

- ^ «DSB переключатели» . Intel Vtune усилитель 2013 . Intel. Архивировано из оригинала 2 декабря 2013 года . Получено 26 августа 2013 года .

- ^ «Руководство для пользователя семьи 8086» (PDF) . Intel Corporation. Октябрь 1979 г. с. 2-68. Архивировано (PDF) из оригинала 4 апреля 2018 года . Получено 28 марта 2018 года .

- ^ «IAPX 286 Справочное руководство по программисту» (PDF) . Intel Corporation. 1983. 2.4.3 Режимы адресации памяти. Архивировано (PDF) из оригинала 28 августа 2017 года . Получено 28 августа 2017 года .

- ^ Справочное руководство по программисту 80386 (PDF) . Intel Corporation. 1986. 2.5.3.2 Вычисление эффективного ададресса. Архивировано (PDF) из оригинала 28 декабря 2018 года . Получено 28 марта 2018 года .

- ^ Jump up to: а беременный Руководство по программному обеспечению программного обеспечения Intel® 64 и IA-32, том 1: Основная архитектура . Intel Corporation. Март 2018 года. Глава 3. Архивировано из оригинала 26 января 2012 года . Получено 19 марта 2014 года .

- ^ Andriesse, Dennis (2019). «6.5 Влияние настроек компилятора на разборку». Практический бинарный анализ: создайте свои собственные инструменты Linux для бинарных инструментов, анализа и разборки . Сан -Франциско, Калифорния: No Starch Press, Inc. ISBN 978-1-59327-913-4 Полем OCLC 1050453850 .

- ^ «Руководство по x86 сборке» . Cs.virginia.edu. 11 сентября 2013 года. Архивировано с оригинала 24 марта 2020 года . Получено 6 февраля 2014 года .

- ^ «FSTSW/FNSTSW - хранить x87 Статус FPU Слово статуса» . Архивировано из оригинала 25 января 2022 года . Получено 15 января 2020 года .

Форма топора обучения Fnstsw используется в основном в условном ветвлении ...

- ^ Intel 64 и IA-32 Architectures Software's Developer Руководство по томе 1: Основная архитектура (PDF) . Intel. Март 2013 г. Глава 8. Архивировал (PDF) из оригинала 2 апреля 2013 года . Получено 23 апреля 2013 года .

- ^ "Intel 80287 Семья" . ЦП-мир . Архивировано с оригинала 9 августа 2016 года . Получено 21 июля 2016 года .

- ^ Intel 64 и IA-32 Architectures Software's Developer Руководство по томе 1: Основная архитектура (PDF) . Intel. Март 2013 г. Глава 9. Архивировал (PDF) из оригинала 2 апреля 2013 года . Получено 23 апреля 2013 года .

- ^ Intel 64 и IA-32 Architectures Software's Developer Руководство по томе 1: Основная архитектура (PDF) . Intel. Март 2013 г. Глава 10. Архивировал (PDF) из оригинала 2 апреля 2013 года . Получено 23 апреля 2013 года .

- ^ IAPX 286 Ссылка программиста (PDF) . Intel. 1983. Раздел 1.2, «Режимы работы». Архивировано (PDF) из оригинала 28 августа 2017 года . Получено 27 января 2014 года .

- ^ IAPX 286 Ссылка программиста (PDF) . Intel. 1983. Глава 6, «Управление памятью и виртуальная адресация». Архивировано (PDF) из оригинала 28 августа 2017 года . Получено 27 января 2014 года .

- ^ «Интэль Yamhill Technology: x86-64 Совместима | geek.com» . Архивировано из оригинала 5 сентября 2012 года . Получено 18 июля 2008 года .

- ^ Jump up to: а беременный в «Программирование с помощью технологии Intel MMX ™» . Встроенный Pentium® Family Family Information Center . Intel. Архивировано из оригинала 25 июля 2003 года . Получено 5 июня 2022 года .

- ^ Кришнапрасад, С. (1 января 2004 г.). «Программирование SIMD иллюстрировано с использованием набора инструкций Intel MMX» . Журнал компьютерных наук в колледжах . 19 (3): 268–277. ISSN 1937-4771 .

- ^ Секстон, Майкл Джастин Аллен (21 апреля 2017 г.). «История процессоров AMD» . Аппаратное обеспечение Тома . Получено 5 июня 2022 года .

- ^ Шиппи, Ананд Лал (29 октября 1998 г.). «AMD K6-2 350: что-то делать ...» Анандтех . Получено 5 июня 2022 года .

- ^ «MMX Intel и 3dnow ! web.mit.edu . Получено 5 июня 2022 года .

- ^ «3dnow! ™ Technology Manual» (PDF) . Усовершенствованные микро -устройства . Получено 5 июня 2022 года .

- ^ Jump up to: а беременный «Обновление и ремонт ПК 21 -е издание: функции процессора» . Аппаратное обеспечение Тома . 31 октября 2013 г. Получено 5 июня 2022 года .

- ^ Amd, Inc. (февраль 2002 г.). «Приложение E» (PDF) . AMD ATHLON ™ Процессор X86 Руководство по оптимизации кода (Revision K Ed.). п. 250. Архивировал (PDF) из оригинала 13 апреля 2017 года . Получено 13 апреля 2017 года .

2-битный индекс, состоящий из битов PCD и PWT в записи таблицы страниц, используется для выбора одного из четырех полей PAT Register, когда включена PAE (расширения адреса страницы) или когда PDE не описывает большую страницу.

- ^ Манек Дубаш (20 июля 2006 г.). "Покинет ли Intel итания?" Полем Techworld . Архивировано из оригинала 19 февраля 2011 года . Получено 19 декабря 2010 года .

После рекламы Intel в качестве замены для линейки продуктов x86, ожидания в отношении итания были хорошо задушены назад.

- ^ «IBM Websphere Application Server 64-битный демистифицирован» (PDF) . IBM Corporation. 6 сентября 2007 г. с. 14. Архивировано (PDF) из оригинала 25 января 2022 года . Получено 9 апреля 2010 года .

На рисунках 5, 6 и 7 также показаны 32-разрядные версии приложений «Запустить» на полных нативных аппаратных характеристиках на платформах Power и X86-64. В отличие от некоторых 64-битных архитектур процессоров, аппаратное обеспечение Power и X86-64 не эмулирует 32-битный режим. Поэтому приложения, которые не получают выгоды от 64-битных функций, могут работать с полной производительностью на 32-разрядной версии WebSphere, работающей на вышеупомянутых 64-битных платформах.

- ^ «Том 2: системное программирование» (PDF) . Руководство по программисту AMD64 . AMD Corporation. Март 2024 г. Архивировал (PDF) с оригинала 4 апреля 2024 года . Получено 24 апреля 2024 года .

- ^ Чарли Демерцзян (26 сентября 2003 г.). «Почему Prescott Intel будет использовать расширения AMD64» . Inquirer . Архивировано из оригинала 10 октября 2009 года . Получено 7 октября 2009 г.